# DESIGN AND CONSTRUCTION OF A VIDEO LINE SELECTOR

By YUSUF ISIYAKU 2006/24435EE

ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT

· `` .

.`

NOVEMBER, 2011

# **VIDEO LINE SELECTOR**

By YUSUF ISIYAKU 2006/24435EE

A Thesis submitted to the department of electrical and computer engineering, federal university of technology. Minna, Niger State.

November, 2011

## DEDICATION

This project work is dedicated to my beloved sister Mrs. Saadatu Madonna Ogunbiyi.

## DECLEARATION

I Yusuf Isiyaku, declares that this work was done by me and has never been presented elsewhere for the award of a degree. I also hereby, relinquish the copy right to the federal university of technology, Minna.

USu

Name of Student

11/2011 03

Signature and Date

Yaw Abroham-Attah

Name of Supervisor

11/2011

Signature and Date

6. KAJ

Name of H.O.D

March 15,2012)

**Signature and Date**

Name of External examiner

**Signature and Date**

## ACKNOWLEDGEMENT

My sincere gratitude goes to my supervisor, Mr. Paul Abraham Attah for his time and guidance to me throughout my project. Thank you sir, for your patience and understanding even at times we seemed unserious. May God in his infinite mercies grant you all your heart desires.

My profound appreciation goes to my H.O.D, Engr. A. G. Raji and the entire staff of the department of electrical and computer engineering department who in one way or the other contributed to the success of this project.

I also thank my parents, Late Mr. J. S. Yusufu and Mrs. Maryam Yusufu, my siblings, Skam, Ani Zee, T.Y, Coach, Pash and Jimmy bones for their contributions both financially and morally.

I thank alsoDr. and Mrs. A. D. Tswanya and family for their boundless contribution to the success of this project.

My unending gratitude to my friends, Don Chaisun, Mayowa, Peter, Abraham, the entire class of electrical, 2011. I love you all.

Most of all, I appreciate God almighty for the grace and life he has given to me throughout the project.

## ABSTRACT

Measurements on video signals have been normally difficult. This piece of work is all about the design and construction of a video line selector that selector basically decompose a video signal and extract timing information from a video signal, then it sends a trigger signal to an oscilloscope at the start of that particular line selected by the user. The line selector does not perform measurements on signal, the oscilloscope does that, it only tells the oscilloscope when to start measurement and when to stop based on the timing information of that video.

For accuracy, the same video signal fed to the line selector is also fed to the oscilloscope. The signal appears at the oscilloscope terminal but is not displayed until a trigger signal is received.

## LIST OF FIGURES

| Figure 2.0 Scan Line Pattern on a TV screen4       |

|----------------------------------------------------|

| Figure 2.1 Structure of a Video Signal             |

| Figure 3.0 Video Line Selector Block Diagram10     |

| Figure 3.1 Power Supply Unit10                     |

| Figure 3.2 Bridge Rectifier                        |

| Figure 3.3 Pin Configuration of a 7805 Regulator14 |

| Figure 3.4 LM1881N Pin Configuration15             |

| Figure 3.5 AT89C54 Pin Configuration18             |

| Figure 3.6 Schematic of a HD4478OU LCD21           |

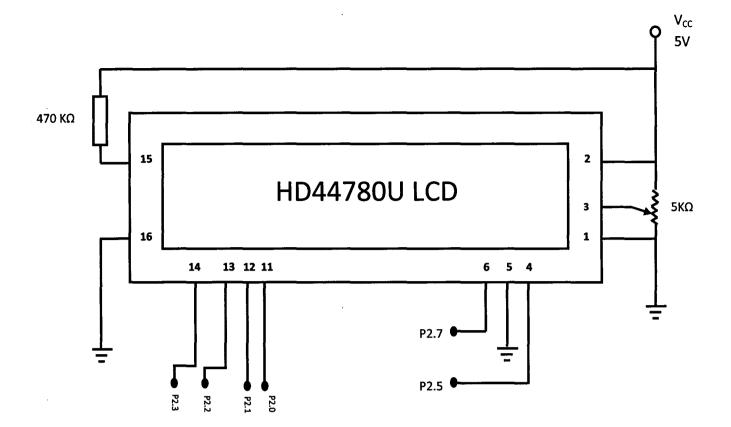

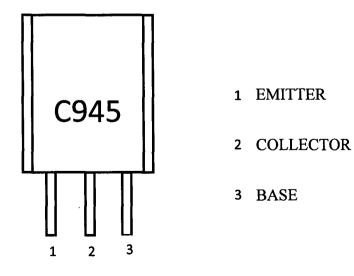

| Figure 3.7 C945(NPN) Transistor21                  |

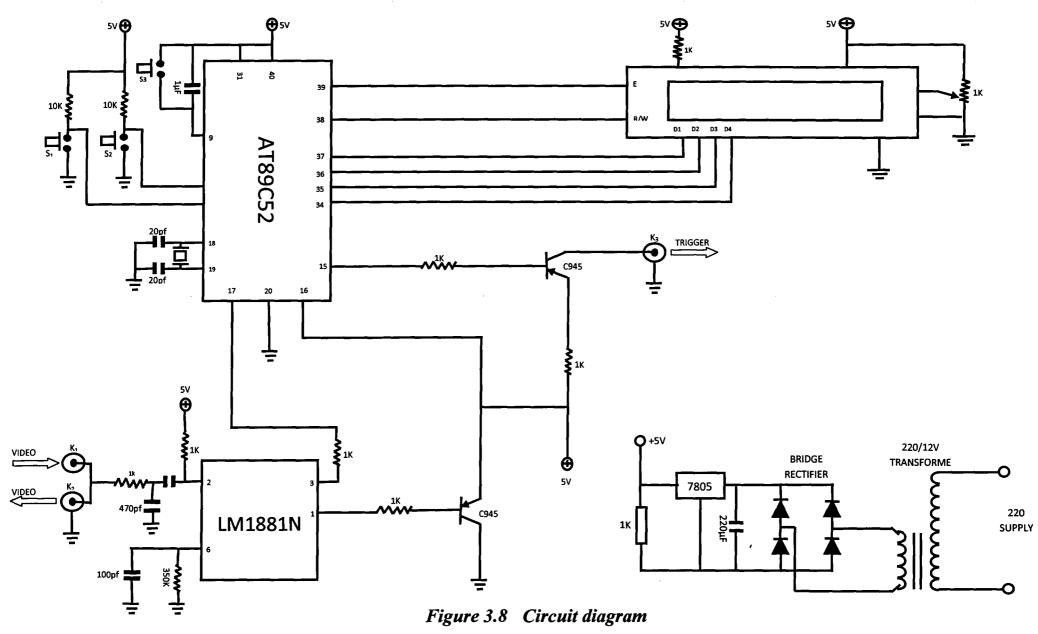

| Figure 3.8 Circuit Diagram23                       |

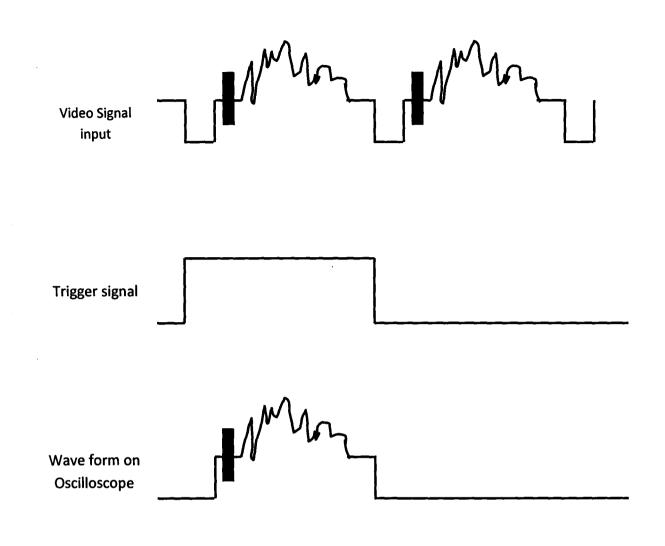

| Figure 4.0 Results                                 |

## TABLE OF CONTENT

| Dedication       | ii  |

|------------------|-----|

| Declaration      | iii |

| Acknowledgement  | iv  |

| Abstract         | v   |

| List of Figures  | vi  |

| Table of Content | vii |

## Chapter One

| 1.0 Introduction           | 1 |

|----------------------------|---|

| 1.1 Aims and Objectives    | 1 |

| 1.2 Methodology            | 2 |

| 1.3 Merits and Limitations | 2 |

## Chapter Two

| 2.0 | Literature | review. | <br> | <br> | <br> | <br> | <br> | .3 |

|-----|------------|---------|------|------|------|------|------|----|

| 2.0 | Literature |         | <br> | <br> | <br> | <br> | <br> | •  |

| 2.1 Brief History of Video Signal |        |

|-----------------------------------|--------|

| 2.2 About Video Signal            |        |

| 2.3 Video Standards and Formats   | ;<br>; |

| 2.3.1 Composite Video6            | i      |

| 2.3.2 S Video6                    |        |

| 2.3.3 Component Video7            | ,      |

| 2.4 Structure of a Video Signal7  |        |

## Chapter Three

| 3.0 Design Analysis          | 9  |

|------------------------------|----|

| 3.1 Power Unit               | 10 |

| 3.1.1 Transformer            | 10 |

| 3.1.2 The Bridge Rectifier   | 11 |

| 3.1.3 The regulator          | 13 |

| 3.2 The Synch Separator Unit | 14 |

| 3.3 The Microcontroller Unit | 15 |

| 3.4 The Display Unit         | 18 |

| 3.4.1 Signal to the Display18                |

|----------------------------------------------|

| 3.4.2 Writing and Reading from the Display19 |

| 3.5 Trigger Unit20                           |

| 3.6 Principle of Operation21                 |

## Chapter Four

| 4.0 Test, Results and Discussion | 23 |

|----------------------------------|----|

| 4.1 Tests                        | 23 |

| 4.1.1 Hardware Test              | 23 |

| 4.1.2 Software Test              | 24 |

| 4.2 Circuit testing              | 24 |

| 4.3 Results                      | 24 |

## Chapter Five

| 5.0 Conclusion and Recommendation | 26 |

|-----------------------------------|----|

| 5.1 Conclusion                    | 26 |

| 5.2 Problems Encountered          | 26 |

## **CHAPTER ONE**

#### **1.0 INTRODUCTION**

It is sometime required to take measurements on video signals for the purpose of repairs, analysis or adjustments on video equipments. For the purpose of that, a video line selector could come in handy particularly when measurements are to be carried out on specific line of a video signal.

This project is all about the design and construction of a video line selector. The circuit's main purpose is to select a particular line of picture from a composite video signal that will be measured or displayed on an oscilloscope.

## 1.1 AIMS AND OBJECTIVES

The project is aimed at designing and constructing a line selector that selects a line of video signal from a composite signal source. Other aims/objectives are

- to decompose a video signal into its separate components

- identifying defects in video signals which can be caused by noise

- to illustrate the wave form of a video signal

#### **1.2 METHODOLOGY**

The project was started by first having a good and comprehensive idea of the whole thing, that is, what the circuit is to do. Then, relevant materials about it were gathered for better comprehension and construction purposes. A circuit diagram was drawn as simple as possible to avoid complexity; also care was taken in the design so as to make sure components chosen are available. The circuit was then laid out and tested on bread board. Finally, the circuit was soldered on Vero-board.

## **1.3 MERITS AND LIMITATIONS**

For a well founded verdict on the operation of a TV set, it is often required to perform measurement on individual lines in the video signal as processed by the set. For this purpose, a number of special test signals (insertion test signals, ITS's) are included in nearly every TV broadcast [1]. The line selector is a handy and multifunctional tool for repairing and adjusting TV sets and other video equipment such as video recorders. The line selector can also be used in video recorders to assign memory location to signal or lines. It also can come handy in extracting information from video signal. In some coded broadcasts, the decoding information is transmitted along the video signal; the line selector can extract this decoding information for the decoder which will be used to decode the video.

## **CHAPTER TWO**

#### 2.0 LITERATURE REVIEW

### 2.1 BRIEF HISTORY OF VIDEO SIGNAL

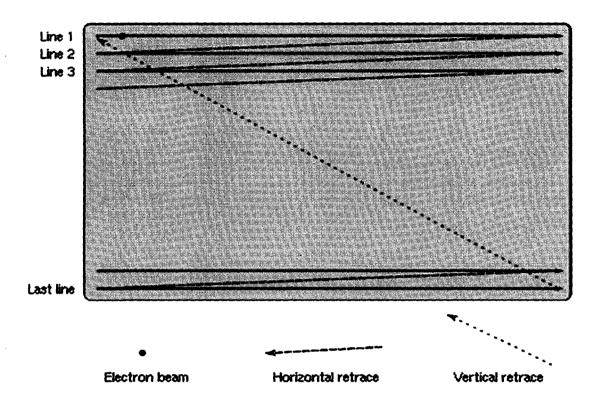

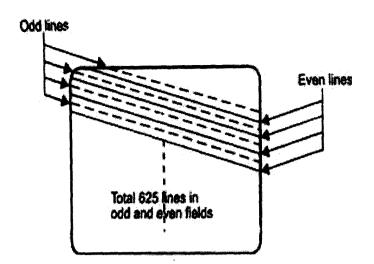

The earliest mechanical television systems used spinning disks with patterns of holes punched into the disc to "scan" an image. A similar disk reconstructed the image at the receiver. Synchronization of the receiver disc rotation was handled through sync pulses broadcast with the image information. However these mechanical systems were slow, the images were dim and flickered severely, and the image resolution very low. Analog television did not really begin as an industry until the development of the cathode-ray tube, which uses a steered electron beam to "write" lines of electrons across a phosphor coated surface [2] as illustrated in the figure 1.0

Figure 2.0 Scan line pattern on a TV screen

The electron beam could be swept across the screen much faster than any mechanical disc system, allowing for more closely spaced scan lines and much higher image resolution, while slow-fade phosphors removed image flicker effects. [2]

## 2.2 ABOUT VIDEO SIGNAL

Broadcasters using analog television systems encode their signal using NTSC, PAL or SECAM analog encoding and then modulate this signal onto a VHF or UHF carrier [2]. Each frame of a television image is composed of lines drawn on the screen. The lines are of varying brightness. The next sequential frame is displayed, allowing the depiction of motion. The analog television signal contains timing and synchronization information so that the receiver can reconstruct a two-dimensional moving image from a one-dimensional time-varying signal. The first commercial analog television systems were monochrome; they were enhanced to include color beginning in the 1950s.[3]

A practical television system needs to take luminance, chrominance (in a color system), synchronization (horizontal and vertical), and audio signals, and broadcast them over a radio transmission.

Analog broadcast television systems come in a variety of frame rates and resolutions. Further differences exist in the frequency and modulation of the audio carrier. When color television was introduced, the hue and saturation information was added to the monochrome signals in a way that black & white televisions ignore. This way backwards compatibility was achieved. That concept is true for all analog television standards.

However there are three standards for the way the additional color information can be encoded and transmitted. The first was the American NTSC (National Television Systems Committee) color television system. The European/Australian PAL (Phase Alternation Line rate) and the French-Former Soviet Union SECAM (Séquentiel Couleur Avec Mémoire) standard were developed later in an attempt to cure certain defects of the NTSC system. PAL's color encoding is similar to the NTSC systems. SECAM uses a different modulation approach than PAL or NTSC.

In principle all three color encoding systems can be combined with any scan line/frame rate combination. Therefore, in order to describe a given signal completely, it's

5

necessary to quote the color system and the broadcast standard as capital letter. For example the United States uses NTSC-M, the UK uses PAL-I, France uses SECAM-L, much of Western Europe and Australia uses PAL-B/G, most of Eastern Europe uses PAL-D/K or SECAM-D/K and so on.[4]

## 2.3 VIDEO STANDARD AND FORMATS

#### 2.3.1 Composite Video

This type of video is passed from one piece of equipment to another using a single coaxial or shielded cable, fitted with the familiar RCA or phono plugs (often color coded yellow). As the name suggests, composite video has all of the signal components needed to produce a TV image, combined together into a single composite signal. This means that the luminance (B&W detail) information, chrominance (color) information and sync pulses are all combined.

#### 2.3.2 S-Video

In this S-video format (sometimes called S-VHS), the chrominance information is kept separate from the luminance and sync information, to reduce the possibility of interaction. S-video signals are transferred via twin coaxial or shielded cables, which are usually fitted with miniature 4-pin DIN plugs. Sometimes they are fitted with two RCA-type plugs, though, marked Y (for luminance plus sync) and C (for chrominance).

#### 2.3.3 Component Video

It is simply video where the components are separated to an even greater extent than that with S-video, so there is even less chance of them Interfering with one another. Instead of simply separating the luminance/sync (Y) and the chrominance (C) information, with component video the chrominance information is further separated into its own two components: the B-Y (blue minus luminance, also called Cb or Pb) and R-Y (red minus luminance, also called Cr or Pr).[5]

### 2.4 STRUCTURE OF A VIDEO SIGNAL

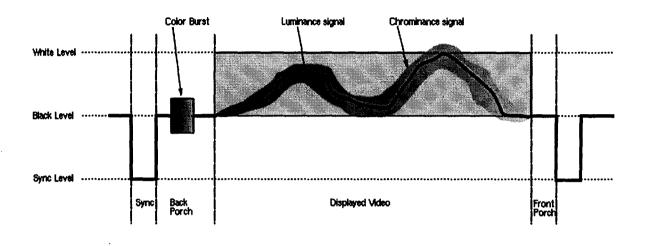

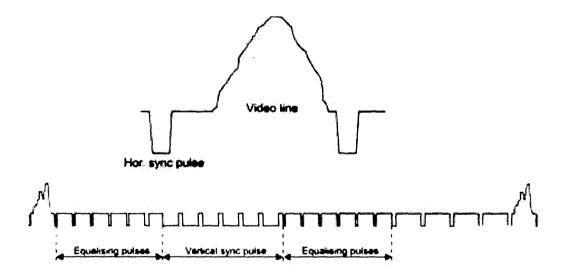

The video carrier is demodulated to give a composite video signal; this contains luminance (brightness), chrominance (color) and synchronization signals; [6] this is identical to the video signal format used by analog video devices such as VCRs or CCTV cameras. The minimum video signal level corresponds to maximum carrier amplitude, and vice versa. The carrier is never shut off altogether; this is to ensure that intercarrier sound demodulation can still occur. An illustration is given in figure 2.0 below.

7

Figure 2.1 Structure of a video signal (video line)

Each line of the displayed image is transmitted using a signal as shown in figure 2.0 above. The same basic format (with minor differences mainly related to timing and the encoding of color) is used for PAL, NTSC and SECAM television systems. A monochrome signal is identical to a color one, with the exception that the elements shown in color in the diagram (the color burst, and the chrominance signal) are not present.

## **CHAPTER THREE**

## 3.0 DESIGN ANALYSIS

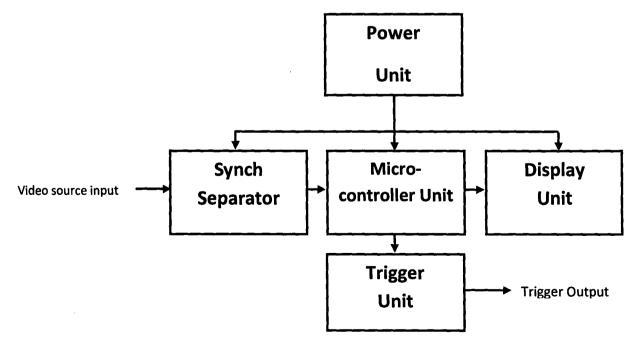

The video line selector is composed of the following modules

> Power supply

$\succ$  Synch separator

- Microcontroller unit

- > Display unit

- > Trigger unit

A block diagram of the whole project is shown in figure 3.0 below.

Figure 3.0 Video Line Selector Block Diagram

#### 3.1 POWER UNIT

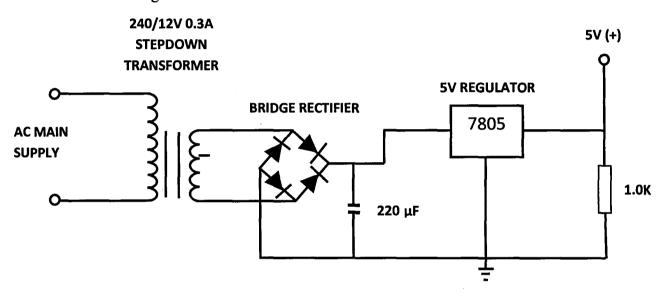

The line selector is powered by a regulated 5 volt dc supply. This was realized using a 0.5A, 240/12v step down transformer. A full-wave bridge rectifier was used for the rectification as shown in figure 3.1

Fig 3.1 power supply unit

#### 3.1.1 Transformer

A 220/12V transformer was used for the purpose of power supply to the line selector.

After stepping down to 12V, a full wave diode rectifier was then used to rectify to DC whose value was

$V_{\rm rms} = V_{\rm peak} / \sqrt{2}$

Where

$V_{\text{peak}}$  is the secondary transformer voltage.

$\sqrt{2}$  is the rms-to-peak scaling factor

$$V_{\rm rms} = V_{\rm peak} / \sqrt{2}$$

$V_{\rm rms} = 12/\sqrt{2} \approx 8.5$

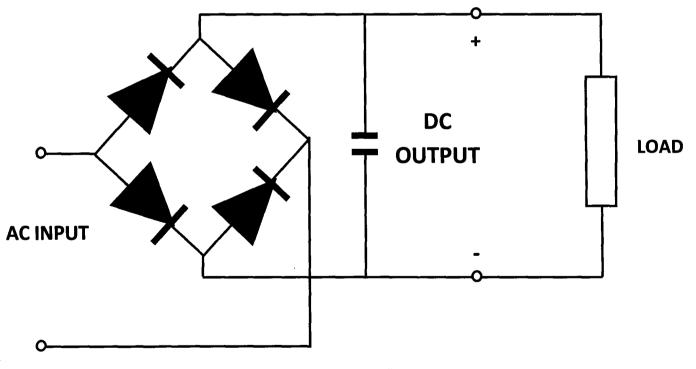

### 3.1.2 The Bridge Rectifier

The diode bridge rectifier is an arrangement of four diodes connected in a bridge circuit as shown in figure 3.2 that provides the same polarity of output voltage. It provides full wave rectification from an Ac input. Usually a capacitor is added to the rectifier to eliminate the AC ripples present in the DC.

Figure 3.2 Bridge Rectifier

The diodes put together have a forward voltage drop or junction barrier of 1.4V

Therefore,

$V_{out} = V_{rms} - 1.4$

$$= 8.5 - 1.4 = 7.1 \text{V}$$

The capacitor used was evaluated as follows

Q = CV = IT

#### Where

C is the value of the smoothing capacitance

V is the maximum value of the AC ripple voltage

I is the maximum load current

$T = \frac{1}{2}$  for full wave bridge rectifier

F is the main frequency

$C = IT/V = I \times \frac{1}{2}F/V$

The 7805 regulator needs a minimum of 7V to maintain a regulated output of 5V, therefore, a 2V peak-to-peak AC ripple voltage was maintained. Also, maximum current drawn is taken to be 150mA.

Evaluating for C, we had

$C = 150 \times 10^{-3} \times 1/(2 \times 50)/2$

= (0.15×0.01)/2

= 0.0015/2 = 0.00075

A 25V 22  $\mu$ F capacitor was used for the purpose of smoothing.

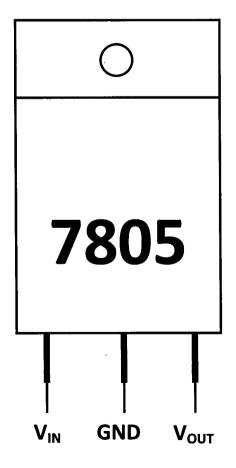

## 3.1.3 The Regulator

The regulator used is shown in figure 3.3 below.

Figure 3.3 Pin configuration of a 7805 Regulator

The regulator was connected across the smoothened DC to regulate the  $7.1V_{rms}$  to 5V at a maximum load current of 1A.

12V transformer was used so as to compensate for fluctuations in the AC supply by a margin of (7.1 - 5)V = 2.1V. The output of the regulator was used to power the whole circuit.

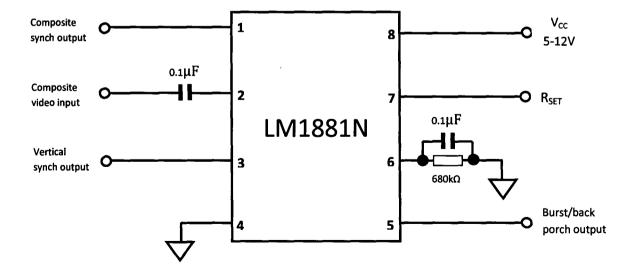

### **3.2 THE SYNCH SEPARATOR**

For the purpose of this project, the LM1881N synch separator was used. The LM1881 Video sync separator extracts timing information including composite and vertical sync, burst/back porch timing, and odd/even field information from standard negative going sync NTSC, PAL\*, and SECAM video signals with amplitude from 0.5V to 2V p-p. The integrated circuit is also capable of providing sync separation for non-standard, faster horizontal rate video signals. A schematic of the LM1881N is shown in figure 3.4 below

Figure 3.4 LM1881N pin configuration

#### Features

- > AC coupled composite input signal

- > >10k $\Omega$  input resistance

- <10mA power supply drain current</p>

- Composite sync and vertical outputs

- Odd/even field output

- Burst gate/back porch output

- Horizontal scan rates to 150 kHz

- Edge triggered vertical output

> Default triggered vertical output for non-standard video

Signal (video games-home computers).[7]

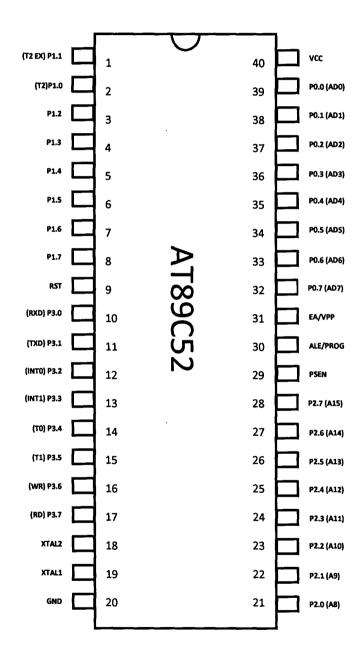

### **3.3 THE MICROCONTROLLER**

The AT89C52 is a low-power, high-performance CMOS 8-bit microcomputer with 8Kbytes of Flash programmable and erasable read only memory (PEROM). The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 and 80C52 instruction set and pin out. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C52 is a powerful microcomputer which provides a highly-flexible and cost-effective solution to many embedded control applications.

#### Features

- Compatible with MCS-51<sup>™</sup> Products

- 8K Bytes of In-System Reprogrammable Flash Memory

- Endurance: 1,000 Write/Erase Cycles

- Fully Static Operation: 0 Hz to 24 MHz

- Three-level Program Memory Lock

- 256 x 8-bit Internal RAM

- 32 Programmable I/O Lines

- Three 16-bit Timer/Counters

- Eight Interrupt Sources

- Programmable Serial Channel

- Low-power Idle and Power-down Modes.[8]

The pin configuration of the AT89C52 is shown in figure 3.5 below.

Figure 3.5 AT89C52 pin configuration

#### 3.4 THE DISPLAY UNIT

~

. .

Ĵ

The display unit uses a 16 character by 1 line to display the state of the solar panel. A 1602B LCD is used. It has maximum character length of 16 displayed on one line, an operating voltage of 5V. LCD displays designed around Hitachi's LCD HD44780 module, are inexpensive, easy to use, and it is even possible to produce a readout using the 8x80 pixels of the display. They have a standard ASCII set of characters and mathematical symbols. For an 8-bit data bus, the display requires a +5V supply plus 11 I/O lines. For a 4bit data bus it only requires the supply lines plus seven extra lines. In this project, the 8-bit data bus was used. When the LCD display is not enabled, data lines are tri-state and they do not interfere with the operation of the microcontroller.

## 3.4.1 Signals to the Display

The LCD also requires 3 control lines from the microcontroller:

- Enable: This line allows access to the display through R/W and RS lines. When this line is low, the LCD is disabled and ignores signals from R/W and RS. When (E) line is high, the LCD checks the state of the two control lines and responds accordingly.

- **Read/Write:** This line determines the direction of data between the LCD and microcontroller. When it is low, data is written to the LCD. When it is high, data is read from the LCD.

18

• **Register select:** With the help of this line, the LCD interprets the type of data on data lines. When it is low, an instruction is being written to the LCD. When it is high, a character is being written to the LCD.

#### 3.4.2 Writing and Reading Data from the Display

Writing data to the LCD is done in several steps:

- > Set R/W bit to low

- Set RS bit to logic 0 or 1 (instruction or character)

- Set data to data lines (if it is writing)

- $\triangleright$  Set E line to high

- $\blacktriangleright$  Set E line to low

Read data from data lines (if it is reading):

- ➤ Set R/W bit to high

- Set RS bit to logic 0 or 1 (instruction or character)

- Set data to data lines (if it is writing)

- $\triangleright$  Set E line to high

- > Set E line to low [9]

4

The schematic of the display is shown in figure 3.6 below.

Figure 3.6 Schematic of the HD44780U LCD

## 3.5 THE TRIGGER UNIT

1

The trigger unit was realized with the use of C945 npn transistor. The trigger to the oscilloscope is a high. The C945 acts as switch that sends a +5V to the collector pin when it has 0V as its base pin voltage.

Figure 3.7 C945 (NPN) transistor

### 3.6 PRINCIPLE OF OPERATION OF THE LINE SELECTOR

When video signal is fed to the line selector through k1, the same signal appears at the oscilloscope through k2. The oscilloscope is operated in the trigger mode, so it doesn't display wave form until it is triggered.

The line selector, based on what line selected, will send a trigger signal only at the start of that particular line selected. On receipt of the trigger, the oscilloscope displays the wave form of the video for a time period of  $64\mu$ s (length of one line).

The microcontroller is programmed in such a way to count the number of horizontal and vertical synch pulses such that the trigger is sent through k3 only when the line count equals the preset value set by the user. The press switch s1 and s2 are used to increment or decrease the preset value while s3 is for resetting the microcontroller.

### **CHAPTER FOUR**

#### 4.0 TESTS, RESULTS AND DISCUSSION

#### 4.1 TESTS

On completion of circuit construction, tests were carried out to ensure full functionality of the circuit. Tests carried out include

1) Hard ware

2) Soft ware

#### 4.1.1 Hardware testing

Hardware testing is basically a test of all physical components in the circuit. To ensure circuit functionality, each component was tested separately and the connection between components. Some of the tests carried out under hardware include

- Continuity Test: This is the testing of all physical connections or paths and polarity linking the different circuit components used. This was done to ensure that the circuit was realized as it is in the diagram.

- Short Circuit Test: The polarity of supply was tested all across the circuit before power on to avoid damage to the circuit due to short circuit current.

- Partial Contact Test: This was done to ensure that all components were firmly placed on board, so that errors that may arise due to partial contact were avoided.

#### 4.1.2 Software Testing

To avoid malfunction of the circuit due software errors, the software was also tested. The test carried out on software was basically running the software on the microcontroller after each segment is written. Errors detected were immediately corrected and the process repeated until software development was complete.

#### **4.2 CIRCUIT TESTING**

After the circuit was completed, it was tested. A video source was fed to the circuit and the input to the synch separator was tested. The output, the vertical and horizontal synch outputs were tested. Finally, the trigger output was tested. After all test results were completed, the circuit was placed in a case for protection.

#### **4.3 RESULTS**

When the video signal was fed into the circuit and a particular video line was selected, the oscilloscope only displayed an output at that particular line. An illustration of the wave form observed is shown in figure 4.0 below

Figure 4.0 Results

#### **CHAPTER FIVE**

#### **5.0 CONCLUSION AND RECOMMENDATION**

#### **5.1 CONCLUSION**

Based on the results obtained, it can be concluded that the video line selector sends a trigger signal to the oscilloscope at the start of a particular line selected by the user. This implies that the aims of the project which were to decompose the video signal and to monitor wave form of the different line contained in a video signal were achieved successfully.

It can also be concluded that defects, which may be caused by noise or other factors, in a video signal can be easily detected with the line selector.

#### **5.2 PROBLEMS ENCOUNTERD**

Though the project was completed successfully, there were a few problems that came up such as

- Sourcing information

- Financial problems

- Circuit design modification

- Broken microcontroller pin

- Software problems.

4

## **5.3 RECOMMENDATION**

The video line selector can be improved upon by in-cooperating a display to it that will display the wave form without the use of an oscilloscope. A modification of the selector could be interfacing it with a computer for further analysis of a video signals.

#### REFERENCES

- Electronic Test Insruments (Tech/Elektor Electronics) First Aurthorised Asia-Percific Edition. 1995 ISBN 981-214-734-9

- 2. www.wikipedia.com/wiki/Analog\_television

- 3. www.thefullwiki.org/analog\_television

- 4. www.maxim-ic.com/understanding \_analog\_signal

- 5. videosig.PDF

- 6. www.wikipedia.com/wiki/composite\_video

- 7. www.datasheetcatlog.com/datasheet/ LM1881

- 8. www.datasheetcatlog.com/datasheet/AT89C52

- 9. www.datasheetcatlog.com/datasheet/HD44780U (LCD-II)

- 10. B. L. Theraja and A. K. Theraja, a Text Book of Electrical Technology

## APPENDIX

### **PAL Video Timing Specification**

#### **General timing**

Line period 64 us (Micro-seconds)

Line blanking 12.05 + 0.25 us

Line sync 4.7 + 0.1 us

Front porch: 1.65 +- 0.1 us

Burst start 5.6 + 0.1 us after sync start.

Burst 10 +- 1 cycles

#### PAL details

1. CCIR/PAL standard video signal has 625 lines/frame and it repeats @ 25 frames/sec.

2. Each frame is split into 2 fields; - each consisting of 312.5 lines, called odd and even fields. Thus field rate is 50. i.e. CCIR /PAL std has 50 fields/sec rate .

**Interlacing**: The lines of odd-even field lie alternately. This method of scanning is called interlacing. This interlaced scanning is used to reduce flicker while displaying the image on a monitor. Interlaced scanning process is shown below.

## **Synchronization Pulse**

Starting of each Horizontal line is marked by a Horizontal sync pulse and the starting of each field by a vertical sync pulse. There are 625 Horizontal sync pulses per frame and 50 vertical sync pulses per second. Vertical sync pulse is a serrated block pulse as shown below.

Synchronisation pulses ensure that the video image is locked on a video monitor (or VCR etc) vertically and horizontally without any jitter or rolling. If vertical sync is lost, picture may move/tear vertically. If horizontal sync is lost, picture may move/tear horizontally. Synchronisation pulse ensure that all the equipment used in a CCTV set up like VCRs,

Monitors, Multiplexers and cameras are locked together. Video information is carried on each line except portions which are in blank periods (Horizontal & Vertical blanking / retrace period).

.