# DESIGN, CONSTRUCTION AND TESTING OF A DIGITAL TESTING KIT ((LOGIC PROBE AND LOGIC PULSER)

BV

BURAIMOH G.A. (93/3544)

DEPARTMENT OF ELECTRICAL/COMPUTER ENGINEERING SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY FEDERAL UNIVERSITY OF TECHNOLOGY MINNA, NIGER STATE

A PROJECT SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF A BACHELORS DEGREE IN ELECTRICAL/COMPUTER ENGINEERING

DECEMBER 2000

#### DEDICATION

I whole-heartedly dedicate my project and the entire degree to my parents Barrister (Rev) J. O. Buraimoh and Chief (Mrs) M. A. Buraimoh for their love and support. Also to God for his infinite mercy.

#### CERTIFICATION

This is to certify that this project titled "DESIGN CONSTRUCTION AND TESTING OF A DIGITAL TESTING KIT (LOGIC PROBE AND LOGIC PULSER)" was carried out by BURAIMOH GABRIEL ABIODUN under the supervision of Mr. Kenneth Pinne and submitted to Electrical and Computer Engineering Department, Federal University of Technology, Minna in partial fulfillment of the requirements for the award of Bachelor of engineering (B.ENG) degree in Electrical and Computer Engineering.

| Mr. Keneth Pinne<br>(Project Supervisor)      | Date |  |  |

|-----------------------------------------------|------|--|--|

|                                               |      |  |  |

| Engr. Dr. Y.A. Adediran<br>Head of Department | Date |  |  |

External Examiner

(7(((0)

#### DECLARATION

| , Durannon Gaoriei Abjodun (93/3544), hereby declare i   | that this project work is |

|----------------------------------------------------------|---------------------------|

| lesigned from basic electronic concepts and devices, con | structed and tested under |

| he guidance of my Supervisor, Mr. Kenneth Pinne.         |                           |

|                                                          |                           |

|                                                          |                           |

|                                                          |                           |

|                                                          |                           |

| BURAIMOH G.A                                             | DATE                      |

#### ACKNOWLEDGEMENT

My gratitude goes to my Head of Department, Engr. DR Y.A Adediran for the knowledge imparted in me.

Also to my supervisor, Mr. K.K Pinne, for his support, advice and positive criticism, towards the successful completion of this project.

To the lecturers in the department, whose courses I took. All these helped me a lot in the project design.

My sincere gratitude goes to my parents Barrister (Rev) J.O. Buraimoh and Chief (Mrs.) M.A. Buraimoh, for their financial support, love and sponsorship role played throughout my course in the university.

I cannot forget, but mention my brothers and sisters Mr. & Mrs. M.O. Buraimoh, Mr. & Mrs E.O Buraimoh, Mr. & Mrs. S.O. Buraimoh, Buki, Damola and Femi. To my friends Yemi, Yinka, Biodun, Bash, Sola and Sola Balogun.

Above all, my humble and sincere gratitude to Almighty God who remains constantly by my side no matter what life brings.

#### ABSTRACT

The design, construction and testing of a digital testing kit (logic probe and logic pulser) is covered in this report.

The digital testing kit is a two in a system (logic probe and logic pulser). The Logic probe basically detects the logic state whether its high "1" or low "0" at any given point in a digital circuit under test.

While the logic pulser generates logic pulses (a train of high and low logic states) for test purposes.

A single and straight forward style is used throughout this work, based on the knowledge acquired during my entire course of study.

### TABLE OF CONTENTS

| Title | page                            | *************************************** |                                        |

|-------|---------------------------------|-----------------------------------------|----------------------------------------|

| Ded   | cation                          | **************************************  | ······································ |

| Cert  | ification                       | **************************************  | iii                                    |

| Decl  | aration                         | *************************************** | iV                                     |

| Acki  | nowledgement                    | **************************************  | ~~~~~~~~~V                             |

| Abst  | ract                            | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  | Vj                                     |

| Tabl  | e of contents                   | *************************************** | Vijaviji                               |

|       |                                 |                                         |                                        |

| Chap  | oter One:                       | General introduction                    |                                        |

| 1.1   | Introduction                    | **************************************  | 1                                      |

| 1.2   | The Project :                   | aims                                    |                                        |

| 1.3   | Literature Ro                   | :V}&W                                   | 2-3                                    |

| 1.4   | Project Layo                    | }{}{                                    | 3                                      |

|       |                                 |                                         |                                        |

| Chap  | iter Two:                       | System Design                           |                                        |

| 2,1   | System Desi                     | gn Overview                             | 4                                      |

| 2.2   | The Logic Probe Unit Design5    |                                         |                                        |

| 2.3   | The Logic Pulser Unit Design7-8 |                                         |                                        |

| 2.4   | Power Suppl                     | y Design                                | 8                                      |

|       |                                 |                                         |                                        |

| Chap  | ter Three:                      | Construction, Testing And Results       |                                        |

| 3.1   | Construction and Testing9       |                                         |                                        |

| 3.2   | Results                         | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  |                                        |

| Chap | ter Four   | Conclusion and Recommendations |

|------|------------|--------------------------------|

| 4.1  | Conclusion |                                |

| 4.2  | Recommend  | ations12-13                    |

References

objectives of this project, to provide a device that can detect the logic state of a circuit whether high or low at any point in the circuit under test.

## 1.2 PROJECT AIMS

With much discussion above, this project is aimed at;

- 1. Providing a digital testing kit for use in digital technology laboratories.

- 2. Prolonging the life span of appliances by ensuring optimum use.

- Conserving power and consequently reducing power costs.

## 1.3 LITERATURE REVIEW

The stage where it is no longer strange to have empty laboratories is very dangerous, if a nation is to develop. This is a trend that must be changed for our nation to develop.

Most, if not all-training equipment must be imported from other nations.

This should not be the case as some equipment can be locally developed with advantage to suit our own environment.

Even when some training equipment can be locally manufactured, encouragement comes from nowhere. These problems must be tackled for overall interest of the nation.

This digital testing kit is a two in one system. It has a logic probe and a logic pulser. With the logic probe, the logic state when is HIGH "1" or when is LOW "0" can be detected at any point in a digital circuit. The logic pulser can be used to generate logic pulses (a train of high and low logic states) for testing purposes. This system has been designed with

absolute simplicity, one of the reasons being that it takes its power from the circuit under test. This covers a good voltage range, making it useful in various circuits. It can also be used for testing in Transistor Logic (TTL) circuit and also Complementary Metal Oxide Semiconductor (CMOS) circuits.

The logic probe is based on the CMOS inverter IC CD4049 while the pulser is based on a 555 timer connected in its astable multivibrator mode. This timer IC is hybrid in that it has digital and analogue components.

Under test, the systems positive voltage terminal (RED) is connected to the positive voltage supply of the circuit under test, while the negative (BLACK) is connected to ground. For the logic probe, its input which is pointed to touch the point on the logic circuit. The GREEN LED lights to show a HIGH logic state and the RED LED indicator means a LOW logic state.

#### 1.4 PROJECT LAYOUT

This project report is contained in four chapters for clarity. Chapter one gives a general introduction, defining the problem and proffering a solution. Chapter two details the system design analysis from the very beginning.

The system construction, testing results and modifications are contained in chapter three. Chapter four deals with conclusions and recommendations. A list of materials referenced is also contained in appendix A.

#### CHAPTER TWO

#### SYSTEM DESIGN

#### 2.1 SYSTEM DESIGN OVERVIEW

The "DIGITAL TESTING KIT (LOGIC PROBE AND LOGIC PULSER)" is a digital testing device that can be used in testing digital circuits.

This system has two main unit, the logic probe and the logic pulser. The system gets its power from the circuit under test. To test the logic state of a particular point in a circuit, the tip of the probe is pointed to touch that point and a GREEN display shows that the state at that point is HIGH or "I". When a RED light shows, ten the state at that point is logic "0" or LOW.

For the logic pulser, it provides a steady stream of pulses. A provision is made to vary the frequency of these pulses.

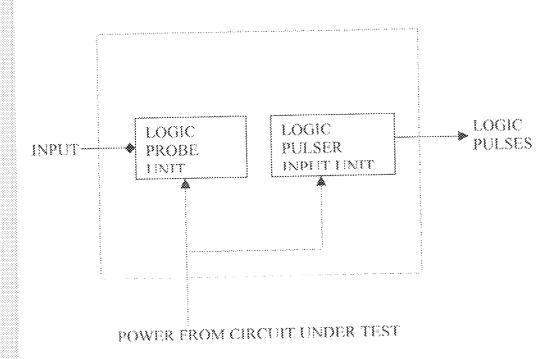

FIGURE 2.1 BLOCK DIAGRAM OF THE DIGITAL TESTING KIT.

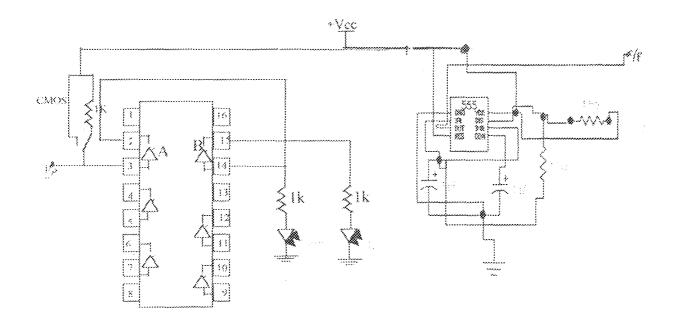

Fig 2.2 THE CIRCUIT DIAGRAM OF THE PROBE PULSER

#### 2.2 THE LOGIC PROBE UNIT DESIGN

A CMOS inverter IC CD4049 is used. The input to the probe is connected to one inverter gate, A and an LED indicator is used to indicate a LOW logic state. This means that the output of A will be HIGH only with a LOW input. This HIGH output is therefore used to power an LED indicator circuit to show that the logic state at the test point is LOW. If the input is HIGH, the output will be low and the LED indicator will not be powered and nothing will be displayed, showing that the test point is not LOW.

On the other hand, the input of another inverter gate, B is connected to the output gate A. The output of gate B is then connected to an LED

indicator circuit to show any HIGH state. This means that a state of HIGH at the test point will be inverted by gate A to a LOW logic level, this will again be inverted b gate B and the HIGH LED indicator circuit will be powered to signify the HIGH logic at the test point.

A typical Light Emitting Diode (LED) indicator is SHOWN below and

#### FIGURE 2.3 LED INDICATOR CIRCUIT.

Designed as follows. In order to limit the forward current flowing to an appropriate value, a resistor is connected in series to the LED.

The LED used here is a round head type with a quoted typical forward current of 10mA, which should not exceed 20mA. The resistor value is calculated as follows;

$$R = \frac{V - Vf}{I}$$

Vf is the forward voltage drop produced by the LED and C is the applied voltage and an above average value of 12V is considered in this design. It is recommended that Vf will be about 2 volts. The value of R can therefore be calculated as;

$$R = \frac{12 - 2}{10mA}$$

$$R = 1K\Omega$$

A single pole throw (SPDT) switch is used to select the type of logic family under test. This can be TTL or CMOS logic. Since the CMOS logic has a lower voltage level, a 1 kilo ohm resistor recommended to drop some of the excess voltage.

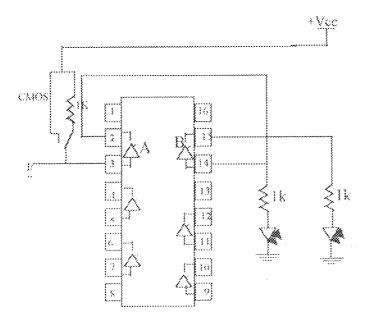

The complete diagram of the logic probe unit is shown below.

#### FIGURE 2.4 THE COMPLETE DIAGRAM OF THE LOGIC PROBE UNIT

#### 2.3 THE LOGIC PULSER UNIT

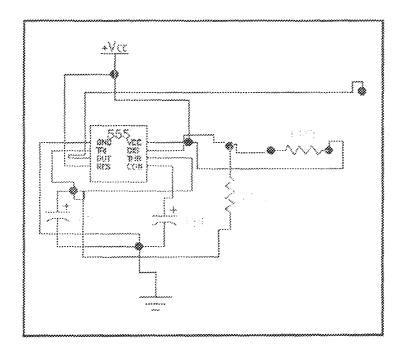

This unit is based on the 555 timer IC, wired as an astable mutivibrator to generate a steady stream of pulses with frequency that varies according to the components chosen.

The frequencies are determined by the following equation.

Frequency,

$$f = \frac{1.44}{(R_1 + 2R_2)C}$$

$$R_1$$

is a variable resistor with a maximum value of 250 kilo ohms. And  $R_2$  is 1 kilo ohm. And  $C=0.1\mu F$

Therefore,

Frequency,

$$f_{low} = \frac{1.44}{(0+2K)0.1\mu}$$

= 7.2Hz

And

Frequency,

$$f_{high} = \frac{1.44}{(250K + 2K)0.1\mu}$$

Therefore the frequency range is from 7.2 to 57.2Hz.

The pulser is powered by the supply voltage of the circuit under test.

The complete circuit diagram of the pulser is shown below.

#### FIG. 2.5 THE CIRCUIT DIAGRAM OF THE PULSER

#### 2.4 POWER SUPPLY DESIGN

The power supply needed to power this system is from +3V to +18V DC.

This covers the wide range for both TTL and CMOS logic circuits which is from +5V to +18V DC.

It is interesting to note that this system derives its power from the circuit under test. Therefore two crocodile clips are used here to tap power from the circuit under test. One is RED and the other is BLACK. The RED and the BLACK represent the positive supply voltage and the ground terminal respectively.

very encouraging and all the expected results were also obtained. Thus there was no need for any modification.

### CHAPTER FOUR

## CONCLUSION AND RECOMMENDATION

### 4.1 CONSLUSIONS

With the aims of designing, constructing and testing of a digital testing kit achieved in every respect, no other thing remains, but to say the project is a total success.

The design, construction and testing of a digital testing kit (logic probe and logic pulser) has been considered in this project report. The system has the advantage of getting its power supply from the circuit under test. Also the system is easy to maintain because of its simplicity and the components are easily replaceable.

With the aims of designing, constructing and testing of a digital testing kit achieved in every respect, no other thing remains but to say the project is a total success.

## 4.2 RECOMMENDATION

In as much as the student's first degree project is important, the problem usually encountered by the students in the course of construction are numerous and usually come in various direction. These problems include soldering (on the actual practical work) limited finance just to mention a few.

The time limit of the project, since it involves research and some thinking done, couple with the fact students do after some courses simultaneously and these course must also be passed before graduation.

The financing of the project is another factor limitating against a good project performance. This is because students do have a lot of good ideas on there project but a times have to drop it simply because of cost to implement it.

After a successful completion of this project, the following are recommended.

- 1. That the digital testing kit should be improved by including a frequency counter.

- A bar display should be included in the logic pulser to indicate a graph of the pulses.

- 3. A circuit should be incorporated in the logic probe to give a beep when HIGH logic state is detected.

- 4. More efforts should be made by all to encourage the development of local test equipment.

### REFERENCES

John C. Norris

Electronics: Practical Applications and Design,

Edward Arnold, 1988,

pp 75-79

Mike Tooley BA

Electronics Databook, PC Publishing,

pp 115, 185,110,111.

Theraja BL and Theraja AK

Electrical Technology

Nirja Construction & Development Co. Ltd, 1995

pp 1791-1814

Tran TU

Electronic Measuring System

John Wiley & Sons, 1987.

рр 33-37