# DESIGN AND CONSTRUCTION OF A DIGITAL PASSWORD ACCESS KEY FOR DOORS.

BY

# KADIRI BATHLONEW

MATRIC NO, 96/5201EE

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING, SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY.

FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA, NIGER STATE, NIGERIA..

IN PARTIAL FULFILLMENT OF REQUIREMENT FOR THE AWARD OF BACHELOR OF ENGINEERING DEGREE(B. ENG) IN ELECTRICAL AND COMPUTER ENGINEERING.

FEBRUARY, 2002

# CERTIFICATION

This is to certify that this work tilled "Design And Construction Of A Digital Password Access Key For Doors" was carried out by Kadiori Bathlomew under the supervision of Engr. Paul Attah for the award of bachelor of engineering in electrical and computer engineering of Federal University Of Technology Minna.

| ENGR.  | PAUL   | ATTAH    |    |

|--------|--------|----------|----|

| (PROJE | ECT SI | JPERVISO | R١ |

28/4/2002

DATE

ENGR. (DR) Y.A ADEDIRAN (HEAD OF DEPT.) 2 / Yran

DATE

OR. T.A AKINBULIRE (EXTERNAL EXAMINER) DATE

# DECLARATION

I Kadiri Bathlomew solemnly declare that every fact as regards to this project is a personal effort in security system design

# DEDICATION

This project is dedicated to my late father Mr Okhumoya Micheal Kadiri Okpodu, my late stepmother Mrs Asinawo Okhumoya and my dear mother Mrs Theresa Okhumoya.

# **ACKNOWLEDGEMENT**

Glory be to God Almighty and our Lord Jesus Christ for His love and mercy towards the success of this project (Amen)

I acknowledge my able lecturers; especially my supervisor Engr. Paul Altah for his moral and academic support, my head of department Engr. Dr. Y.A. Adediran and also Engr. Ahmed Shehu my project coordinator. Equally my sincere gratitude goes to my able parent and guardian Mr Benjamin Okhumoya and Mrs Mary Benjamin for their moral, parental and financial support through out my academic years.

I will not forget my able brothers and sisters that contributed to the success of this project. Mr Vincent Okhumoya, Hon. Joseph Okpodu, Mrs Grace Joseph Kadiri, Mrs Blessing Umcle, Mrs. Teghe Benjamin, Abdulkadiri Ibrahim, Madam U.K and Mr. Deji Akerere.

Equally Lacknowledge my able brother and friends Geoffrey Kadiri, Sunday Atoju, Sunday Joseph,

Francis Peter, Momoh Adamu, Abu Matthew, M.Y. Abubakar, Sadiq Adamu, Murtala Adamu, Friday

Bagudu, Ojo Atoju, Bro. Bernard, Giadys Mairo Kadiri, Stella Nnachere, Rachael Folashade Johnson,

Nonye and Jonathan Corson Likewise. Lappreciate the support of my younger ones Andrew alias Bature,

Emmanuel, Friday, Christiania, Daina, Clara, Sophia, Moses, Beauty, Veronica and Anthonia.

# ABSTRACT

Design and construction of a digital password access key for doors focussed at over coming the failure of old locks and key system was the aim of this project. For instance, the use of master keys, duplication of keys and weight weariness of keys are over came. The project was limited to its number of four input buttons as it determines its ability and reliability.

# TABLE OF CONTENT

| COVER PAGE                             | *   |

|----------------------------------------|-----|

| TITLE PAGE                             | #   |

| CERTIFICATION                          | 111 |

| DECLARATION                            | ŧ٧  |

| DEDICATION                             | ٧   |

| ACKNOWLEDGEMENT                        | VI  |

| ABSTRACT                               | Vil |

| TABLE OF CONTENT                       | VII |

| CHAPTER ONE                            | }   |

| I.I INTRODUCTION                       | 1   |

| 1.2 LITERATURE REVIEW                  | 1   |

| 1.3 PROJECT OBJECTIVE / MOTIVATION     | 3   |

| 1.4 PROJECT LAYOUT                     | 3   |

| CHAPTER TWO                            | 4   |

| 2.1 CHOICE OF COMPONENT                | 4   |

| 2.2 REVIEW OF GATES XTICS              | 6   |

| 2.3 DESIGN AND PRINCIPLES OF OPERATION | 10  |

| 2.4 MECHANICAL LOCK SYSTEM             | 14  |

| 2.5 HOW TO USE THE DEVICE              | 15  |

| CHAPTER THREE                          | 17  |

| 3.1 CONSTRUCTION                       | 17  |

| 3.2 TESTING                            | 17  |

| 3.3 RESULTS                            | 17  |

| 3.4 DISCUSSION OF RESULTS | 18 |

|---------------------------|----|

| CHAPTER FOUR              | 19 |

| 4.TRECOMMENDATON          | 19 |

| 4.2 CONCLUTION            | 19 |

| 4.3 SUGGESTION            | 19 |

| REFERENCE                 | 20 |

#### CHAPTER ONE

# 1.1 INTRODUCTION

Privacy and security is a day-to-day requirement of an individual. As such, this project is focus on the "Design and construction of a digital pass word access key for doors".

Password access is the ability of the device to retain an inputted combination of switches and only accept exactly the same switches as inputs with high accuracy to open the door or give access.

Though, this design is restricted to only four (4) inputs buttons, which gives rise to 24 or 16 possible combinations of password of which only one of them will open the lock, much reliability will be attained with increased number of input buttons, say eight (8) which has 28 (256) possible passwords, sixteen (16) with 65,536 password, while twenty four (24) has 274 which is equivalent to 16,777,216 possible combinations of password. Conclusively 2° possible combinations of passwords can be achieved with "n" being the number of input buttons going by the sequence of this project.

This device drives the lock open using the password as key to activate the lock.

In chapter one, historical background of locks and possible areas of application of this device were discussed. Two contain the general review of the components used in this project, while three deals with its principles of operation and four on the construction, testing and results achieved from this device. Finally, chapter five talk about recommendation, conclusion and possible suggestion in regards of this project.

#### 1.2 LITERATURE REVIEW

#### LOCKS AND SECURITY

The earliest known mechanical fastening for doors is the wooden Egyptian lock, in use four thousand years ago. Another prevalent type of ancient lock, found in China and other parts of the world is the padlock, which works on a spring bard principle. The key is a plain strip of metal, if slid in,

depressing the spring, drawing the barbs together and releasing them from the indentation the bolt can be withdrawn.

Yet another primitive lock is a screw action, padlock. Here the key is an ordinary male screw and as it is turned the barred is withdrawn and the shackie released.

The first lock made of metal which attempted to provide security by requiring a key of peculiar configuration were the warded locks made by the Romans.

# MODERN LOCKS

The security provided by modern locks began in the eighteenth century when an English man ROBERT BARRON invented the tumbler or lever tocks. Another is the combination lock, which has a boilt or shackle with slots in it. A number of rings (tumblers) are provided with numbers or letters around the outside and projection on the inside, which fit the slots. The rings must be lined up correctly in order for the shackle to be withdrawn.

For instance, if the lock has three rings with one hundred numbers on each, there are a million possible combinations only one of which will open the lock. SAFES usually have combination locks because these have no keyhole into which explosives can be inserted to blow the safe. Some times they also have time-lock devices, so that they cannot be opened during certain hours even by some one who has the combination.

# **ELECTRONIC LOCK**

Since the 1970s, electronic lock, which works on the same principles as the pushbulton telephone, was used in the United States. It has several spring-loaded buttons on the outside, each of which sounds a different electronic tone when it is pushed. The right sequence of tones operates the lock.

At present password usage is common among computers, either software or hardware based to safeguard the system, documents and Networks systems etc. Use of permit cards is also common in hotels, while remote controlled doors are highly used in advance countries.

Other types of locks and security systems might be available and are not mentioned in this writeup. Likewise, locks of similar characteristics to this particular project might be available too, but has not been seen or come across by the undertaker of this project. So, it is an original effort on security lock system.

# 1.3 PROJECT OBJECTIVE/MOTIVATION

Digital password key as the name implies plays a major role in the area of security and privacy. The following are the possible areas of its applications:

PRIVATE ROOMS: - This key or lock system can be used on private or personal room doors, such that only right owners gain access.

GATES: - If desired, building with gate can use this system with each member of the house having the same password.

INSTITUTIONS: - Places like ministries, offices, banks and companies can use this device after work hours, such that only authorised staff can gain entrance.

Electronic equipments & Machines can equally use it in guiding against unauthorised persons.

# 1.4 PROJECT LAYOUT

Chapter one contains general introduction of the project and historical background of locks and security.

Chapter two deals with the choice of components, their properties and applications as used in this project.

Chapter three is all about principles of operation of the device and its design illustration.

Chapter four talks about construction, testing, results and discussion in respect to the success of this project.

Chapter five is recommendation; conclusion and suggestion made in regard to this project and project in general.

# CHAPTER TWO

# 2.1 CHOICE OF COMPONENTS

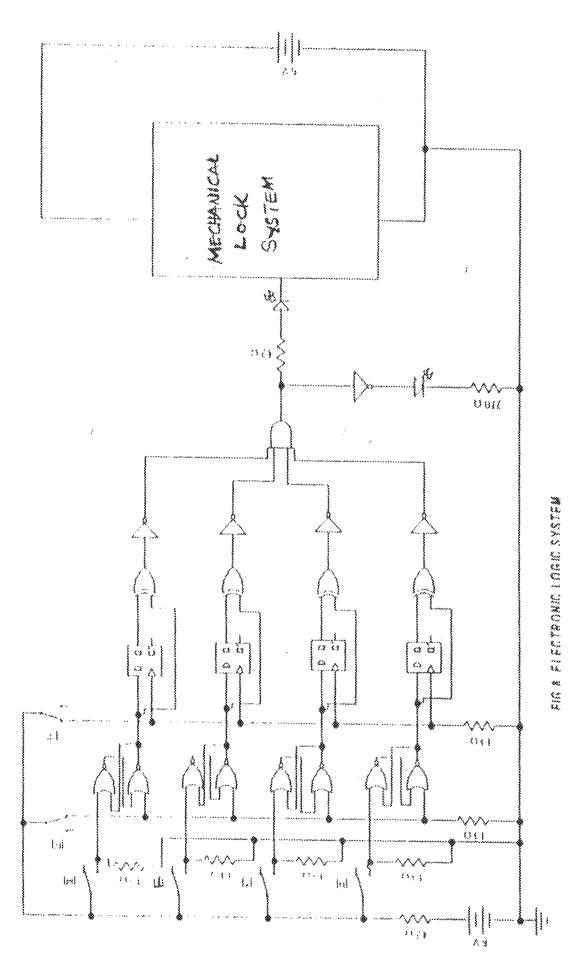

The project was built from TTC logic gates, which includes: - NOR gates, D-latch, exclusive - OR (XOR), inverters (NOT) gate, AND gates, LEDS, Switches, motor and gear system that made up the lock system.

Transistor - transistor logic (TTL), a widely used family of digital device was my choice of integrated circuit (IC) due to its fastness, inexpensive and easy usage.

Though, there are standard, high – speed, power Schottky and low-power Schottky, TTL gates.

Low power Schottky was chosen due to its peculiar characteristics stated below. Since TTL uses active low as well as active high signals, negative as well as positive logics were used in this design.

Also there are other types of Bipolar logic families to which TTL belongs and another the MOS families.

# 2.1.1 BIPOLAR FAMILIES

In the bipolar category are these basic families

Diode -Transistor Logic

(OTL)

Transistor-Transistor Logic

Emitter-Coupled Logic

(ECL)

(ITTL)

DTL uses diodes and transistors, the design was once popular is now obsolete. TTL uses transistors almost exclusively, it has become the most popular family of SSI and MSI chips, ECL the fastest logic family is used in high-speed applications.

# 2.1.2 MOS FAMILIES

The following are the MOS categories

PMOS - P - Channel MOSFET

NMON N Channel MOSFET

CMOS - Complimentary MOSFET

PMOS, the cidest and slowest type, is becoming obsolete. NMOS dominates the LSI field in its use for microprocessor and memories. (MOS), a push pull arrangement of n- and p- channel MOSFET is extensively used where lower power consumption is needed.

# 2.1.3 LOW - POWER SCHOTTKY TTL

By increasing internal resistances as well as using Schotlky diodes, manufacturers have come up with a compromise between low power and high-speed, low power Schottky TTL. Device of this type are numbered 74LS00, 74LS01, 74LS02 etc. It has a power dissipation of around 2mW and a propagation delay time approximately 10ns.

# 2.1.4 SUMMARY OF TIL GATES CHARACTERISTICS

To pull a TTL input low, a voltage between 0.0 and + 0.8V must be applied. The device or circuit used must be able to sink as much as 1.6mA of current to ground.

Pulling a TTL input high, voltage between +2.0 and +5.0 must be applied. The driving device or circuit must be able to source as much as 40µA.

The guaranted output high voltage of 2.4V is 0.4V greater than the required input high voltage of 2.0V. This gives a 0.4V noise margin between the output of a driving gate and the input of a receiving gate. The same noise margins exist for the output low maximum of 0.4V and the maximum input low voltage of 0.8V.

It takes 10 to 25ns for a change on the input of a TTL gate to cause a change on the output. The time is called propagation delay time.

Worst care values are shown below for normal TTL logics.

$$VoH-Min = 2.4v$$

i.e. on the input side a voltage has to be less than 0.8V to qualify as a low – state input and must be more than 2.0V to be considered a high state input. On the out put side, the voltage has to be less than 0.4V to be a low state output and more than 2.4V to be a high state output.

# 2.2.1 REVIEW OF GATES CHARACTERISTICS

# a. INVERTER

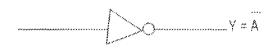

Fig 1.A. A schematic symbol for NOT gate

Fig 1.8. Truth Table

The inverter or NOT gate schematic symbol and truth table is shown above. The output behaviour is simply the opposite, inverse or compliment of the input. The Boolean expression for this is Y = A, the bar over the A indicates inversion and is read "A not"

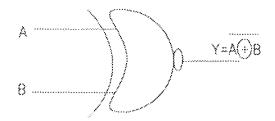

# b. NOR GATE

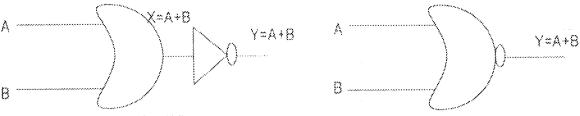

An OR gate with an inverter on its output forms a NOR gate. Fig 2.a below shows the schematic symbol for a NOR gate. Fig 2.b shows the truth table for an OR gate and a NOR gate. The Boolean NOR gate  $\frac{1}{2}$  is Y = A + B. Note that for this gate the output is low if any input is high (1)

Fig 2.a schematic symbol for NOR gate

| A | 8 | X=A+B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Y=A+8 |

|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 0 | 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1     |

| 0 | 1 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0     |

| 1 | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0     |

| 1 | 1 | i de de la companya d | 0     |

FIG 25 TRUTH TABLE

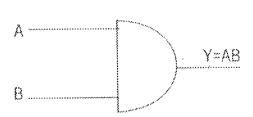

# c. AND GATE

The AND gate operates only if all its inputs are high. In this case, if A and B of the gate below are high, then the output Y will be high (Y). This is illustrated below:

| Δ  |   |   | <u>Y</u> |

|----|---|---|----------|

| () | 0 |   | 0        |

| 0  | į | I | 0        |

| Į  | 0 |   | 0        |

| 1  | § |   | 1        |

|    |   |   |          |

Fig3a, AND, gate schematic symbol

Fig 3.b Truth Table

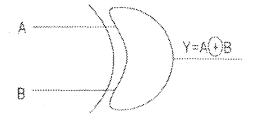

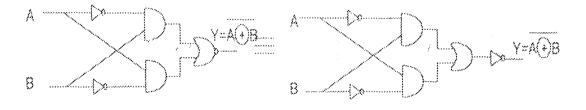

# d. XOR XNOR GATES

Last of the basic gates are the exclusive OR (XOR) and exclusive NOR (XNOR). Figure 4.1 below show the schematic symbol for the exclusive NOR gates. As shown by the truth table in Fig 4.III, the exclusive OR gate might be called a disagreeable gate because its output will be high (1) only if the two inputs disagreed with each other. The Boolean expression for an exclusive OR can be written as Y =AB+AB or Y=AB

Fig 4.1 XOR schematic symbol

Fig 4.II XNOR schematic symbol

| Α | 8  | AG B | AG B |

|---|----|------|------|

| 0 | 0  | 0    | 1    |

| 0 | 1  | 1    | 0    |

| 1 | () | 1    | 0    |

| 1 | 1  | 0    | 1    |

An exclusive NOR gate might be called an agreeable gate, or equality detector, because its output will become high (I) if the two inputs agreed (i.e. both are high or low). The Boolean expression for an exclusive NOR is Y = AB + AB = AB \(\overline{\text{QAB}}\).

Fig 4.IV EXCLUSIVE NOR GATE REALISATION

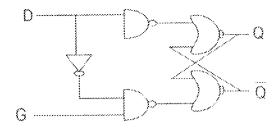

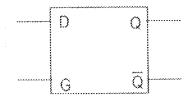

# e. D. LATCH

The D. latch is available in 7475 quad D Latch. As shown in the truth table below, figure 5.C. or analysing the circuit below, the Q output follows the D input as long as the enable "G" input is high. The logic state present on the D input just before the enable goes low will be latched on the output. For talches, the enable input is some times called the strobe, or gate. Note, in this project the latch was use for the memory.

Fig 5.A Logic design of D - latch

Fig 5.8 Schematic symbol

| Ð | G | Q | Q |

|---|---|---|---|

| Χ | 0 | Q | Q |

| 0 | 1 | 0 | 1 |

| 1 | 1 |   |   |

FIG 5.C Truth Table

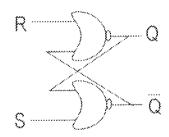

# f. R-SFLIP FLOP

FIG 6.a R-S Flip Flop symbol

| R | S | Q          | ACTION           |

|---|---|------------|------------------|

| 0 | £ | last value | No change<br>Set |

| i | 0 | Û          | Reset            |

|   | 1 | ?          | Forbidden        |

Fig 6.b Truth Table

The flip flop actually has two outputs defined in more general terms as Q and Q. It should be clear that regardless of the actual value of Q, its compliment is Q. There are two inputs to the flip-flop defined as R and S. The input/output possibilities for R-S flip-flop are summarized in the truth table in figure 6.b above.

It is also important to remember that TTL gates inputs are quite noise sensitive and therefore should never be left unconnected either to the output of a prior circuit, or if unused, to GND or +VCC.

# 2.2.2 INTERFACING LOGIC FAMILIES TO SIMPLE DISPLAYS AND RELAYS

The colour of light of the LED is determined by the type of materials it is made from and may be red, yellow or green. The forward voltage drop across the diode varies from about 1.5V for a red LED at 20mA to about 3V for a green LED at the same current standard. TTL, Schollky or high-power TTL can supply enough drive current to light an LED.

# SOLID STATE RELAYS

Most solid-state relays have TTL-compatible input and some have the input circuiting optically coupled to the trial control circuit, but in this project, thyristor was use as the relay or switch to power the motor each time the right password in entered.

# 2.3.0 DESIGNS AND PRINCIPLES OF OPERATION

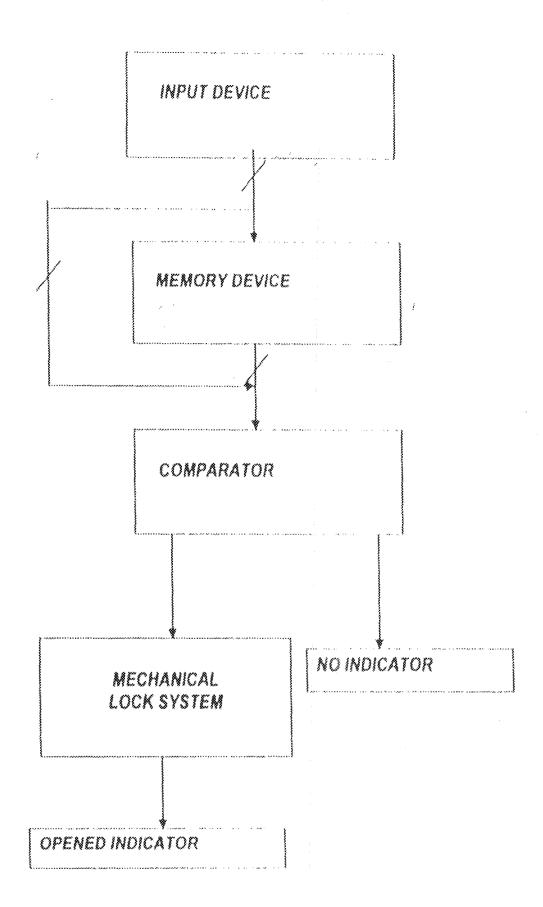

This project is made of two basic parts, namely, electronic and mechanical lock system. The electronic part is responsible for password saving and accessing, while the mechanical lock system does the opening and closing of the door. This is illustrated in the block diagram of figure 7.

# 2.3.1 ELECTRONIC PART

This device is made of three parts, the input device, memory device and the comparator interlinked to serve the purpose of passwording. Figure 8 below shows the design arrangement.

# i. INPUT DEVICE

The input device comprises of switches used in selecting the required combination of password and flip-flops, which retain the selected input (temporal memory). A set signal is sent to the R-S flip-flop each time the input switch is tapped, thus the flip-flop retain a high (1) at it output. This helps the memory device to get exactly the selected or required password and save. With the aid of the comparator, the input device equally helps in accessing the stored password.

This device is also RESET each time the RESET switch is depressed or the CLOSED button is enabled, therefore all the flip-flops outputs become low for new entry.

# **II. MEMORY DEVICE**

The memory device is built from D-fatch, which retains the selected inputs from the flip-flops before, and after the SAVE button is isolated.

This password remains as long as there is power supply from the battery and the SAVE button remains in isolation.

# III. COMPARATOR

The comparator is a logical combination of exclusive OR gates, inverters and four inputs AND gate. The XOR gate output only goes high each time there is a disagreement between the two outputs from the inputs device and the memory device. It also goes low when there is an agreement between them. For instance, if the input device output is high while the memory device output is low or vice versa, then the XOR output becomes high signifying disagreement.

Likewise, if both are high or low, the XOR gate output becomes low signifying agreement. With the inverters, a more justifiable outputs are obtained; i.e. high outputs for agreement and low outputs for disagreement.

Final comparison is done by the four input ANO gate, which only comes high when all its inputs are high indicating agreement from all the XNOR gate. Otherwise, remains low.

TRG THEOX X DIAGRAM

# 2.4. MECHANICAL LOCK SYSTEM

Locking is done by this part of the project. It comprised of resistors, thyristor, motor, switches and gear system. A schematic diagram is shown in figure 9.

# 2.4.1 OPEN AND CLOSE STATE

The open and close switches are interlocked in a way that the CLOSE switch goes OFF or springs out each time the OPEN switch is depressed and vice-versa.

With OPEN switch is depressed, conductor Y is made negative while the ENTER PASSWORD indicator remains high telling the operator to enter the right password. If done the SCR (thyristor) is fired through the gate, therefore allowing the passage of current to the motor through conductor X which becomes positive.

Activated motor runs the lock open until isolation switch A goes off to break power supply to the motor and then puts ON the OPENED indicator to signify FREE ACCESS.

The lock remains OPENED, until the CLOSE button is depressed to run the motor in the reversed direction, with conductor Y and X becoming positive and negative respectively.

At full lock the motor is powered OFF by isolation switch 8 putting ON the CLOSED indicator and ENTER Password indicator.

# 2.5. HOW TO USE THE DEVICE

# TO SAVE A PASSWORD IN THE MEMORY

At OPENED state select the SAVE button situated indoor, click the RESET switch to reset all the input device flip-flops outputs low (o), choose the desired combination of key buttons on the door labelled **B. A. T. H.** as password. After which the SAVE button is depressed to retain the chosen password in the memory.

# TO ACCESS THE SAVED PASSWORD

If desired to open the door, the stored password must be accessed correctly. Depress the OPEN button; the ENTER PASSWORD indicator remains high while CLOSED indicator goes low. Select the right password and use the ENTER key to order for cross checking. The No-indicator comes on when the entered password is incorrect.

When entered password is incorrect, use the RESET switch to reset the inputs and then choose the right password. If true, the thyristor is fired and the lock runs open. Finally the OPENED indicator is put ON indicating free access.

# 2.6. POWER SUPPLY

For a working device there must be a source of power or energy, otherwise the system remains redundant. Thus, dry cell of 6V was used in this project as the need arises for constant power supply.

The electronic or password device was powered separately from the mechanical lock system as transient affects the stored password.

# CHAPTER THREE

# 3.0 CONSTRUCTION, TESTING AND RESULTS

# 3.1 CONSTRCUTION.

Construction was done successfully with neat soldering and proper placement of components on board. Correct interlinking of pins was done as shown in figure 10 below. A wooden locker was also constructed to demonstrate the door.

# 3.2 TESTING

Commendable results were achieved using electronic workbench logic design. On breadboard also expected results were obtained and lastly, after construction testing was a success. Conclusively a working device was produced.

# 3.3. RESULTS

The following input labelled 8.A.T.H. were tested on the memory device and under listed output was achieved.

|                                                                                              | 8 | A             | ĭ                     | Н            |

|----------------------------------------------------------------------------------------------|---|---------------|-----------------------|--------------|

|                                                                                              |   |               |                       |              |

| 1.                                                                                           | 0 | 0             | 0                     | 0            |

| 2.                                                                                           | 0 | 0             | 0                     | 1            |

| 3.                                                                                           | 0 | 0             | 1                     | 0            |

| 4.                                                                                           | 0 | 0             | 0<br>1<br>1<br>10 / 1 | 1            |

| 5.                                                                                           | 0 | 1             | 0.7                   | ()           |

| 6.                                                                                           | 0 | 1             | 0                     | 1            |

| 7.                                                                                           | 0 | 1             | 1                     | 0            |

| 8.                                                                                           | 0 | 4             | d<br>d                | -}           |

| 9.                                                                                           | * | 0             | 1<br>1                | 0            |

| 10.                                                                                          | 4 | 0             |                       | 1            |

| 11.                                                                                          | 1 | 0             | 0<br>1<br>1           | 0            |

| 12.                                                                                          | 1 | 0             | 1                     | 1            |

| 13.                                                                                          | 1 | 1             | 0                     | 0            |

| 14                                                                                           | 1 | 1             | 0                     | 1            |

| 15.                                                                                          | 1 | 0111100001111 | 0                     | 010101010101 |

| 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>10.<br>11.<br>12.<br>13.<br>14.<br>15. |   | 1             | .s.                   | }            |

Each of these inputs too was compared wrongly and correctly with the right results obtain. All indicators equally came ON at the right time.

# 3.4 DISCUSSION OF RESULTS

The motor was powered separately from the electronic device as transient due to sudden switching of the motor affects the stored memory. Resistors of IKO were used at switch points where a low and a high is required in order to avoid floating input at low state and short circuit at high state.

# CHAPTER FOUR

# 4.0 RECOMMENDATIONS AND CONCLUSION

# 4.1 RECOMMENDATIONS

The project is friendly and useful to the society. With increased number of inputs device, memory device and the comparator, a more reliable device of better abilities to this will be obtained. Likewise, if a rechargeable battery system is used with this device on the door, a well-secured lock system is our limit.

Though, a lot of improvements can be made on this project, especially in the area of indicators, an LCD dot matrix decoder can be used to display all the indicated outputs one after the other. Another area is that all the input button can only be selected ones, improvements can be made to allow double or triple selection.

# 4.2 CONCLUSION

It is good to be an engineer to take up the challenges of engineering. It was not easy, after facing all the challenges of failure and still come out with a commendable achievement. To God be the glory.

The project was very good, logical and very sensitive. The aim of the project was fully achieved meaning an improvement in security system.

# 5.3. SUGGESTIONS

Students are faced with the problem of looking for project titles due to in availability of working materials, so if the University can make provision of project materials, the students will do better by making strong or complex projects in all fields of engineering.

Considerable time should be given to students to boost their knowledge of practical. We can even do better than the white men, if special attention is given to student.

# REFERENCE

1. DONALD P. LEACH (1986)

ALBERT PAUL MALVINO

DIGITAL PRINCIPLES AND APPLICATIONS (FOURTH EDITION) Mc GRAW - HILL INTERNATIONAL EDITIONS (ELECTRICAS AND ELECTRONICS ENGINEERING SERIES) NEW YORK ATLANTA DALLAS ST. LOUIS SAN FRANCISCO

2. DOUGLAS V. HALL (1983) MICROPROCESSOR AND DIGITAL SYSTEMS (SECOND EDITION) Mc GRAW - HILL INTERNATIONAL EDITIONS

(COMPUTER SERIES)

LISBON LONDON.

PP 188 - 256.

3. HOW IT WORKS (1987, 1989) THE NEW ILLUSTRATED SCIENCE AND INVENTION ENCYCLOPEDIA (VOLUME 11) HIS STUTTMAN INC. PUBLISHERS, WEST POINT, CONNECTICUT 06889

MARSHALL CAVENDISH LIMITED.

PP 1464 - 1466.