# COMPARATIVE EVALUATION OF TRAFFIC LIGHT REALIZATION USING COMBINATION AND MONOSTABLE MULTIVIBRATOR METHODS OF DESIGN.

BY

# 'SALAM SHAYO S.

(89/1204)

# DEPARTMENTAL OF ELECTRICAL AND COMPUTER ENGINEERING SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY, FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA.

"A PROJECT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF ENGINEERING TECHNOLOGY IN DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING, SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY, FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA, NIGER-STATE."

FEBRUARY 1997

#### CERTIFICATION

The undersigned certify that this project has been carried out by <u>Abdulsalam</u> Shakiru Shayo and has been read and approved as meeting the requirements of the Department of Electrical and Computer Engineering Technology, Minna, for a project report in partial fulfillment of the requirements for the award of the degree of Bachelor of Engineering Technology.

PROF. S.O. AJOSE (SUPERVISOR/DEPARTMENTAL CHAIRMAN)

DR. E.B. OYETOLA (Ag. DEAN OF ENGINEERING SCHOOL)

EXTERNAL EXAMINER

DATE

DATE

DATE

ii

# DECLARATION

I hereby declare that this project work is a genuine one which was wholly and solely constructed by me under the supervision of Prof. S.O. Ajose, Chairman department of Electrical and computer Engineering, federal University of technology, Minna.

Information derived from published and un published work of others has been acknowledged in the text.

ii:

s.s.s

# DEDICATION

iv

This project work is dedicated to :

- Glory of almighty Allah.

- My late grand mum- Hajiya Wuraola A. Garba.

- My blood; Bayo, Dola, Joke, Sina, Tunde and Wole.

# ACKNOWLEDGEMENT

Praise be to allah, the cherisher, the most gracious, the most merciful, sustainer of the world and peace and blessings of Allah be unto his messenger, Muhammad, the seal of all prophets. Praise be to Allah the lord of universe.

Sincere thanks are due to my supervisor, Professor S.O Ajose, who gave me the benefit of his wisdom, for his careful guidance and timeless interest in my work for seeing me through it and for making a number of corrections, suggestions and remarks.

I am grateful to all my lecturers in the school of Engineering who taught me and helped me in one way or the other during the course of my studies; especially: late engineer L.A Moses who started the supervision of this project work but due to Allah's will, was unable to end it. May his soul rest in perfect peace.

My appreciation goes to all other lecturers too: Engr. Dr. Oyetola, Engr. Dr. Akinbode, Engr. Dr. Onifade, Engr. Dr. Ajisegiri, Engr. Abifarin, Engr. Rumala, Engr. Adediran, Engr. Ibokwe, Engr. Raji, Engr. Obiora, who also leaves their respective working place to contribute out of their knowledge to nation technology, man power development, Engr. MoHi'd Shehu and all others that have contributed to my achievement I can not mentioned their names. I am grateful. I cannot but register my unreserved appreciations to my friends; Afolabi M.A, Opadiran O.N, Adeshina S.A, Fon C.A, Banseka H.S.T, Fon C.T. Jnr, Shaba H.J, Opadiran O.K, Dukuye B. Fagoyinbo L.A, Adiasor I.K, Adesokun B.A, Olobayo S.B, Labiran O.A, Fadeji N, Akintola O.D, Adedigba A.M, who have made my campus life and stay in Minna an interesting and memorable one. Thanks for some wonderful memories.

I wish to record my appreciation to some of my friends, colleagues, neighbours, who had in one way or the other assisted during the course of my program. They are Ayanbukola Tayo, Amizat Waliyi, Olarinoye T.O.D, Aliyu M, Wokoma O.J, Aluko A.A, Bello S.J, Soul, Bassey, Balogun-Oluwa O.J, Yabba Y, Barde D.D, Aileku A.L, I. Isah Atodo, Nor O.S, Ipaye S.A, Musbau Opaleye, Gidado Ibrahim, Kehinde Ojediran, Andrew and Elijah, Bayo and Olumide, Ladan, Jafaru Kwali, and the Kwalis, Jibril and sons, Labaran and those not mentioned by names, I am most grateful to them all.

My profound gratitude goes to Dr. A.A Salawu, Sikiru A.Salawu, Alhaji and Hajiya A.A Bello, their family, Alhaji S.T Bello, Adolphus, Cosmos, Osita and Ifeanyi Emenike, Anderson Valentine, Longenus and Anayo Ojilere, Alhaji and Hajiya R.A Alao, Dapo Alao, Layi Hamzat, Teslim, Tirimidi and Wasiu Rafiu, Ajao Kasali, Mikailu Mustapha, Musbau I. Bello, and all that I cannot mention their names for their moral, financial and intellectual support. May Allah be with you all.

vi

Big thanks to Bamidele F.F for her love, concerned and supports (morally and financially) during the study period. I am indebted.

Words are inadequate to express the degree of gratitude I owned my darling friend; Kilani Ibrahim Balkisu- for her understanding, moral and intellectual supports, caring and kindness, truthfulness and generousity, and also for been there anytime she is needed. I am proud of you.

I am also grateful to my parents Alhaji and Hajiya S.A. Abdulsalam for their financial support, encouragement and unflinching committment to my academic pursiut. I am particularly grateful to my mother - Abdulsalam M.A. for all she had done for me throughout the duration of my academic pursuit, infact, she is the Architect of my life. Oh, Allah my Lord-bestow them your mercy as they cherished on me in childhood.

I am indebted to authors and publishers of the enlightening works listed in the reference which has been consulted and quoted literally. My debt to these Writers will be sufficiently clean from the references made to them and if any remain unacknowledge, the oversight is unintentional.

My gratitudes goes to Alhaji Hassan Bahago for his effort in securing me a place for my degree programme and also as a guardian throughout the course of my studies. Alhaji, words are

vii

not enough to express my thanks. May Allah be with you and guide you in all your endeaviours.

Lastly, my gratitude to Hajiya H. Raji and her family most especially Raji Hamzat, Alhaji Rafiu and his family, Engr. Lateef Salahu, Mal. Abdulateef Alani Sanyaolu Arewa and his family, Alhaji Wasiu Ayinde and his band, Mr Hussain Jimoh and his family, the Afolabis (Debo and Tunji) and all that I wished but I cannot mention by name, Thanks and may Allah bless you all. Oh, Allah; I am grateful to you.

- Shayo Salam

viii

#### ABSTRACT

1.1.1

The project dealt with comparative analysis and evaluation of traffic light realization using combinational logic circuit and MONOSTABLE MULTIVIBRATOR methods of design.

The basic factors used in comparative analysis and evaluation are cost of production, space occupation, speed and reliability to know which of the design method is more considerable and economical for future environmental development.

In proceeding chapters, like in chapter one, introduction and literature review was dealt with, review the implication of traffic jam, also compared different methods of traffic light realization design and their mode of operation.

Problems statement and methodology was discussed in chapter two, stating various type of problems that has been encountered in traffic light implementation.

Chapter three deals with selection and design of components. Components selection and design was done in such a way that there will be a room for comparison between the two design methods.

In chapter four, Comparative evaluation of the design methods (combinational and monostable multvibrator) was carried out using the above stated factors. Most of the project work was performed

ix

in this chapter because the design and its pin connection was done here too.

Finally, chapter five talks about the conclusion and recommendation where the appropriate design was recommended for future design.

$\mathbf{x}$

# TABLE OF CONTENTS

1 contract

| CERTIFICATIO | N.          | •   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | i:  | Ĺ          |

|--------------|-------------|-----|-----|------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|---|---|---|---|---|---|-----|------------|

| DECLARATION  | •••         | •   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | ii: | Ĺ          |

| DEDICATION   | ••          | •   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | i   | 7          |

| ACKNOWLEDGEM | IENT        | •   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | • • | 7          |

| ABSTRACT     | •           | •   | •   | •    | •  |     | •   | •   | •   | •   | •.  | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | i   | ĸ          |

| TABLE OF CON | JTEN        | TS  | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | . : | x          |

| CHAPTER ONE  |             |     |     |      |    |     |     |     |     |     |     |     |     |     |     |     |    |     |   |   |   |   |   |   |     |            |

| INTRODUCTION | ŧ.          | •   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | •   | 1          |

| 1.1 LITERATU | JRE         | REV | /IE | EW   | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | •   | 3          |

| CHAPTER TWO  |             |     |     |      |    |     |     |     |     |     |     |     |     |     |     |     |    |     |   |   |   |   |   |   |     | -          |

| PROBLEM STAT |             |     |     |      |    |     |     |     |     |     |     |     |     |     |     |     |    |     |   |   |   |   |   |   |     |            |

| 2.1 PROBLEM  | STA         | TEN | 1EN | IT : |    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | •   | . <b>6</b> |

| 2.2 METHODOI | JOGY        | :   | •   | •    | •  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | •   | 6'         |

| CHAPTER THRE | <u>3e</u> . | •   | •   | • ′  | •  | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •   | ٠  | •   | • | • | • | • | • | • | .1  | 1          |

| COMPONENTS 2 | AND         | DES | SIG | 3N   | OF | ר ק | [R] | \F1 | 7I( | C I | JIG | HJ  | с ( | 201 | NTI | ROI | L] | ERS | 5 | • | • | • | • | • | 1   | 1          |

| 3.1 COMBINAT | FION        | IAL | LC  | )G]  | C  | CI  | IRC | CU  | IT  | DI  | ESI | [G] | 1   | •   | •   | •   |    | •   | • | • | • | • | • | • | 1   | 1          |

| 3.2 DESIGN   | OF F        | EG  | JLF | ΥТE  | ED | PC  | OWI | ER  | SI  | JPI | 5L2 | Z   |     | •   |     |     |    |     | • | • |   |   | • | • | 1   | 12         |

xi

| 3.2.1 SMOOTHING THE RECTIFIED A.C SUPPLY                                                                 | 4  |

|----------------------------------------------------------------------------------------------------------|----|

| 3.2.2 STABILIZING THE SUPPLY                                                                             | 5  |

| 3.2.3 USED COMPONENTS AND VALUES                                                                         | 5  |

| 3.3 THE PULSE GENERATOR: $\dots$ | .8 |

| 3.4 MODULOS -16- COUNTER USING JK FLIP-FLOP                                                              | 2  |

| 3.5 COMBINATIONAL LOGIC CIRCUIT TRAFFIC LIGHT CONTROLLER                                                 | 33 |

| 3.6 THE OUTPUT STAGE                                                                                     | 18 |

| 3.7: COMPONENTS AND VALUES                                                                               | 10 |

| 3.8 TRAFFIC LIGHT CONTROLLER DESIGN USING MONOSTABLE<br>MULTIVIBRATOR                                    | 42 |

| 3.8.1 CALCULATION OF THE TIME DELAY                                                                      | 43 |

| CHAPTER FOUR                                                                                             | 55 |

| COMPARATIVE EVALUATION OF THE DESIGNS                                                                    | 50 |

| 4.1 PRODUCTION COST                                                                                      | 50 |

| 4.2 RELIABILITY                                                                                          | 55 |

| 4.2.1 IMPORTANCE OF RELIABILITY                                                                          | 57 |

| 4.3 SPACE                                                                                                | 61 |

| 4.4 SPEED:                                                                                               | 61 |

| 4.5 COMPARISM AND EVALUATION OF THE METHOD:                                                              | 62 |

xii

| <u>CHAPTER FIVE</u>           | •   | 63  |

|-------------------------------|-----|-----|

| CONCLUSION AND RECOMMENDATION | •   | G3  |

| 5.1: CONCLUSION               | •   | Ç3. |

| 5.2 RECOMMENDATION            | - ( | 63  |

| REFERENCES                    | • 1 | 34  |

xii i

#### CHAPTER ONE

#### INTRODUCTION

"Traffic" means, the movement of people or vehicles along roads or streets, of ships in the sea, planes in the air space, movement of products on conveyor belts e.t.c.

Due to development and everyday increase in human population and vehicles, traffics leads to "Traffic jam or congestion", and this traffic congestion has being one of the utmost problem in our cities and towns in all corners of the world. Various accidents have resulted as a result of traffic congestion which leads to loss of lives and properties.

Attempt have been made in all ways to avoid if possible or reduced the problem of traffic congestion. Like in these days and up till today in most cities and towns in developing countries, traffic warders are being employed, making use of hand to control traffic. There are lot of imperfection in this method of traffic control due to fatigue during the period of working, poor conditions of service, risk taking, scaring and human feelings during and after fatal accidents, and mis-interpretation of sign given by warder in conjunction with rule - activities of some drivers.

For more efficiency and perfection in traffic control, different automatic traffic control methods have been adopted. They are:

Combination Logic Circuit type, Micro-processor type, Microcomputer type, Programmable logic Array (PLA) type e.t.c. These automatic traffic light control systems employ different types of lighting colours and the most commonly used lighting colours in traffic are: Red, Amber and Green. The meaning of these colours are;

i. Red - Stop.

ii. Red/Amber - Get ready to start moving.

iii. Green - Go.

iv. Amber - Get ready to stop.

The lighting of each bulb has duration which can be vary by using couples of capacitors and resistors, though in this project work we are not really concerned with the time duration but the evaluation of different design methods.

Automatic traffic light control are categorized into four (4) places:

A. Fixed time signal; the lighting duration of all the lights (Red, Amber and Green) are fixed or remain unchanged until they are reset.

<u>B. Time variable signal:</u> this works in such a way that the lighting periods change at specify time of the day for Red, Amber and Green lights.

<u>C. Vehicle actuated signal:</u> it works with the vehicle movement over a detector to an automatic controller gives signal or

#### controls the lights.

<u>D. Computer control traffic</u>: Area computer control traffic uses computer for the storage of a number of traffic plans designed to match all the various traffic conditions likely to be encountered. The computer sends instructions to all the various controllers in the area according to the particular plan selected. The computer also monitors the system to check for controller or detector faults and thus considerably speeds maintenance and avoid lengthy delays. Electropie -

In this project, a comparative analysis and evaluation of the methods of designing traffic light is to be carried out, but before then a literature survey on the topic was carried out.

#### 1.1 LITERATURE REVIEW

Due to the problems encountered with manually controlled traffic, many methods of controlling traffic automatically have been developed and some of the methods are as follows:

- A. Combinational Logic Circuit method.

- B. Monostable Multivibrator method.

- C. Programmable Logic Array (PLA) method.

- D. Microprocessor method.

- E. Microcomputer method.

Here in Electrical and computer engineering department, F.U.T, Minna;

- In the work carried out by Austin A. in 1992, he made use of combinational logic method of designing.

- In Ogunkayode A. Olufemi's work of 1994, he made use of monostable multivibrator method to carry out the design of traffic light, and in the project work carried out by Ogungbesan A. Adeniyi in 1994, he made use of Programmable Logic Array (PLA) method of designing.

- In most advanced countries like America, Russian, France, they make use of Microprocessor and Microcomputers in implementing their traffic light control systems.

This project is concerned with comparative analysis and evaluation of two of the different methods of design (combinational logic circuit and Monostable multivibrator methods of design) using the following criteria:

- Production cost

- Reliability.

- Space.

- Speeds, and to therefore propose which is more suitable for implementation in our environment.

In chapter two, the problem statement and methodology of evaluation is presented.

In chapter three selection and designs of various components and modules are presented.

Chapter four talks about comparative evaluation of the design methods.

While in chapter five, conclusion and recommendation of the project topic was carried out. Where the suitable method of design for our environment was recommended for future execution.

#### CHAPTER TWO

1.00

#### PROBLEM STATEMENT AND METHODOLOGY

### 2.1 PROBLEM STATEMENT:

It is discovered that the traffic light controller implemented using combinational logic circuit has low reliability value due to too many connections of wires, too many components like capacitors, transistors, ICs, Diodes, e.t.c. The moment one of these components fails, the system as a whole fails or when there is disconnection of one of the connected wires, the system also fails.

Therefore, for economical and durability purposes it is required to carry out a comparative evaluation of combinational method of traffic light design and monostable multivibrator method of design using the following criteria and then give a recommendation for the traffic light which is more suitable and durable for implementation in our environment - Minna metropolis.

The criteria to be used for evaluations are;

- i. Production cost.

- ii. Reliability of the system.

- iii. Speed and

iv. Space on printed circuit board (Vero board).

#### 2.2 METHODOLOGY:

The methodologies employed for the comparative evaluation involves (consists) of the following steps:

i. The design of traffic light controller is carried out using combinational Logic Circuit method and Monostable Multivibrator method. ii. The pin connections of the ICs and the wire connections of the analog electronic components involved are carried out and from here the evaluation of the two methods of designs proceeds.

iii. The evaluation is being carried out using the criteria: Production cost, reliability, space and speed, as follows:

#### - Production cost:

The bill of quantity, labor cost, and overhead cost prices of producing electronic systems in Minna town for each design is computed and compared to determine which is more cheaper. See the table 1 for the format of the bill of quantity:

# TABLE 1 BILL OF QUANTITY TABLE

| S/N | NAME OF | QUANTITY | COST/ITEM | TOTAL COST |

|-----|---------|----------|-----------|------------|

|     | ITEMS   |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          | }         |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     |         |          |           |            |

|     | TOTAL   |          |           |            |

|     |         |          |           |            |

į...

- Labor cost is also calculated. The labor cost is taken as 20% of the material cost, if direct labor used.

Material Cost(MC) x 20 Labor Cost (LC) = ----- N 100

- Overhead Cost:

The overhead cost includes all expenses incurred, different from material and labor costs and is taken as 10% of the cost material.

Material Cost (MC) x 10 Overhead Cost (OC) = ----- <del>N</del> 100

Total production cost = MC + LC + OC

### - Reliability:

The reliability of each of the design work would be calculated and compared to determine which one has higher reliability. The following formula is used for the calculation of the reliability  $(R=e^{-it})$ :

$R = R_{IC} + R_T + R_D + R_C$  R = Total reliability  $R_{IC} = \text{Reliability of Integrated Circuit (IC)}$   $R_T = \text{Reliability of Transistor}$   $R_D = \text{Reliability of Diodes}$   $R_C = \text{Reliability of Capacitors}$

#### - <u>Space</u>:

The number of ICs, Diodes, Resistors, Transistors, and Capacitors wold be controlled for each of the design and compared to determine which of the design occupied more spaces.

- Speed:

The speed of each of the design circuit diagram for the light would be determined. This is determined by using the following formula:

$Y = Y_{IC1} + Y_{IC2} + \ldots + Y_{ICn}$

Y = delay time

$Y_{IC1}$  = delay time for IC1

$Y_{ICn}$  = delay time for n IC

Y is determined through the longest wire connection on veroboard.

A comparative table of evaluation is drawn as shown in Table2 for clear comparison and analysis.

# Table 2

|               | PRODU | JCT              | RELIABILITY | SPACE | (No | IC) | SPEED  |

|---------------|-------|------------------|-------------|-------|-----|-----|--------|

|               | COST  | ( <del>N</del> ) | (NO UNIT)   |       |     | :   | (secs) |

| COMBINATIONAL |       |                  |             |       |     |     |        |

| LOGIC         |       |                  |             |       |     |     |        |

| DESIGN        |       |                  |             |       |     |     |        |

| METHOD        |       |                  |             |       |     |     |        |

| MONOSTABLE    |       |                  |             |       |     |     |        |

| MULTIVIBRATOR |       |                  |             |       |     |     |        |

| DESIGN        |       |                  |             |       |     |     |        |

| METHOD        |       |                  |             |       |     |     |        |

#### CHAPTER THREE

# COMPONENTS AND DESIGN OF TRAFFIC LIGHT CONTROLLERS

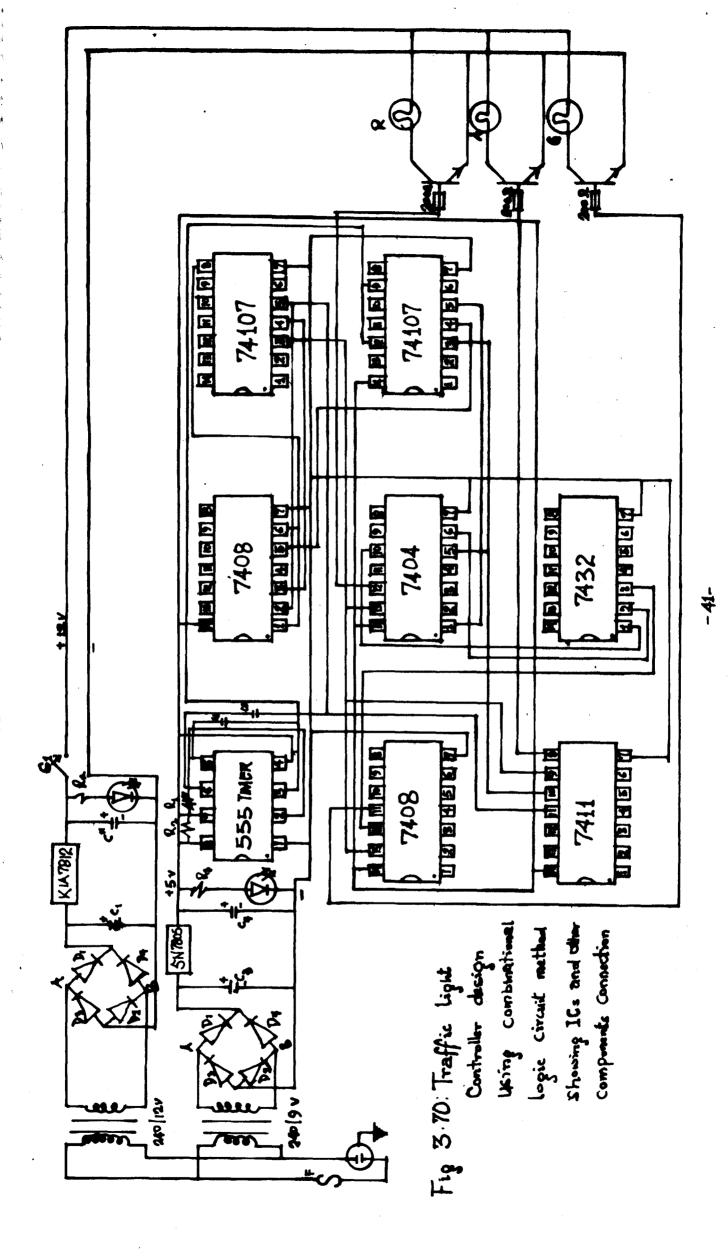

This section of the project consists of two design of traffic controller and Monostable multivibrator design of traffic light controller.

# 3.1 COMBINATIONAL LOGIC CIRCUIT DESIGN

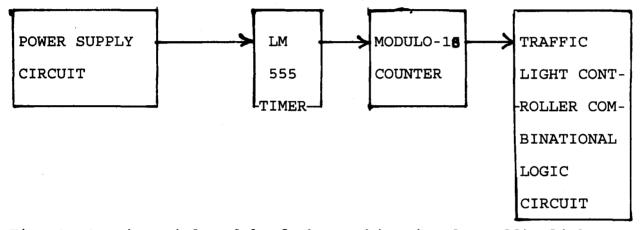

The model of the traffic light controller system is illustrated pictorially as shown in Figure 3.1 below:

Fig. 3.10: pictorial model of the combinational traffic light controller.

Traffic light controller system was designed basically on electronic components like capacitors, diodes, IC's, resistors and transistors. The system is simply based on the sequential counting of a clock (synchorous) Mod-16-counter and the decoding output of Mod-16-counter using logic gates gives the sequential changes of the light. These decoded outputs are fed into

transistors which consequently switch "ON" the different bulb at different intervals. Stabilized 5V d.c supply was used for the integrated circuits while 12v d.c supply was used for the bulbs.

Traffic controller system is analyzed as follows:

- 240/9V and 240/12V step-down transformer; was used as a source of power which the output from the secondary was rectified, filtered and regulated properly so that stabilized 5V and 12V d.c. supply was obtained to power the system.

- The timing pulses needed by the logic counter is generated using LM 555 timer, in an astable mode.

- Two dual JK flip-flop ICs (SN74107) counter was connected across the timer output.

- The counter output was combined together and decoded using combinational logic circuits which thus make the bulbs glow when necessary by switching the transistors respectively.

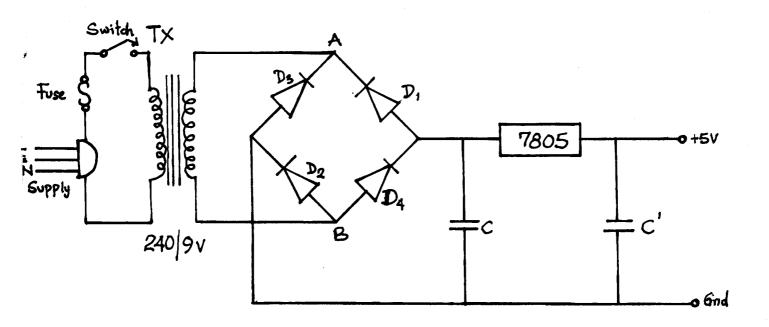

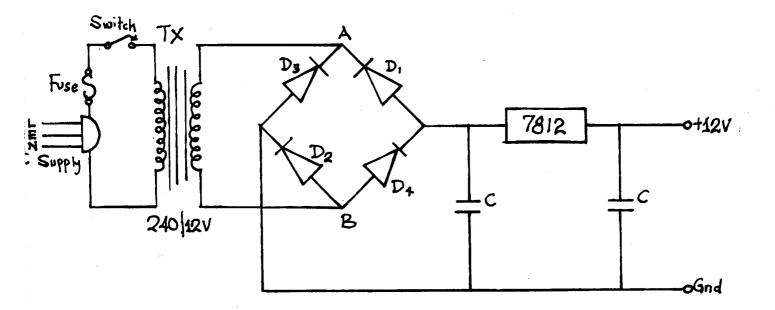

### 3.2 DESIGN OF REGULATED POWER SUPPLY

The most vital part of any electronic circuit is the source of power. Apart from the 240/9V and 240/12V a.c step down and the rectifiers, there is the need for a smoothing circuit and a stabilizing circuit. For this project, two power supply units are used, the first is the regulated 5V d.c which is used to fed the Ics and the second 12V d.c that supplies the bulbs. The circuit diagram for +5V and +12V were shown in Figures 3.20 and 3.21 respectively.

Fig 3.20: 5V d.c. regulated power supply circuit

Fig. 3,21: 12 d.c Regulated Power Supply Circuit

When 240V a.c is fed into the input of the transformer, the transformer steps 240V down to its rating. Like in 240/9V, the transformer steps 240V down to 9V a.c. This 9V is then passed through a Bridge rectifier. This bridge rectifier circuit has four diodes, diagonally opposite pairs of which conduct simultaneously so that when point A is positive with respect to B, diodes D1 and D2 conduct, D3 and D4 being reverse biased. When point B is positive with respect to point A, diodes D3 and D4 conduct, while D1 and D2 are reverse biased as shown in Figures **3**.20 and 3.21.

A undirectional currents and voltages were obtained from the rectifying the ough still contains some degree of alternating currents and voltages along its d.c counterpart.

# 3.2.1 SMOOTHING THE RECTIFIED A.C SUPPLY

Capacitors play an important role in this section of the circuitry shown in figures 3.20 and 3.21 especially for the smoothening activities in the power supply circuits and also to determine the frequencies of the timing pulses in the timer circuit. Though using Bridge rectifier, as used in the design would have reduced the a.c component to the minimum level but there is still a need to smoothing the rectifier's output. The capacitors (C) in Figures 3.20 and 3.21 was used as a filter, thus giving an output that is steady and devoid of the remaining a.c components. This capacitor is called "reservoir Capacitor"

and the other capacitor C' is improving the quality of the output of the regulators.

#### 3.2.2 STABILIZING THE SUPPLY

As the load current increases from zero to infinity, the d.c output voltage from an ordinary power supply units decreases from maximum level to zero i.e load current is inversely proportional to the output voltage (V=IR). So, due to dropping in output voltage as a result of increase in load current, there is need to stabilize the voltage supply and this explains the reason for the use of the AN7805 voltage regulation as shown in Figure 3.20 and this AN7805 regulator provides protection against overloading and overheating of the circuit components.

Figure 3.20 is the circuit diagram of the regulated 5V that supplies ICs while Figure 3.21 is also the circuit diagram of regulated 12V which supply power to the bulbs.

3.2.3 USED COMPONENTS AND VALUES AN7805 5V voltage regulator. KIA7812 12V voltage regulator. 0.022 micro Farad ceramic capacitor (x2) IN 4001 diode (x8) 2200 micro Farad/25V d.c Electrolytic capacitor 6800 micro Farad/25V d.c Electrolytic capacitor=r 240/9V a.c Transformer.

240/12V a.c Transformer. switch (x2) 100 mA Fuse.

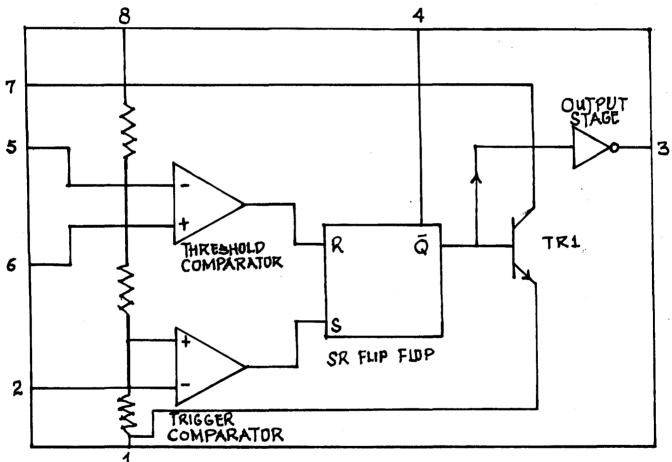

# 3.3 THE PULSE GENERATOR:

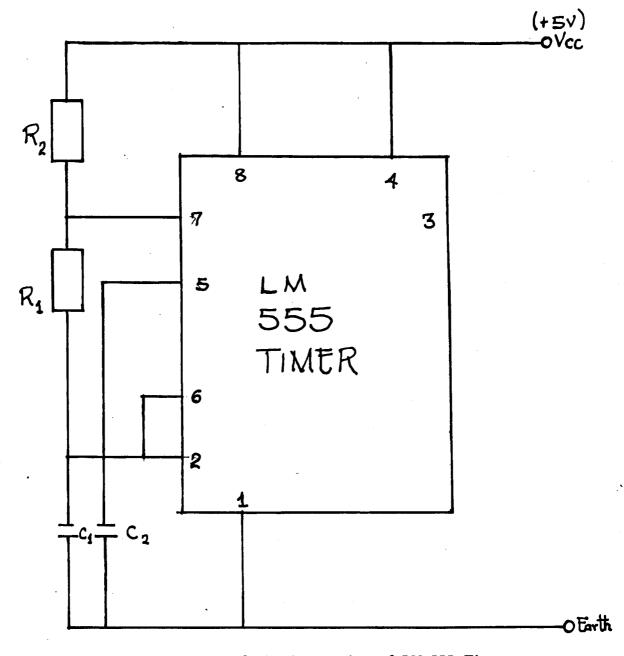

LM 555 Timer IC was used in an astable mode to generate the timing pulses needed by the logic counter. Basically, it consist of an SR flip-flop which set and reset are each controlled by an operational Amplifiers (used as voltage comparators). An eight pin DIL IC operates from supply rail voltages of (3-15)V and since Transistor-Transistor Logic (TTL) logic family was used in this project design, the timer IC in this case was operated from a d.c supply of 5V. The interval block diagram of LM 555 Timer is shown in Figure 3.30

| Pin 1: | Ground        | Pin 5: | Control Voltage |

|--------|---------------|--------|-----------------|

| Pin 2: | Trigger Input | Pin 6: | Threshold       |

| Pin 3: | Output        | Pin 7: | Discharge       |

| Pin 4: | Reset         | Pin 8: | Power Supply    |

The figure 3.31 shows block diagram of the pin connection of LM 555 Timer when connected in an astable mode.

Trigger (Pin 2) was connected to the Threshold (Pin 6) as shown in Figure 3.31. R1, R2, C1 and C2 are external components. Initially C1 charges up through R1 and R2 and when the voltage across it just more than 2/3 Vcc, the output from the Threshold comparator goes "high", and resets the flip-flop. When Q goes "high", there is existence of two outputs, firstly the output from the IC pin 3 goes low (since inverting output buffer is incorporated so that a considerable current can be source to, or sunk from, a load). Second, transistor (Tr1) switches ON (since its base is now +ve) allowing to discharge through it and R1.

Now when the voltage across C1 is below  $1/_3$  Vcc, the output from the Trigger comparator goes "high" and sets the flip-flop. Q will thus go "low", also with two outputs. First, the output from the IC goes "high" and second, the transistor (Tr1) turns OFF (since its base is no longer +ve) so letting C1 charge up to 2/3 Vcc again through R1 and R2, as it did at the beginning. And this cycle is then repeated continuously giving an oscillatory, output with a rectangular wave from which is "high" while C1 is charging and "low" while it discharge.

Generally, the output is 'high' for longer period than it is 'low', since C1 charges through two resistors R1 and R2, but

discharges only through R1. LM 555 Timer using in an astable mode has one important factor which is the connection of reset (Pin 4) which is the "direct reset" for the flip-flop to +Vcc (+5V). If the voltage falls below approximately 0.7V, the astable will stop. Also, since the 555 Timer is used as an astable, the control voltage (Pin 5) was connected via 0.01 micro Farad capacitor to the neutral (0V).

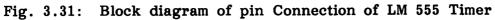

LM 555 Timer wave form is shown in Figure 3.32.

Fig. 3.32: Waveforms of the LM 555 Timer

The voltage across the capacitor when charging and discharging was given as calculated below:

i. When charging, the charging period is t, and calculated as follows;

$2/3Vcc = Vcc - [Vcc - Vcc/3] \exp [-t/C1(R1 + R2)]$  ----(a)  $2/3Vcc = Vcc - 2/3Vcc \exp [-t/C1(R1+R2)]$  -----(b) dividing through by Vcc,

$2/3 = 1 - 2/3 \exp [-t/C1(R1+R2)]$

$2/3 \exp [-t/C1 (R1+R2)] = 1 - 2/3 = 1/3$

multiplying through by 3/2,

$\exp [-t/C1(R1 + R2)] = 1/2$

$2 = \frac{1}{\exp [-t/C1(R1 + R)]}$ log 2 = t/C1(R1 + R2) t = c!(R1 + R2) log 2

t = 0.693 C1(R1 + R2) ----- (b)

ii. When discharging, the discharge period is td, and calculated as follows;

2/3Vcc = Vcc - [Vcc - Vcc/3]exp[-td/C1R1]

2/3Vcc = Vcc - [2/3Vcc]exp[-td/C1R1]

$1/3Vcc = 2/3Vcc \exp[-td/C1R1]$

dividing through by Vcc,

$1/3 = 2/3 \exp[-td/C1R1]$

$1/2 = \exp [-td/C1R1]$

$2 = \exp [td/C1R1]$

td = C1R1 log 2 td = 0.6933C1R1 ----- (c)

The period time 'T' of the output wave form is thus given by,

T = t + td T = 0.693C1[R1 + R2] + 0.693C1R1 T = 0.693C1R1 + 0.693C1R1 + 0.693C1R2T = 0.693C1[2R1 + R2] ------(d)

The operating frequency of the output waveform is,

$$F = \frac{1}{T} = \frac{1}{0.693C1(2R1 + R2)}$$

$$= \frac{1.44}{C1(2R1 + R2)}$$

Hz ------ (e)

In this traffic light controller design, the period of each pulse was chosen to be 2 seconds, the capacitor's value was chosen to be 330 micro Farad and R2 was chosen to be 1K ohm.

From equation (d),

T = 0.693C1(2R1 + R2)

where T = 2 secs, C = 330 micro Farad and R2 = 1 K ohm.

$2 = 0.693 \times 330 \times 10^{-6} (2R1 + R2)$

$2 = 0228.69 \times 10^{-6} (2R1 + 10^3)$

$2 = 0.22869 + 457.38 \times 10^{-6} R1$

$1.77131 = 457.38 \times 10^{-6} R1$

$$R1 = \frac{1.77131}{457.38 \times 10^{-6}} = \frac{1.77131}{457.38} \times 10^{-6}$$

Therefore,

$$R1 = \frac{1.77131}{457.38} \times 10^{6} \text{ ohm} = 3873 \text{ ohm}.$$

Which implies that,

R1 is approximated to 4K ohm.

Since R1 = 4K ohm, this gives the opportunity of using 10K ohm variable resistor in the design.

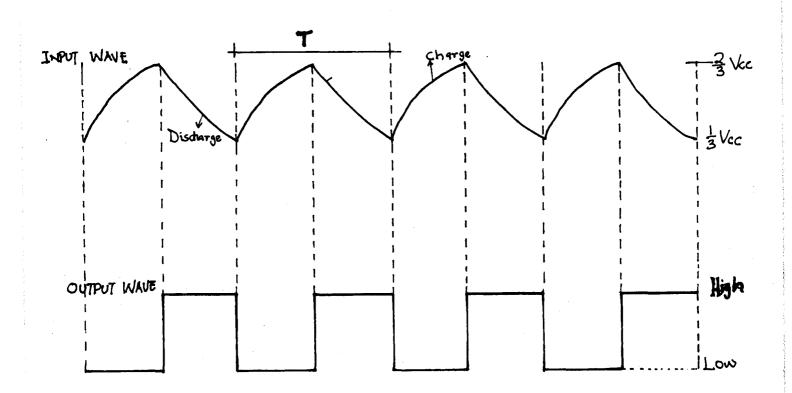

#### 3.4 MODULOS -16- COUNTER DESIGN USING JK FLIP-FLOP

Electric counters are digital instrument that can be used to perform many functions like in data handling and control, counting the number of pulses in a controlled time interval, or alternatively the time interval between the pulses.

Synchronous (clock) counter and Asynchronous (ripple) counter are two types of digital counters.

#### A. ASYNCHRONOUS COUNTER

In Asychronous counter, the output of the last flip-flop, in a four binary counter will not change until four flip-flop propagation delays after a positive edge of the input clock (i.e the effect of a clock pulse ripples down through the chain of the

flip-flops and the outputs are not directly in synchronization with the clock).

There are some advantages and disadvantages in this type of counter;

i. Advantage;

- Inexpensive.

ii. Disadvantage;

- Generation of unwanted spikes during the transition from the first stage through the time at which the first flipflop in a chain changes its output stage.

#### B. SYNCHRONOUS COUNTER

In this type of counter, all the flip-flops are directly clocked at the same time by the input clock thereby changing their output simultaneously. and this is the only advantage that clock counter is having over its ripple counterparts.

Modulo -16- counter is a counter that returns to its initial stage after 16 cycles of the input waveform.

The first step taken in Mod -16- Synchronous counter design is the construction of the basic transition table for flip-flop use in the design as shown in Figure 3.40.

| J | К | Q <sup>n+1</sup> |

|---|---|------------------|

| 0 | 0 | Q <sup>n</sup>   |

| 0 | 1 | 1                |

| 1 | 0 | 0                |

| 1 | 1 | Q <sup>n</sup>   |

Fig. 3.40: Next state table for JK flip-flop.

where  $Q^{n+1}$  = The Q output after the clock transition.

$Q^n$  = The Q output before the clock pulse occurred.

JK flip-flop is used because it is a universal one that can be connected as D or T - types.

In this particular Mod -16- counter design using synchronous JK flip-flop, if <u>J=1 and K=0</u>, the Q output <u>becomes 1</u> at the next clock transition. If <u>J=0 and K=1</u>, the Q outputs are 0 (i.e J=K=0) when a clock transition occurs, the Q output remains the same,  $Q^{n+1} = Q^n$  and finally, if J = 1 and K = 1 (i.e J=K=1), the Q output assumes the opposite state at the clock transition,  $Q^{n+1}=\overline{Q}n$  and this opposite state at the clock transition is referred to as "Toggling".

Basic transition table for the JK flip-flop and counter state table were shown in Figures 3.41 and 3.42 respectively.

| ORIGINAL STATE (Q <sup>n</sup> ) | NEXT STATE Q <sup>n+1</sup> | J | К |

|----------------------------------|-----------------------------|---|---|

|                                  |                             |   |   |

| 0                                | 0                           | 0 | x |

| 0                                | 1                           | 8 | x |

| 1                                | 0                           | 0 | 1 |

| . 1                              | 1                           | Ŋ | 0 |

|                                  |                             |   |   |

|                                  |                             |   |   |

|                                  |                             |   |   |

|                                  |                             |   |   |

|                                  |                             |   |   |

X = "dent care"

Fig. 3.41 Transition table for JK flip-flop

| DECIMAL | PRESENT        | NEXT             |            |            | <br>  |          |

|---------|----------------|------------------|------------|------------|-------|----------|

|         | STATE          | STATE            |            |            |       |          |

|         | Q <sup>n</sup> | Q <sup>n+1</sup> |            |            |       |          |

|         |                | WXYZ             | Jw Kw      | Jx Kx      | Ју Ку | Jz Kz    |

|         | WXYZ           |                  |            |            |       |          |

| 0       | 0 0 0 0        | 0001             | 0 X        | 0 X        | 0 X   | 1 X      |

| 1       | 0001           | 0010             | 0 X        | 0 X        | 1 X   | X 1      |

| 2       | 0010           | 0011             | 0 X        | 0 X        | x o   | 1 X      |

| 3       | 0 0 1 1        | 0100             | 0 X        | 1 X        | X 1   | X l      |

| 4       | 0 1 0 0        | 0 1 0 1          | 0 X        | X 0        | 0 X   | 1 X      |

| 5       | 0 1 0 1        | 0110             | 0 X        | X O        | 1 X   | X 1      |

| 6       | 0 1 1 0        | 0111             | 0 X        | <b>X</b> 0 | x o   | 1 X      |

| 7       | 0 1 1 1        | 1000-            | 1 X        | X l        | X 1   | X 1      |

| 8       | 1000           | 1001             | X 0        | 0 X        | 0 X   | 1 X      |

| 9       | 1001           | 1010             | <b>X</b> 0 | 0 X        | 1 X   | хı       |

| 10      | 1010           | 1011             | <b>X</b> 0 | 0 X        | x o   | 1 X      |

| 11      | 1011           | 1 1 0 0          | <b>X</b> 0 | 1 X        | X 1   | X 1      |

| 12      | 1 1 0 0        | 1 1 0 1          | <b>X</b> 0 | X O        | o x   | 1 X      |

| 13      | 1101           | 1110             | X 0        | X O        | ı x   | X 1      |

| 14      | 1110           | 1111             | X O        | x o        | x o   | 1 X      |

| 15      | 1111           | 0 0 0 0          | X 1        | X l        | X 1   | X 1      |

|         |                |                  |            |            |       |          |

|         |                |                  |            |            |       |          |

|         |                |                  |            |            |       | <u> </u> |

Fig. 3.42: Modulo -16- counter state table

Further simplification of the design is being carried out use Karnaugh Map as shown in Figure 3.43.

# I. FOR Jw:

| WX        | 00  | 01 | 10 | 11 |

|-----------|-----|----|----|----|

| YZ        |     |    |    |    |

| 00        | 0   | 0  | х  | х  |

| 01        | 0   | 0  | х  | х  |

| 10        | 0   | 1  | X  | х  |

| 11        | 0   | 0  | х  | X  |

| $J_w = F$ | BCD |    |    |    |

II. FOR Jx:

| 00 | 01 | 11                | 10                      |

|----|----|-------------------|-------------------------|

|    |    |                   |                         |

| 0  | х  | х                 | 0                       |

| 0  | х  | х                 | 0                       |

| 1  | X  | X                 | 1                       |

| 0  | х  | х                 | 0                       |

|    | 0  | 0 X<br>0 X<br>1 X | 0 X X<br>0 X X<br>1 X X |

III. FOR Jy:

| WX<br>YZ                 | 00 | 01 | 11 | 10 |

|--------------------------|----|----|----|----|

| 00                       | 0  | 0  | 0  | 0  |

| 01                       | 1  | 1  | 1  | 1  |

| 10                       | x  | х  | х  | x  |

| 11<br>J <sub>y</sub> = D | х  | х  | х  | X  |

IV. FOR Jz:

| WX                       | 00 | 01 | 11 | 10 |

|--------------------------|----|----|----|----|

| YZ                       |    |    |    |    |

| 00                       | 1  | 1  | 1  | 1  |

| 01                       | x  | х  | х  | x  |

| 10                       | x  | х  | х  | X  |

| 11<br>J <sub>z</sub> = 1 | 1  | 1  | 1  | 1  |

FOR Kw:

| WX | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| YZ |    |    |    |    |

| 00 | х  | х  | 0  | 0  |

| 01 | х  | х  | 0  | 0  |

| 10 | x  | X  |    | 0  |

| 11 | x  | x  | 0  | 0  |

FOR Kx:

| WX | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| YZ |    |    |    |    |

| 00 | х  | 0  | 0  | х  |

| 01 | х  | 0  | 0  | x  |

| 10 | X  | 1  | 1  | ×  |

| 11 | x  | 0  | 0  | х  |

$K_{\star} = C$

FOR KY:

| WX<br>YZ | 00 | 01 | 11 | 10     |

|----------|----|----|----|--------|

| 00       | x  | х  | х  | х      |

| 01       | X  | x  | x  | x      |

| 10       | 1  | 1  | 1  | 1      |

| 11       | 0  | 0  | 0  | 0      |

| K, = 1   | D  |    |    | لعيهوا |

FOR Kz:

| WX<br>YZ                 | 00 | 01 | 11 | 10 |

|--------------------------|----|----|----|----|

| 00                       | (x | x  | x  | X  |

| 01                       | 1  | 1  |    |    |

|                          |    |    | 1  | 1  |

| 10                       | 1  | 1  | 1  | 1  |

| 11<br>K <sub>z</sub> = 1 | X  | X  | X  | x  |

Qz. 1QY Q× QW CLOCK INPUT 1 Q J Q J Q J Q ₽<sup>CLK</sup> FFZ CLK DCLK DCLK FFY FFW FFX ā Q | ā. Q. K K K -K Fig 3.44: Block diagram of the Synchronous Mod - 16 - counter

31

. .

## 3.5 COMBINATIONAL LOGIC CIRCUIT TRAFFIC LIGHT CONTROLLER

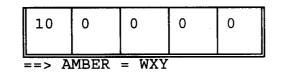

The operational of the traffic light controller is shown in the Table 3.50 using MOd -16- counter as a counting element.

| DECIMAL | W | X | Y | Z | R | A | G | PULSES (SECS) |

|---------|---|---|---|---|---|---|---|---------------|

| 0       | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 2             |

| 1       | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 2             |

| 2       | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 2             |

| 3       | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 2             |

| 4       | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 2             |

| 5       | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 2             |

| 6       | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 2             |

| 7       | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 2             |

| 8       | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 2             |

| 9       | 1 | 0 | 0 | 1 | 0 | 0 | l | 2             |

| 10      | 1 | 0 | 1 | 0 | ο | 0 | 1 | 2             |

| 11      | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 2             |

| 12      | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 2             |

| 13      | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 2             |

| 14      | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 2             |

| 15      | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 2             |

Table 3.50: Truth table of counting order.

Some boolean algebra had to be performed in order to determine which output will be decoded by the logic gate (i.e W, X, Y, Z).

$\underline{i. \text{ FOR RED:} }$   $\overline{W}\overline{X}\overline{Y}Z + \overline{W}\overline{X}\overline{Y}Z + \overline{W}\overline{X}Y\overline{Z} + \overline{W}\overline{X}\overline{Y}Z + \overline{W}\overline{X}Y\overline{Z} + \overline{W}\overline{X}\overline{Y}\overline{Z} + \overline{W}\overline{X}\overline{Y}\overline{X} + \overline{W}\overline{X}\overline{Y}\overline{X} + \overline{W}\overline{X}\overline{X} + \overline{W}\overline{X} + \overline{W}\overline{X}\overline{X} + \overline{W}\overline{X} + \overline{W} + \overline{W}\overline{X} + \overline{W}\overline{X} + \overline{W$

ii. FOR AMBER:

$WXY\overline{Z} + WXYZ$

= WXY $(\bar{Z}+Z)$

= WXY.

iii. FOR GREEN:

$W\bar{X}\bar{Y}\bar{Z} + W\bar{X}\bar{Y}Z + W\bar{X}Y\bar{Z} + W\bar{X}YZ + WX\bar{Y}\bar{Z} + WX\bar{Y}Z$

$= W\overline{X}\overline{Y}\overline{Z} + WX\overline{Y}\overline{Z} + W\overline{X}\overline{Y}Z + WX\overline{Y}Z + W\overline{X}Y\overline{Z} + W\overline{X}YZ$

$= W\overline{Y}\overline{Z}(\overline{X}+X) + W\overline{Y}Z(\overline{X}+X) + W\overline{X}Y(\overline{Z}+Z)$

$= W\overline{Y}\overline{Z} + W\overline{Y}Z + W\overline{X}Y$

$= W\overline{Y}(\overline{Z}+Z) + W\overline{X}Y$

$= W\overline{Y} + W\overline{X}Y$

$= W(\overline{Y} + \overline{X}Y)$

$= W(\bar{Y} + \bar{X})$

$= W(\bar{Y} + \bar{X})$

The output of the binary counter is then decoded with the

designed combinational logic circuit.

Karnangh Map ( a system of reducing Boolean expressions using a matrix of 1's and 0's ) can be used to simplify Boolean algebra as shown in Tables 3.51.

I. FOR RED:

| ZY          | 00             | 01 | 10 | 11             |  |

|-------------|----------------|----|----|----------------|--|

| XW          | 1              |    |    |                |  |

| 00          | 1              | 71 | 1  | 1 <sup>°</sup> |  |

| 01          | 0              | 0  | 0  | 0              |  |

| 11          | 0              | 1  | 1  | 0              |  |

| 10          | $\int_{1}^{1}$ | 1  | 1  | 1              |  |

| ==> RED = W |                |    |    |                |  |

TABLE 3.51(a)

II. FOR AMBER:

| ZY | 00 | 01 | 10 | 11 |

|----|----|----|----|----|

| xw |    |    |    |    |

| 00 | 0  | 0  | 0  | 0  |

| 01 | 0  | 0  | 0  | 0  |

| 11 | 0  | 1  | 1  | 0  |

TABLE 3.51(b)

1 <sup>1</sup>.

.

III. FOR GREEN:

| ZY<br>XW | 00 | 01 | 10 | 11 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       | 1  | 1  | 1  | 1) |

| 11       | 1  | 0  | 0  | 1  |

| 10       | 0  | 0  | 0  | 0  |

- TABLE 3.51(c)

- $= W\overline{X} + W\overline{Z} + W\overline{Y}Z$

- $= W\vec{X} + W\vec{Y}(\vec{Z}+Z)$

- $= W\overline{X} + W\overline{Y}$

- $= W(\vec{X} + \vec{Y})$ .

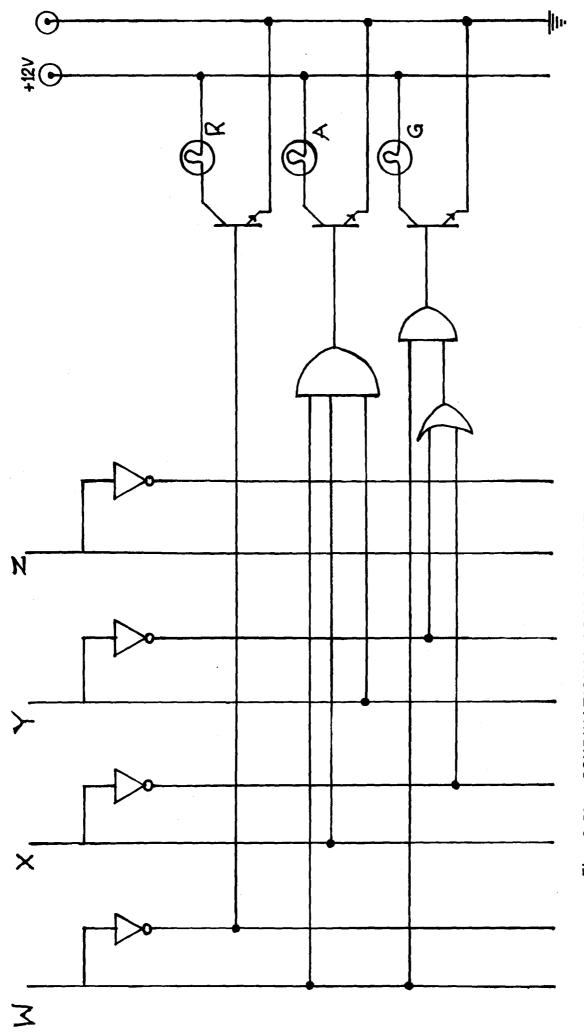

Fig. 3.52: COMBINATIONAL LOGIC CIRCUIT

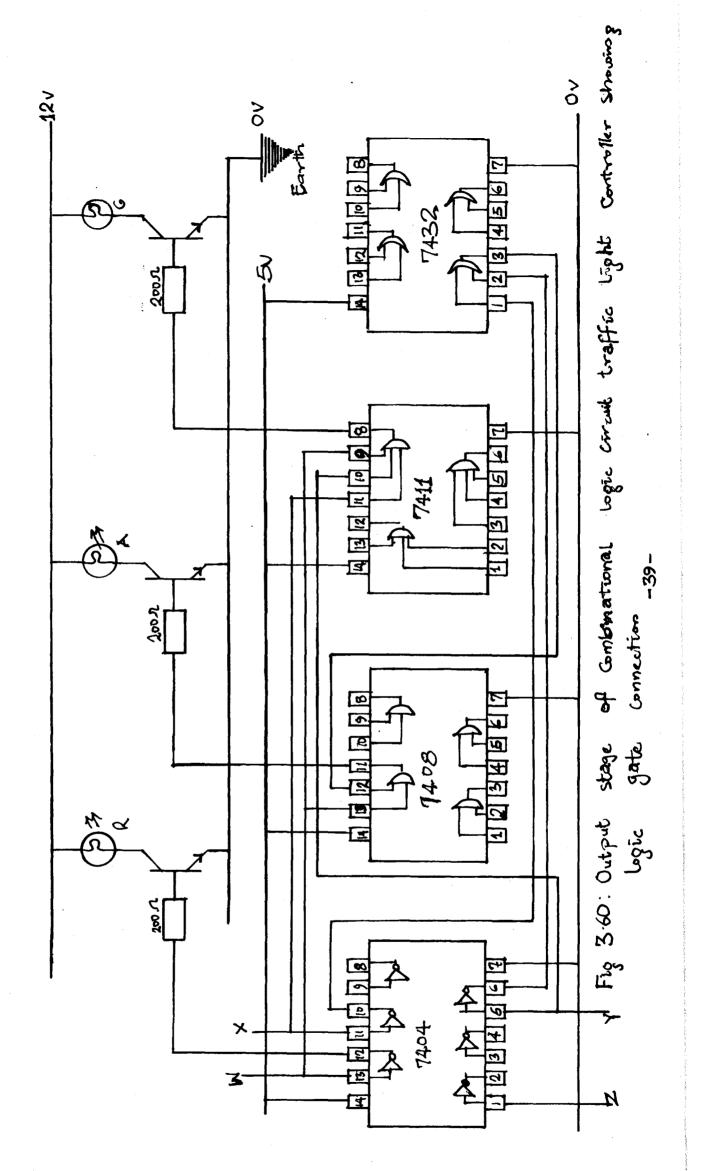

### 3.6 THE OUTPUT STAGE

Combinational Logic gates is use to combined different output of the Mod -16- counter, and the output of the gates are then connected to different transistors each. A particular final output is connected to the base of a transistor, while the ammeter of the transistor is connected to neutral line (OV) the output of the transistor is connected to bulb. The collector is then connected to one of the bulb pin, while the other bulb pin is connected to the 12 volts d.c regulated supply. Once the logic is 'high' the transistor automatically switch ON the bulb attached to it and this remains for the duration of which the logic is 'high'. Once the logic goes 'low', the bulb goes OFF.

### 3.7: COMPONENTS AND VALUES

SN 7411 (x1) Quad 3-input AND gate. SN 7432 (x1) Quad 2-input OR gate. SN 7404 (x1) Hex Inverter. SN 7408 (x2) Quad 2-input AND gate. SN 74107 (x2) Dual JK flip-flop. LM 555 Timer. Capacitor C=330 micro Farad/25V Capacitor C=0.01 micro Farad BFY52 (x3) Transistor. 12V, 5W(x3) Bulb. Resistor R1 = 4K ohm. Resistor R2 = 1K ohm.

3.8 TRAFFIC LIGHT CONTROLLER DESIGN USING MONOSTABLE

# MULTIVIBRATOR.

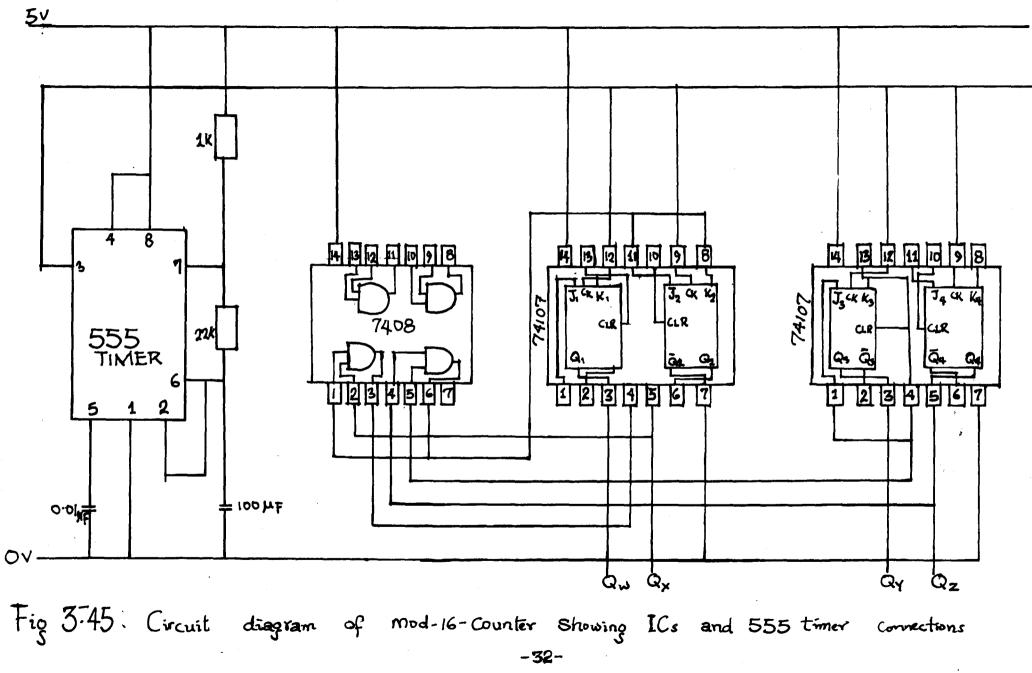

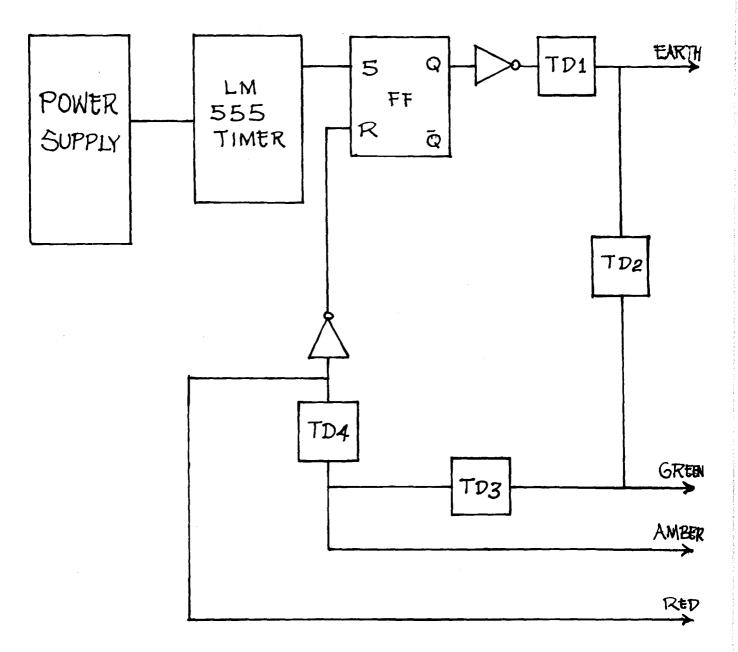

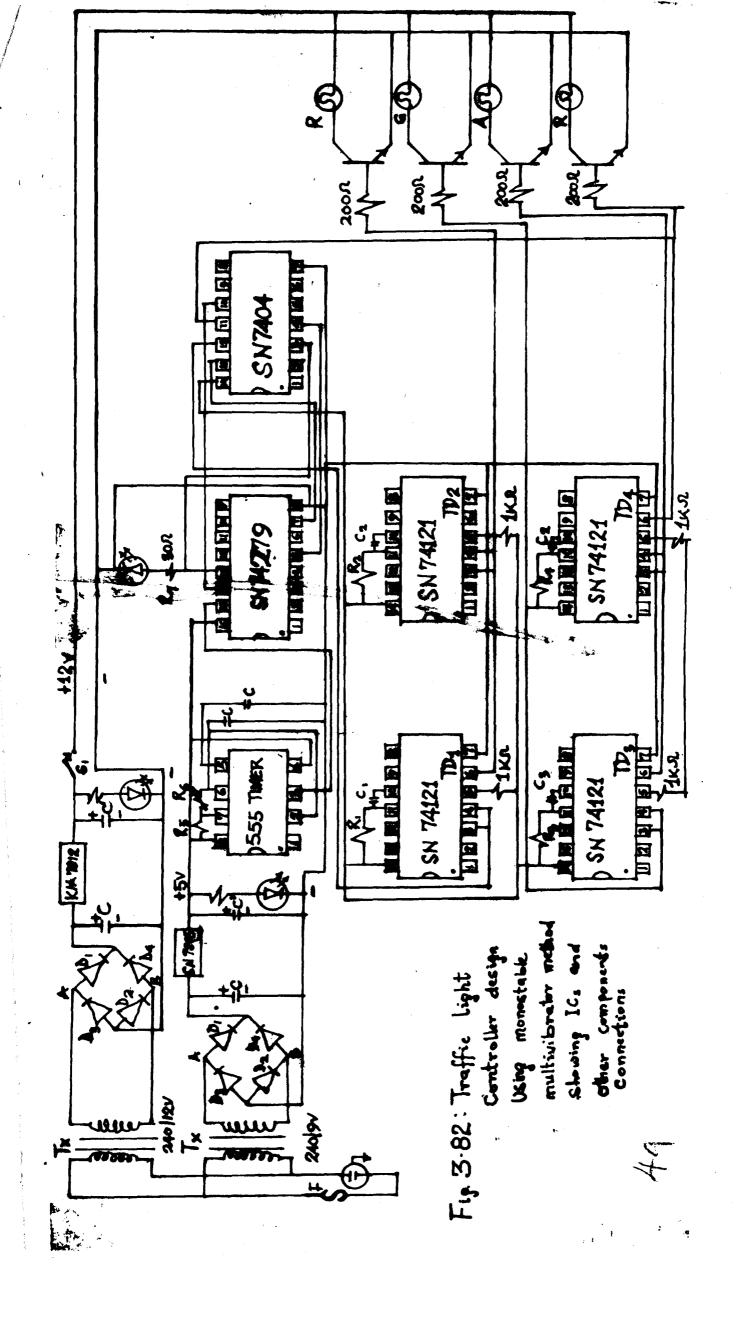

The block diagram of the light controller using Monostable multivibrator is shown in Fig. 3.80.

Fig. 3.80: Block diagram of traffic light controller using mono stable multivibrator.

The design for the power supply and the 555 Timer has been done in sections 3.2 and 3.3.

The next thing is to compute the time delay for the four multivibrators. The 555 timer here generates a signal of 1 pulse per sum of the delay times 30.3 secs.

#### 3.8.1 CALCULATION OF THE TIME DELAY

In any circuit where time delay is required, Multivibrator are mostly used. These Multivibrators are categorized into three:-

- Astable or free-running Multivibrator: which has no stable states. It switches at a rate determined by the circuit components from a state to another. It generates a continuous stream of almost square wave pulses which is used to produce timing pulses for keeping the different part of a digital system, and this is one of the importance.

- Bistable Multivibrator: this has two stable states. External trigger or clock pulses makes it to switch from one stage to another.

They are normally refereed to as memory type circuits because in any digital systems, it is used to store the binary digits of '0' (low) and '1' (high) output.

- Monostable Multivibrator: is a device that causes delay by converting a pulse of unpredicted length of time into a square pulse of predicted length (voltage). Monostable Multivibrator is

also refereed to as one shot multivibrator.

This project work, for the time delay, Monostable (one shot) Multivibrator is use. And SN74121 type is used because it is a non-triggable one, which when stimulated, releases its pulse, but however locks any further incoming information until the full pulse duration and can be express mathematically as follows:

T = 0.7RC

where C = Capacitor value.

R = Resistor value.

T = Time duration of the pulse.

Various calculations carried out are as follows:

(a) <u>FOR RED</u>:The first signal means "wait don't cross" and the time delay(TD1) is calculated as shown below:

When R = 15K ohm and C = 470 micro Farad

T = 0.7 RC

$T = 0.7 \times 15 \times 10^3 \times 470 \times 10^{-6}$

= <u>4.9 secs</u>

==> TD1 = 4.9 secs

(b) <u>FOR GREEN</u>:

Green signals means "Cross" and the delay time (TD2) is calculated as follows:

when R = 30K ohm and C = 470 micro Farad.

T = 0.7RC

$T = 0.7 \times 30 \times 10^3 \times 470 \times 10^{-6}$

= 9.9 secs.

==> TD2 = <u>9.9 secs</u>

(c) <u>FOR AMBER</u>:

V

4

Amber signal means "Get ready to stop crossing" and the delay time (TD3) is calculated as shown:

when R = 9K ohm and C = 470 micro Farad.

T = 0.7RC  $T = 0.7 \times 9 \times 10^{3} \times 470 \times 10^{-6}$  = 3.0 secs.= > TD3 = 3.0 secs

(d) <u>FOR RED</u>:

The second red signal means "Stop crossing" and the delay time is calculated as:

T = 0.7RC

$T = 0.7 \times 38 \times 10^3 \times 470 \times 10^{-6}$

= 12.5 secs.

==> TD4 = <u>12.5 secs</u>

Total delay time =  $T_{ud}$  = TD1 + TD2 + TD3 + TD4

= 4.9 + 9.9 + 3.0 + 12.5

= <u>30.3 secs</u>

Choosing a particular 470 micro Farad for the total delay time  $({\rm T}_{\rm ud})\,,$  the average resistor value is:

=  $T_{td}$  = 0.7RC 30.3 = 0.7R x 470x10<sup>-6</sup> R = 92.1K ohm R = <u>92K ohm</u>

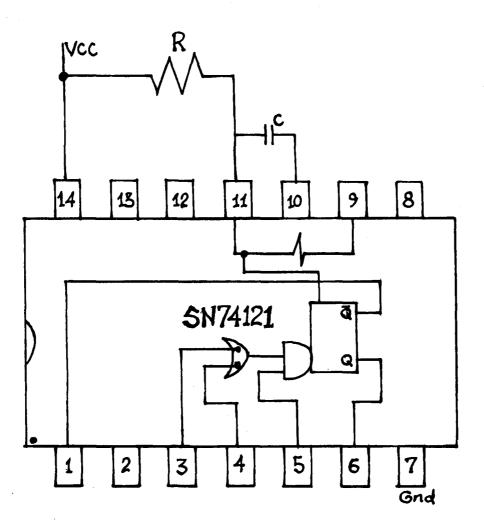

The connection mode of the resistor and capacitor on SN74121 monostable multivibrator with SN74121 internal block diagram is shown in Figure 3.81.

Fig. 3.81: Connection Mode and Internal Block Diagram of SN 74121 Monostable Multivibrator.

Fig. 3.81 Connection mode and interval block diagram of SN74121 monostable Multivibrator.

In this project work, the other Transistor Logic family used are:-

- SN7408 AND gate.

- SN7404 NOT gate.

### CHAPTER FOUR

### COMPARATIVE EVALUATION OF THE DESIGNS

As we have earlier stated in chapter two, the comparative evaluation of the two designs (i.e using combinational Logic method and Monostable Multivibrator method) shall now be carried out using the following criteria;

i. Production cost.

ii. Reliability

iii. Space

iv. Speed.

#### 4.1 PRODUCTION COST

Production cost or bill of quantity for combinational Logic Circuit method of design and Monostable Multivibrator method design are shown in Tables 4.10 and 4.11 respectively.

# COST ESTIMATE TABLES

| s/N       | ITEM                  | ITEM    | UNIT   | QUANTITY | AMOUNT |

|-----------|-----------------------|---------|--------|----------|--------|

|           |                       | LABEL   | COST N |          | • •    |

| 1.        | TIMER (PULSE          | LM555CN | 40     | 1        | 40     |

|           | GENERATOR)            |         |        |          |        |

| 2.        | JK FLIP-FLOP          | SN74107 | 120    | 2        | 240    |

| 3.        | 2-INPUT AND GATE      | SN7408  | 110    | 2        | 220    |

| 4.        | NOT GATE              | SN7404  | 80     | 1        | 80     |

| 5.        | 3-INPUT AND GATE      | SN7411  | 110    | 1        | 110    |

| 6.        | 2-INPUT OR GATE       | SN7432  | 110    | 1        | 110    |

| 7.        | DIODES                | IN4001  | 5      | 8        | 40     |

| 8.        | LIGHT EMITTING DIODES | -       | 10     | 2        | 20     |

| 9.        | TRANSISTOR            | BFY52   | 20     | 3        | 60     |

| 10        | VERO BOARD            | -       | 100    | l        | 100    |

| <b>31</b> | SOLDERING IRON        | -       | 1.5M   | -        | 50     |

| 12        | CONNECTION WIRE       | -       | 30M    | -        | 150    |

| .13       | VOLTAGE REGULATOR     | SN7805  | 50     | 1        | 50     |

| 11        | VOLTAGE REGULATOR     | KIA7812 | 50     | 1        | 50     |

|           |                       |         |        |          |        |

|           |                       |         |        |          |        |

| •         |                       |         |        |          |        |

|           |                       |         |        |          |        |

|           |                       |         |        |          |        |

| L         |                       |         |        |          |        |

| S/N | ITEM        | RATING  | UNIT<br>COST(취) | QTY   | AMOUNT |

|-----|-------------|---------|-----------------|-------|--------|

| 15  | TRANSFORMER | 240/9V  | 150             | 1     | 150    |

| .16 | TRANSFORMER | 240/12V | 150             | 1     | 150    |

| ז 1 | CAPACITORS  |         |                 |       |        |

| . i | C1          | 6800UF  | 10              | 1     | 10     |

| 11  | C1 AND C4   | 0.02UF  | 10              | 2     | 20     |

| iii | СЗ          | 2200UF  | 10              | 1     | 10     |

| iv  | C5          | 330UF   | 10              | 1     | 10     |

| · v | C6          | 0.01UF  | 10              | 1     | 10     |

| .18 | RESISTOR    |         |                 |       |        |

| i   | R1          | 4K OHM  | 5               | 1     | 5      |

| i i | R2          | 1К ОНМ  | 5               | 1     | 5      |

| iii | R3          | 50 OHM  | 5               | 1     | 5      |

| iv  | R4          | 170 OHM | 5               | 1     | 5      |

| 19  | FUSE        | 100mA   | 20              | 1     | 20 ·   |

| 20  | TUBLER BULB | 12V 5W  | 30              | 3     | 90     |

| i.  |             |         |                 |       |        |

| ii  |             |         |                 |       |        |

| •   |             |         |                 |       |        |

| ii  |             |         |                 |       |        |

| i   |             |         |                 |       |        |

| iv  | 1           |         |                 |       |        |

|     |             |         |                 |       |        |

| 19  |             |         |                 |       |        |

| 20  |             |         |                 |       |        |

|     |             |         |                 | TOTAL | 1810   |

| s/ | ITEM                  | ITEM    | UNIT   | QUANTITY | AMOUNT         |

|----|-----------------------|---------|--------|----------|----------------|

| N  |                       | LABEL   | COST N |          | Τ <del>Ν</del> |

| 1. | TIMER (PULSE          | LM555CN | 40     | 1        | 40             |

|    | GENERATOR)            |         |        |          |                |

| 2. | NOT GATE              | SN7404  | 800    | 1        | 80             |

| 3. | MONOSTABLE            |         | 1      |          |                |

|    | MULTIVIBRATOR         | SN74121 | 90     | 4        | 360            |

| 4. | <b>-</b>              | SN74279 | 80     | 1.       | 80             |

| 5. | DIODES                | IN4001  | 5      | 8        | 40             |

| 6. | LIGHT EMITTING DIODES | -       | 10     | 3        | 30             |

| 7. | CONNECTION WIRE       | -       | 30/M   | -        | 90             |

| 8. | VERO BOARD            | -       | 100    | 1        | 100            |

| 9. | SOLDERING WIRE        | -       | 1.5M   | -        | 20             |

| 10 | VOLTAGE REGULATOR     | SN7805  | 50     | 1        | 50             |

| 41 | VOLTAGE REGULATOR     |         | 50     | 1        | 50             |

| 12 | TRANSISTOR            | KIA7812 | 20     | 3        | 60             |

| •  |                       | BFY52   |        |          |                |

| 12 |                       |         |        |          |                |

|    |                       |         |        |          |                |

| S/ | ITEM                  | RATING  | UNIT   | QUANTITY | AMOUN          |

| N  |                       |         | COST   |          | Т              |

| S/N          | ITEM            | RATING  | UNIT<br>COST(취) | QTY | AMOUNT |

|--------------|-----------------|---------|-----------------|-----|--------|

| 13           | TRANSFORMER     | 240/9V  | 150             | 1   | 150    |

|              | TRANSFORMER     | 240/12V | 150             | 1 · | 150    |

| 14           | CAPACITORS      |         |                 |     |        |

| 15           | C1              | 6800UF  | 10              | 1   | 10     |

| 1            | C1 AND C4       | 0.02UF  | 10              | 2   | 20     |

| 'ii          | С3              | 2200UF  | 10              | 1   | 10     |

| i <b>ii</b>  | C5              | 330UF   | 10              | 1   | 10     |

| iv           | C6              | 0.01UF  | 10              | 1   | 10     |

| • <b>v</b>   | C11,C12,C13,C14 | 4.70UF  | 10              | 4   | 40     |

| 16           | RESISTORS       |         |                 |     |        |

| i            | R1              | 15K OHM | 5               | 1   | 5      |

| ii           | R2              | зок онм | 5               | 1   | 5      |

| įii          | R3              | 9К ОНМ  | 5               | 1   | 5      |

| iy           | R4              | З8К ОНМ | 5               | 1   | 5      |

| v            | R5              | IK OHM  | 5               | 1   | 5      |

| . <b>v</b> i | R6              | 4K OHM  | 5               | 1   | 5      |

| vii          | R7              | ЗОК ОНМ | 5               | 1   | 5      |

| 17           | FUSE            | 100mA   | 20              | 1   | 20     |

| 18           | TUBLER BULB     | 12V 5W  | 30              | 4   | 120    |

|              |                 |         |                 |     |        |

| •            |                 |         |                 |     |        |

| ii           |                 |         |                 |     |        |

| i            |                 |         |                 |     |        |

| iv           |                 |         |                 |     |        |

| •            |                 |         |                 |     |        |

| v.           |                 |         |                 |     |        |

|              |                 |         |                 |     |        |

### 4.2 <u>RELIABILITY</u>

The term reliability describes the security of a system. It is difficult to evolve a definition satisfactorily in all circumstances, the following meets most requirements: Reliability is also the characteristic of a component or of a system which may be expressed or defined by the probability that a device or system performing its function adequately, for the period of time intended under stated conditions, frequency of failure and not on the failure probability alone.

Reliability concept has always been associated, in a good qualitative way, with good design, endurance, consistuent quality and dependability. In recent years, however, the much greater complexity of electrical and electronic equipment and seriousness of a failure in the system has made it necessary to attempt not only to improve the reliability of equipment but also to asses it in qualitative terms.

This assessment of reliability is not a simple matter and it will be appreciated that the achievement of high reliability is an aim in which many people must be involved. The component manufacturer, the designers, the production team, the test and quality control Engineers, the installation Engineers and the customers must all contribute to this aim, and it is the objective of this chapter to indicate some of the consideration which are involved.

For some devices and systems, reliability is expressed per unit of time, whereas reliability is stated per unit of use for others.

During the useful life of an electronic product, the failure rate denoted by "X" is approximately constant and is the number of failure per unit time and is a useful measure of a system reliability. The reciprocal of the failure rate is known as the "Mean time" Between Failures (MBTF) which is usually stated in hours. Where failure rate ( $\lambda$ ) are constants, one quantitative measure of reliability is this Mean Time Between Failures (MBTF). A filament lamp for example might have an expected life of 3000hrs.

Reliability generally, in the sense just defined varies over time and is stated as a reliability function, R(t) which gives the probability that an item will function without over time (t).

The value of R(t) can be found in principle for life trails on a sample of items sufficiently large to give statistically valid resulted. The sample of items is tested to failure and the proportion of failed items is plotted as a function of time. The result is called the life time distribution function, F(t) which is the probability function.

Since the proportion of failed items can not decrease, the slope of F(t) is never negative. F(t) can also be interpreted as the proportion of items life less than or equal to t. Then 1-F(t) is the proportion of items with exceeding t, which is also the probability that an item will function without failure over time t or R(t).

### 4.2.1 IMPORTANCE OF RELIABILITY

Reliability is important because human lives and properties depends on correct function of either electrical or electronics system in their surrounding. The failure results in huge financial losses and a times loss of life. This reliability importance serves as a guarantee and invoke competition among manufacturers. Customers requirement also need to be satisfied.

The reliability of the designed system (i.e Combinational Logic Circuit design and Monostable Multivibrator design methods) is calculated using tables 4.20 and 4.21

Reliability  $[R(t)] = e^{-\hat{\eta} i n t}$  ----- (i) where,

$1/w^{6}hr = w^{6}hr^{-1} = Constant failure rate.$

jn = total failure rate

R(t) = reliability at time t

t = time

hr = hour

C = typical component

n = normal condition

j = number of component

k = number of sampled component

$\lambda = \Sigma \lambda Cljn + c2jnj + \dots + \lambda Ckjn$

t = 168 hrs  $R(t) = e^{-\hat{A}jnt} = R(168) = e^{-\hat{A}jn(168)}$  ----- (ii)

From the table 4.20, the reliability for combinational Logic Circuits design is calculated as follows:

$\mathbf{\hat{A}jn} = [14.40 + 20.00 + 0.20 + 1.60 + 1.00 + 5.10 + 0.345]/10^{6}hr$   $R(168) = e^{-} 42.65 \times 168 \times 10^{-6}hr^{-1}$   $= e^{-} 4.265 \times 10^{-5} \times 168$  = 0.933

From table 4.21, the reliability for Monostable Multivibrator method of design is calculated as follows:

$R(t) = e^{-i \pi} = R(168) = e^{-i \pi} (168)$   $\hbar jn = [24.00 + 22.00 + 0.18 + 5.20 + 1.00 + 6.80 + 0.255]/10^{6} hr$   $R(168) = e^{-59.44 \times 10^{-6}} \times 168$   $= e^{-5.994 \times 10^{-5}} \times 168$  = 0.91

Tables below shows the failure rate of electronic components in normal conditions (t=t20°C):

| s/ | COMPONENTS               | QUANTITY | <b>Å</b> X10 <sup>-6</sup> hr <sup>-1</sup> | TOTAL                                        |

|----|--------------------------|----------|---------------------------------------------|----------------------------------------------|

| N  |                          |          |                                             | <b>ð</b> JX10 <sup>-6</sup> hr <sup>-1</sup> |

| 1. | CAPACITORS               | 06       | 2.40                                        | 14.40                                        |

| 2. | DIODES                   | 10       | 2.00                                        | 20.00                                        |

| 3. | INTEGRATED CIRCUITS (IC) | 10       | 0.02                                        | 0.2                                          |

| 4. | RESISTORS                | 04       | 0.40                                        | 1.60                                         |

| 5. | TRANSFORMERS             | 02       | 0.50                                        | 1.00                                         |

| 6. | TRANSISTORS              | 03       | 1.70                                        | 5.10                                         |

| 7. | CONNECTION WIRE          | 23       | 0.015                                       | 0.35                                         |

|    | TOTAL                    |          |                                             | 42.65                                        |

|    |                          |          |                                             |                                              |

Table 4.20: Failure rate of electronics components in normal condition (t=t20°C) for Combinational Logic Circuit design method.

| s/       | COMPONENTS               | QUANTITY | <b>Å</b> X10 <sup>-6</sup> hr <sup>-1</sup> | TOTAL                                        |

|----------|--------------------------|----------|---------------------------------------------|----------------------------------------------|

| N        |                          |          |                                             | <b>∂</b> JX10 <sup>-6</sup> hr <sup>-1</sup> |

| 1.       | CAPACITORS               | 10       | 2.40                                        | 24.00                                        |

| 2.       | DIODES                   | 11       | 2.00                                        | 22.00                                        |

| 3.       | INTEGRATED CIRCUITS (IC) | 9        | 0.02                                        | 0.18                                         |

| 4.       | RESISTORS                | 13       | 0.40                                        | 5.20 ·                                       |

| 5.       | TRANSFORMERS             | 02       | 0.50                                        | 1.00                                         |

| 6.       | TRANSISTORS              | 04       | 1.70                                        | 6.80                                         |

| 7.       | CONNECTION WIRE          | 17       | 0.015                                       | 0.255                                        |

| <b> </b> | TOTAL                    |          |                                             | 59.44                                        |

|          | TOTAL                    |          |                                             | 59.44                                        |

Table 4.21: Failure rate of electronics components in normal condition (t= $t20^{\circ}C$ ) for Monostable Multivibrator method of design.

# 4.3 <u>SPACE</u>

The number of Integrated Circuits (IC) and all other components including wire connection were considered from the pin diagram for each method of design which shows that the combinational Logic Circuits (10) and many wires connections (23-lines) while the Monostable Multivibrator method of design has (9) Integrated Circuits and (17-lines) wire connections.

Therefore, since the sizes of Diodes, Resistors, Transistors are small compare to ICs size and space occupied by wire connection, we can now conclude that combinational Logic method of design occupies more space.

#### 4.4 <u>SPEED</u>:

Speed can be calculated using the longest wire connection. i.e. the circuit with longest wire connection delays in speed time compare with the one with short wire connection.

From each methods of design pin connection diagram we can see that Monostable Multivibrator method have lesser number of wire connections due to limit number of components compared to Combinational Logic Circuit method. And for these reasons, Monostable Multivibrator design method is faster (i.e having greater speed) than Combinational Logic Circuit method of design.

Apart from determination of speed from wire connection, and how long the wires are, speed can also be determined from each and individual ICs speed of operation (frequency). And it can be concluded that Monostable Multivibrator method of design is faster in operation than Combinational Logic Circuit method due to high frequency Ics used in its design.

#### 4.5 COMPARISM AND EVALUATIONS OF THE METHODS:

From the comparism evaluations carried out in the project, it can be concluded that Monostable Multivibrator method of design which occupies lesser space, have smaller cost of production, speeds faster and having better reliability value is proposed for the construction for future development of traffic light in our environment.

#### CHAPTER FIVE

#### CONCLUSION AND RECOMMENDATION

### 5.1: CONCLUSION

From the result of the studies carried out in the course of this project, that is using Combinational Logic Circuit method and Monostable Multivibrator method of design for traffic light controller system using production cost, reliability, space occupation and speed as criteria. It can be concluded that the use of any of the method of designs mentioned above depends on financial status, availability of Materials and the environmental factors. But traffic light realization using Monostable Multivibrator method of design is more appropriate based on recommendation below.

#### 5.2 <u>RECOMMENDATION</u>

Recommendation made depends on the research carried out on this project using cost of production, reliability, space occupation and speed as points of comparism and evaluations.

Monostable multivibrator method of design with low cost of production, occupies less space, faster and has more or less equal reliability with the other method (Combinational method) is recommended for our environment for further development work which can be carried out due to advantages seen from observation made from the research and work carried out in this project.

### REFERENCES

1. GEORGE LOVEDAY: 1984; Practical Interface Circuits for Micros, PITMAL Publishing Ltd, second Edition; pg.52-73.

ENGR. MOSES L.A: 1994; Lecture Notes on Digital Electronics,

300 LEVEL.

3. ENGR. MOSES L.A: 1994; Lecture Notes on Digital Electronics, 400 LEVEL.

4. The illustrated Science and Invention encyclopedia,

H.S.STUTTMAN Co., INC, vol 18; pg. 2462-2465.

5. MIKE TOOLEY: 1988; Practical Digital Electronics Handbook, PC Publishing.

6. HERBERT TAUB AND DONALD SCHILLING: 1977; Digital Integrated Electronics, Mc Graw - Hill Book Co.

7. CLAUDE A. WINTROWSKI AND CHARLES H. HOUSE: 1981; Logic

Circuits and Micro Computer Systems, Mc Graw Hill Book Co.

8. MIKE TOOLEY: 1990; Everyday Electronics Databook, PC

Publishing.