# DESIGN AND CONSTRUCTION OF A FOUR CHANNEL AUDIO / VIDEO SELECTOR

BY

## **OLONIRE BAMIDELE OLUWATOSIN**

## 2001/12080EE

## DEPARTMENT OF ELECTRICAL/COMPUTER ENGINEERING

SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY

FEDERAL UNIVERSITY OF TECHNOLOGY MINNA ,NIGERIA

NOVEMBER, 2007

## DESIGN AND CONSTRUCTION OF A FOUR CHANNEL AUDIO / VIDEO SELECTOR

BY

#### **OLONIRE BAMIDELE OLUWATOSIN**

2001/12080EE

## DEPARTMENT OF ELECTRICAL /COMPUTER ENGINEERING SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY

#### FEDERAL UNIVERSITY OF TECHNOLOGY MINNA , NIGERIA

## SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF BACHELOR OF ENGINEERING (B.ENG) ELECTRICAL /COMPUTER

NOVEMBER 2007

#### **DEDICATION**

This project is dedicated to God Almighty, for whom and by whom all things are made, for his love and faithfulness and to my beloved mother, Mrs J.A. Olonire, and father Mr. Nathaniel Ariyo Olonire. -

#### **DECLARATION**

I hereby declare that this project was designed, constructed and written by me 'OLONIRE BAMIDELE OLUWATOSIN' 2001/12080EE of the department of electrical and computer engineering .Federal University of Technology, Minna; under the supervision of Mal Bala Salihu .

٩

Signature of student

#### CERTIFICATION

This is to certify that this project work titled DESIGN AND CONSTRUCTION OF A FOUR CHANNEL AUDIO /VIDEO SELECTOR was carried out by Olonire Bamidele Oluwatosin (2001/12080EE) for the award of bachelor of engineering (B.Eng) degree in electrical and computer engineering.Federal University Of Technology,Minna.

Mal Bala Salihu

Project supervisor

29/Nov. 2007

sign & date

Engr . M.D\_Abdullahi

Head of Dept

sign & date

External Examiner

sign & date

#### ACKNOWLEDGEMENT

I am highly grateful to those ,who had in one way or the other made this project a huge success, most especially my supervisor in person of Mal Bala Salihu, for his unflinching support, and under whose understanding advice and constructive criticism, I was able to accomplish the enormous challenge posed by this work, also to my lecturers whose efforts made it possible for me to have a good foundation for the completion of this project.

Unquantifiable thanks to my parents Mr and Mrs Nathaniel Ariyo Olonire for their spiritual, moral, emotional and financial support towards my success in my stay in school ;you are the best.

I am also deeply grateful to my sisters in persons of Miss Ifejola Olonire, Dr.Mrs Omolade Ebun Owoleke, Mrs Omolara Phillips Olonire Falola, Mrs Mayowa Adesanya and Mrs Bosede Abubakar Maigari, for their concern, love and support throughout my stay in school; to also my nephews and nieces Tope Bawa, Tunde Owoleke, Victor Owoleke, Bunmi Owoleke, Kemi Owoleke for their fervent prayers; and also to friends like Omenye Azubike, Seun Ejiko, Victor Arokoyo, Adetunji Ademola, Chike Onyema for standing by my side through thick and thin. Thanks see you all at the top. Most of all my utmost thanks goes to Jehovah God, for his grace, mercies and protection over me throughout my stay in school.

#### ABSTRACT

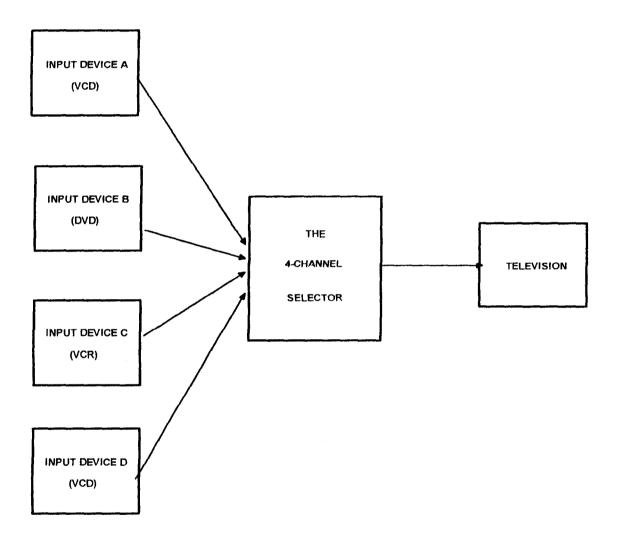

This project titled 'four channel audio/video selector' is designed to provide individuals or personnel's ability to switch or select needed, wanted or desirable audio or video signals from devices imputed and connected to an output display.

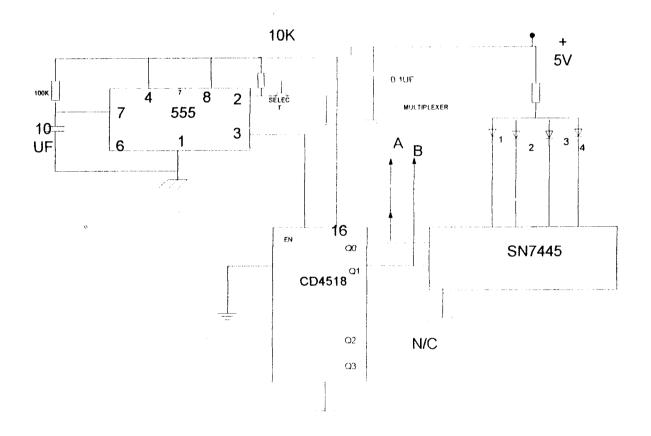

To accomplish the aim and objective of the project CMOS ICs CD4518 counter, CD4052 multiplexer ,SN7445 decoder and IC for video selection and a voltage regulator a 7805 IC were the components used.

The CD4518 counter is a 4 -bit up- counter ,and multiplexer that selects wanted video/audio signals is the CD4052 and the 555 monostable timer switches to desired channel.

The principle of operation of this device is powered by stepping-down an AC supply from P.H.C.N of about 220V to 9V, which is the required power for supply, which also in turn regulated by a voltage regulator IC 7805; the inputted audio/video signals from devices connected to the device is decoded by SN7445 IC, then the 555 monostable timer produces a time lapse pulse which is in turn counted by the counter IC( i.e the CD4518) . Then the desired signal is selected by manually switching the selector knob by the aid of the selector IC the multiplexer CD4052; then transmitted to output which is usually a TV connected to the device .

### LIST OF TABLES

| TABLE 1 | 20 |

|---------|----|

| TABLE 2 | 22 |

| TABLE 3 | 25 |

## **LIST OF FIGURES**

| FIGURE 1  | 11 |

|-----------|----|

| FIGURE 2  | 12 |

| FIGURE 3  | 14 |

| FIGURE 4  | 16 |

| FIGURE 5  | 17 |

| FIGURE 6  | 18 |

| FIGURE 7  | 19 |

| FIGURE 8  | 21 |

| FIGURE 9  | 23 |

| FIGURE 10 | 24 |

| FIGURE 11 | 26 |

| FIGURE 12 | 27 |

| FIGURE 13 | 29 |

| FIGURE 14 | 30 |

## **TABLE OF CONTENTS**

| TITLE                         | PAGE |

|-------------------------------|------|

| COVER PAGE                    | · I  |

| TITTLE PAGE                   | 11   |

| DEDICATION                    | 111  |

| DECLARATION                   | IV   |

| CERTIFICATION                 | V    |

| AKNOWLEDGEMENT                | VI   |

| ABSTRACT                      | VIII |

| LIST OF TABLES                | IX   |

| LIST OF FIGURES               | Х    |

| TABLE OF CONTENT              | XI   |

| CHAPTER ONE                   |      |

| 1.0 INTRODUCTION              | 1    |

| 1.1 AIM AND OBJECTIVE         | 1    |

| 1.2 JUSTIFICATION OF SELECTOR | 2    |

| 1.3 SCOPE OF PROJECT          | 3    |

| 1.4 METHODOLOGY               | 3    |

| 1.5 MERITS AND LIMITATION     | 4    |

| 1.6 PROJECT OUTLINE           | 5    |

| CHAPTER TWO                   |      |

| 2.0 LITERATURE REVIEW         | 6    |

| 2.1HISTORY AND DEVELOPMENT OF AUDIO AND VIDEO DEVICES | 6  |

|-------------------------------------------------------|----|

| 2.2 VIDEO AND AUDIO SIGNAL                            | 8  |

| CHAPTER THREE                                         |    |

| 3.0 DESIGN ANALYSIS                                   | 10 |

| 3.0 BLOCK DIAGRAM                                     | 11 |

| 3.1 POWER SUPPLY                                      | 12 |

| 3.2 BRIDGE RECTIFIER 1                                | 5  |

| 3.3 INPUT UNIT 1                                      | 16 |

| 3.4 VIDEO SELECTOR 1                                  | 19 |

| 3.5 LED DRIVER 2                                      | 25 |

| CHAPTER FOUR                                          |    |

| 4.0 CIRCUIT CONSTRUCTION 2                            | 8  |

| 4.1 CASING CONSTRUCTION 2                             | 9  |

| 4.2 TESTING 3                                         | 0  |

| 4.3 RESULTS AND DISCUSSION 3                          | 31 |

| CHAPTER FIVE                                          |    |

| 5.0 CONCLUSION 3                                      | 32 |

| 5.1 PROBLEMS ENCOUNTERED 3                            | 32 |

| 5.2 RECOMMENDATIONS 3                                 | 2  |

| <b>REFERENCE</b> 3                                    | 3  |

| APPENDIXA34                                           | 4  |

| APPENDIX B 3.                                         | 5  |

| APPENDIXC 3                                           | 7  |

#### **CHAPTER ONE**

#### **1.0 INTRODUCTION**

Video (Latin for "I see", first person singular present, indicative of videre, "to see") is the technology of electronically capturing, recording, processing, storing, transmitting, and reconstructing a sequence of still images representing scenes in motion. Video technology was first developed for television systems, but has been further developed in many formats to allow for consumer video recording and other applications. This project mainly involves a digital 4-1 Audio video (AV) selector for video studio, closed circuit television (CCTV) and home use applications. The design involves the selection of a particular channel with an AV signal from four available channels. The switching is digital, therefore a smooth operation is certain. The materials used in this project ranges from basic electronic components to insulators and a lot of other things which are locally available. The integrated circuits involved are Complementary Metallic Oxide Semiconductor (CMOS). This type of logic is known for its high density content, high flexibility, low power consumption, wide voltage supply range, low cost, and large features.

#### **1.1 AIMS AND OBJECTIVES**

1

The project is aimed at the design and construction of a four channel audio /video selector for the following purpose.

- 1. For slide selection of different strategic aerial views of a highly secured premises of a CCTV (closed circuit television) aborted system.

- For selection of aerial views of a satellite reconnaissance monitoring system of a settlement.

- Selection of different views of in between cameras in stadiums ,during matches or important events; and in media houses.

- 4. Selection of wanted virtual/audio display in homes.

#### **1.2 JUSTIFICATIONS OF A SELECTOR**

The said project can be effectively applied in areas of security monitoring where it could be used with a closed circuit television (CCTV). It could also be used in television studio and media houses as a switch in between cameras. It can also be used domestically to switch between video signal sources

#### **1.3 THE SCOPE OF THE PROJECT**

The project is all about the 4-1 channel switching of Video Audio (AV) signals. The design is made with a considerable level of simplicity. As earlier stated, complementary metal oxide semi conductor (CMOS) integrated circuit (IC) are in use. The use is justified by the merits of the logic as compare to the common other alternative, Transistor Transistor Logic (TTL).

#### **1.4 METHODOLOGY**

The most important step during the course of this project is acquisition of relevant information which involved intense internet browsing and reading of related books and journals on this very topic, sourcing of materials and electronic components for the construction.

The circuit design follows in steps ; a circuitry design software such as 'work bench ' was required to ease up the work , different circuits were simulated on these platform before the work was finally assembled .The result of the earlier steps gave room for the construction of the four channel audio/video selector.

#### **1.5 MERITS AND LIMITATION**

Complementary metal oxide semi conductor (CMOS) technology provides the design reasonable effective performance and economic importance. The design is quite straight forward that someone with little technical electronic knowledge will be able to handle in construction. The project is limited to four AV channels which is not expandable. The switching could be done manually by pressing buttons or automatically with variable timing

#### **1.6 PROJECT OUTLINE**

In the first chapter, a general introduction was given, the aim and objective was highlighted, methodology then merit and limitation of the project reviewed.

Chapter two, deals with the literature review, historical background, theoretical background previous work of others related to this project, challenges that resulted to limitations.

Chapter three covers the system design and analysis, construction of system, diagrams selection of components used and implementation.

Chapter four covers the report, steps taken when constructed system was tested , result tabulated , and general discussion.

Chapter five finally concludes the report of the whole project, recommendation and suggestion should be clearly stated

#### **CHAPTER 2**

#### 2.0 LITERATURE REVIEW

# **2.1 HISTORY AND DEVELOPMENT OF VIDEO AND AUDIO DEVICES**

The term video (from the Latin for "I see") commonly refers to several storage formats for moving pictures: digital video formats, including digital versatile disc (DVD), QuickTime, and MPEG-4, and analog videotapes, including Betamax. Video signals go along with corresponding audio signals, expect in rare occasion. Video can be recorded and transmitted in various physical media: in magnetic tape when recorded as PAL or NTSC electric signals by video cameras, or in MPEG-4 or DV digital media when recorded by digital cameras. In the UK, Australia, The Netherlands and New Zealand, the term video is often used informally to refer to both video recorders and video cassettes; the meaning is normally clear from the context.

Quality of video essentially depends on the capturing method and storage used. Digital television (DTV) is a relatively recent format with higher quality than earlier television formats and has become a standard for television video. 3D-video, digital video in three dimensions, premiered at the end of 20th century. Six or eight cameras with real-time depth measurement are typically used to capture 3D-video streams. The format of 3D-video is fixed in MPEG-4 Part 16 Animation Framework Extension (AFX).

Digital video (the latest video technology) was first introduced in 1983 with the <u>Sony</u> D-1 format, which recorded an uncompressed standard definition component video signal in digital form instead of the high-band analog forms that had been commonplace until then. Due to the expense, D-1 was used primarily by large television networks. It would eventually be replaced by cheaper systems using compressed data, most notably Sony's <u>Digital Betacam</u>, still heavily used as a field recording format by professional television producers. Consumer digital video first appeared in the form of <u>QuickTime</u>, <u>Apple</u> <u>Computer</u>'s architecture for time-based and streaming data formats, which appeared in crude form around 1990. Initial consumer-level content creation tools were crude, requiring an analog video source to be digitized to a computer-readable format. While low-quality at first, consumer digital video increased rapidly in quality, first with the introduction of playback standards such as MPEG-1 and MPEG-2 (adopted for use in television transmission and <u>DVD</u> media), and then the introduction of the <u>DV</u> tape format allowing recording direct to digital data and simplifying the editing process, allowing <u>non-linear editing systems</u> to be deployed wholly on desktop computers.

As of early 2007, the highest resolution demonstrated for digital video generation is 33 mega pixels (7680 x 4320) at 60 frames per second ("UHDV"), though this has only been demonstrated in special laboratory settings [1]. The highest speed is attained in industrial and scientific high speed cameras that are capable of filming 1024x1024 video at up to 1 million frames per second for brief periods of recording. There is moving development of video technology.

#### 2.2 VIDEO AND AUDIO SIGNAL

Composite video is commonly called "video signal" It is the format of an <u>analog</u> television (picture only) signal before it is combined with a sound signal and <u>modulated</u> onto an <u>RF carrier</u>. It is usually in a standard format such as NTSC, PAL, or <u>SECAM</u>. It is a composite of three source signals called Y, U and V (together referred to as <u>YUV</u>) with sync pulses. Y represents the brightness or luminance of the picture and includes synchronizing pulses, so that by itself it could be displayed as a monochrome picture. U and V between them carry the color information. They are first mixed with two orthogonal phases of a color carrier signal to form a signal called the chrominance. Y and UV are then added together. Since Y is a base band signal and UV has been mixed with a carrier, this addition is equivalent to frequency-division multiplexing.

Composite video cannot easily be directed to any broadcast channel simply by modulating the proper RF carrier frequency with it. Most analogue home video equipment records a signal in (roughly) composite format: Laserdiscs store a true composite signal, while <u>VHS</u> tapes use a slightly modified composite signal. These devices then give the user the option of outputting the raw signal, or modulating it on to a <u>VHF</u> or <u>UHF</u> frequency to appear on a selected TV channel. In typical home applications, the composite video signal is typically connected using an <u>RCA jack</u>, normally yellow (often accompanied with red and white for right and left audio channels respectively). <u>BNC</u> connectors and higher quality co-axial cable are often used in more professional applications. In Europe, <u>SCART</u> connections are often used instead of RCA jacks — though SCART can also carry far superior RGB component video signals (and to a lesser

extent, <u>S-Video</u>), so where available, RGB is used instead of composite video with computers, video game consoles, and <u>DVD</u> players. Some devices that connect to a TV, such as <u>videogame consoles</u> and the ubiquitous home computers of the <u>1980s</u>, naturally output a composite signal. This may then be converted to RF with an external box known as an <u>RF modulator</u> that generates the proper carrier (often for channel 3 or 4 in <u>North America</u>). The RF modulator is preferably left outside the console so the RF doesn't interfere with the components inside the machine. <u>VCRs</u> and similar devices already have to deal with RF signals in their tuners, so the modulator is located inside the box. Also, most early home computers usually employed an internal RF modulator.

#### **CHAPTER THREE**

#### **3.0 DESIGN ANALYSIS**

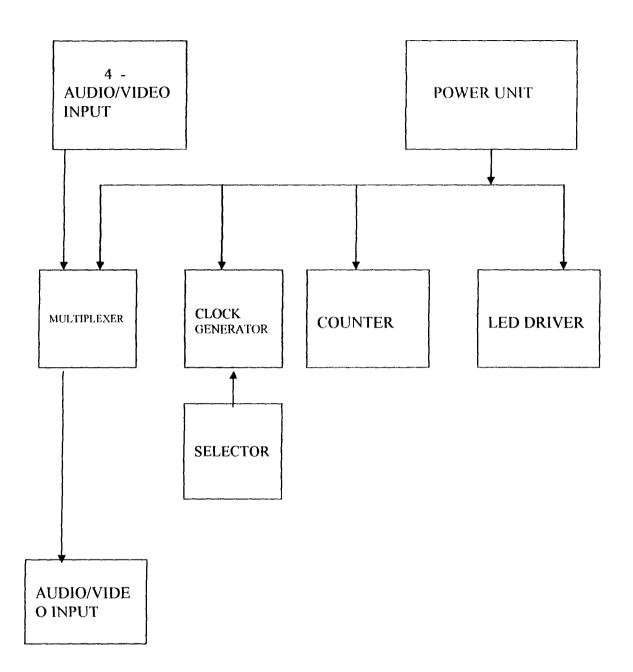

The four channel audio / video selector switching system embodies the following subsystems.

- Power supply.

- CD4052 4-to-1 analog multiplexer.

- Input units

- SW7445 1-of-10 decoder (LED Driver).

- 555 monostable (switch debouncer).

- CD4518 Counter.

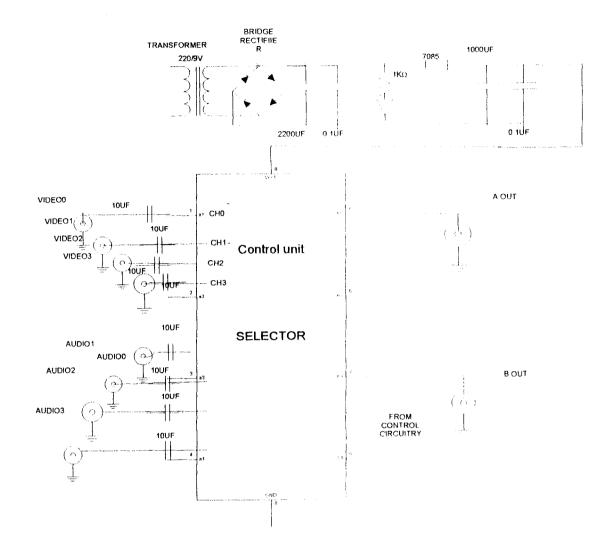

This device was carefully designed and constructed by logically connecting these forementioned components or ICs together, putting a lot of electrical factors into consideration ; such as stepping –down P.H.C.N power supply to 9V as required by the circuitry, rectifying AC into DC .Capacitors and resistors were also not left out as they were used to smoothen and filter fluctuating current flowing in the circuitry design.Below is a block diagram representing the logical architecture of the designed device in fig 3.0.

#### **3.1 POWER SUPPLY**

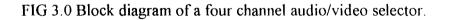

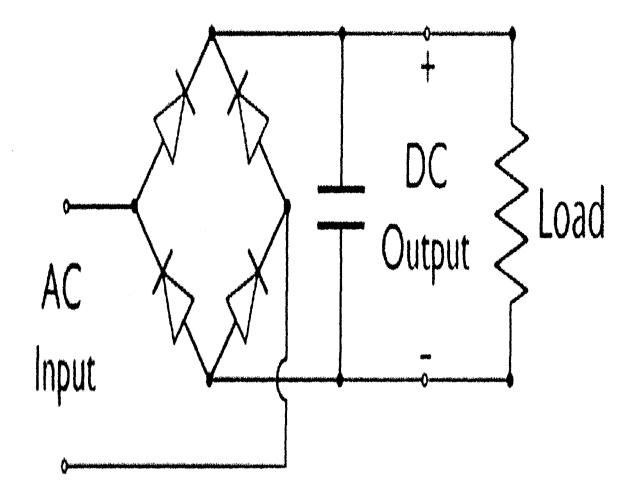

A regulated 5 - volt dc supply was needed for system functionality this was realized using 9v 0.5A step-down transformer wired to a full - wave bridge rectifier the connection is shown in fig 3.1

Fig 3.1 Power Supply Unit. 5 V regulated DC supply

The 9v rms ac voltage was connected to a pulsating dc voltage of amplitude.

Vpeak =  $[(Vrms\sqrt{2}) - 1.4]$

Where

Vrms=secondary AC voltage.

$\sqrt{2}$  = rms -to -peak scaling factor .

1.4= 2 -diode forward voltage drop.

Using the system variables,

Vpeak =  $9\sqrt{2} - 1.4 \approx 11.2V$

This value of voltage was smoothened by a capacitance evaluated from

Q = CV = IT

Where

C = value of smoothening capacitance

V=maximum value of AC ripple voltage.

I= maximum load current.

T = 1/2 (Full – wave bridge rectifier )

F = Main frequency.

$C = I T/V = I \times I/2F /V$

For the 7805 regulator the minimum input voltage needed to maintain regulation is 7V.Therefore a 2 V peak -to -peak AC ripple voltage was fixed. The maximum system current drain was normally taken as 150 mA.

Calculating for C.

C= 0.15 × 1/(2× 50)/2 = 0.15 × 0.01 /2 =0.0015/2 =0.00075F

=750µF

A 25 – volt 2200 $\mu$  F capacitor was used for the smoothening capacitance .

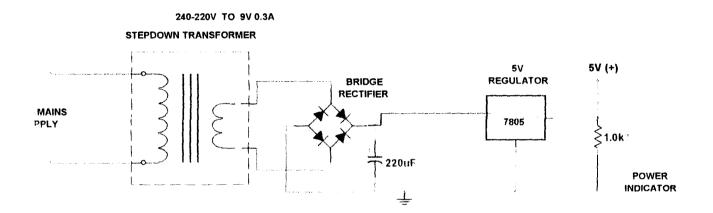

The 7805 regulator is a 5-volt 1-amp regulator with the pinning shown in fig 3.2

## Vin GND Vat

FIG 3.2 Pin -out assessment of 7805

The regulator was connected across the smoothening to regulate the voltage from 11V to 5V at a maximum load current of 1A.

The 5- volt output was stabilized by a 16 v  $1000\mu$ F capacitance and fed to the circuit .

#### **3.2 THE BRIDGE RECTIFIER**

A diode bridge or bridge rectifier (occasionally called a Graetz bridge) is an arrangement of four diodes connected in a bridge circuit as shown below, that provides the same polarity of output voltage for any polarity of the input voltage. When used in its most common application, for conversion of alternating current (AC) input into direct current (DC) output, it is known as a bridge rectifier. The bridge rectifier provides full wave rectification from a two wire AC input (saving the cost of a center tapped transformer) but has two diode drops rather than one reducing efficiency over a center tap based design for the same output voltage.

For many applications, especially with single phase AC where the full-wave bridge serves to convert an AC input into a DC output, the addition of a <u>capacitor</u> may be important because the bridge alone supplies an output voltage of fixed polarity but pulsating magnitude.

FIG 3.3 A SIMPLE BRIDGE RECTIFIER

#### **3.3 INPUT UNIT**

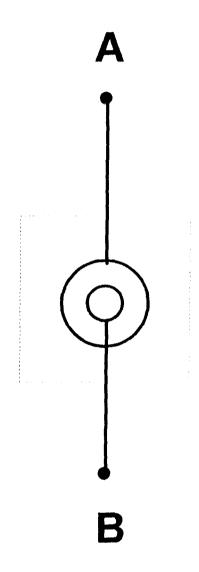

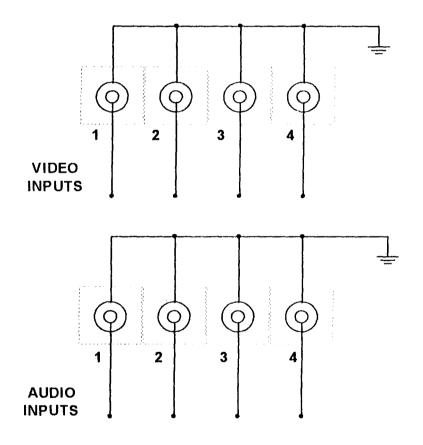

The Input unit involves mere eight AV sockets. Four serve video and the others, audio. They are divided into four groups. Each group serves a particular channel which involves both video and audio signals. The sockets are points in which the device is connected to or receive signals from external devices such as video, camera, DVD, and VCD.

Fig 3.4 An input Socket

The leading sockets possess two terminals A and B (as shown above). A is usually connected to the ground or negative terminal of the power supply. The other terminal deals with the main transmitted signal containing video or audio information.

FIG 3.5 Four video /audio inputs. 18

#### **3.4 VIDEO SELECTOR**

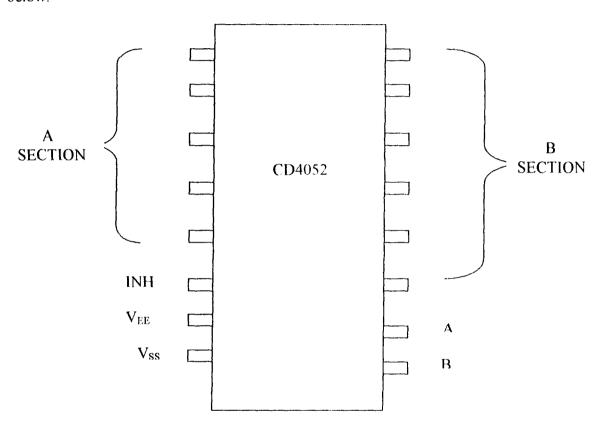

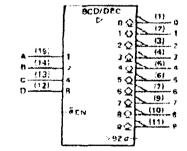

An analog 1 - of - 4 CMOS multiplexer was used to select the desired AV audio /video pair .the CD4052 is a CMOS device in a 16 -pin package shown below. VDD

FIG 3.6 A CD4052 ANALOG MULTIPLEXER

The CD4052 multiplexer is a dual 4-to-1 switching device with two section A and B.The device has two address inputs A0, A1 and an active low enable input.Two input channels are selected simultaneously depending on the state of the address inputs.

| AD | DRESS | SELECTED C | HANNEL (A,B) |

|----|-------|------------|--------------|

| A1 | A0    |            |              |

| 0  | 0     | CH 0(A)    | CH0(B)       |

| 0  | 1     | CH 1(A)    | CH 1(B)      |

| 1  | 0     | CH 2(A)    | CH 2(B)      |

| 1  | 1     | CH 3(A)    | CH 3(B)      |

FIG 3.0 State of address inputs.

The video signals were connected to the A section and the audio signal connected to the B sections.

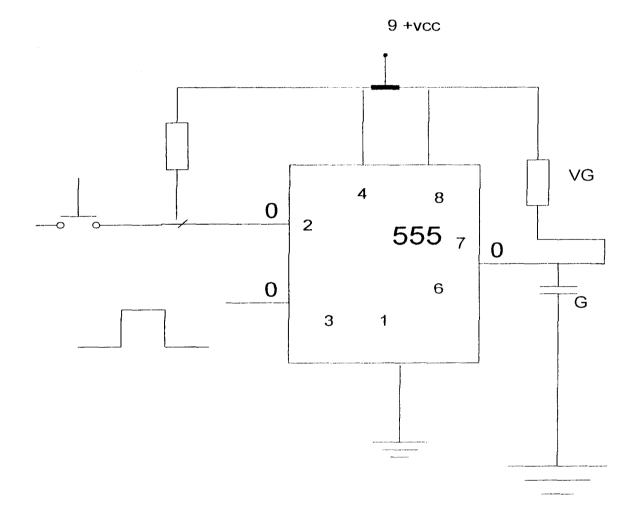

The address were generated by a 4- bit counter CD4518 clocked by a debouncer circuitry to prevent spurious clock generation.

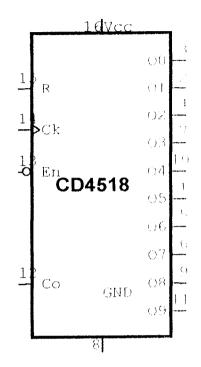

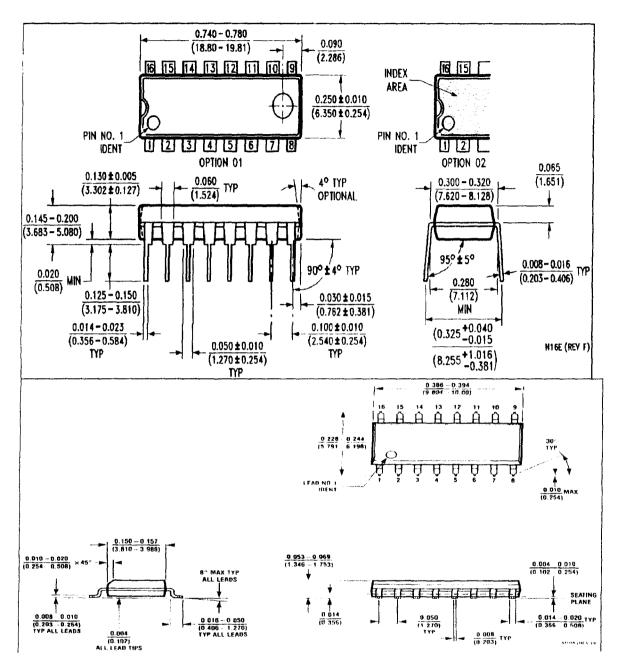

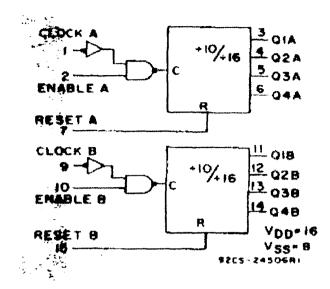

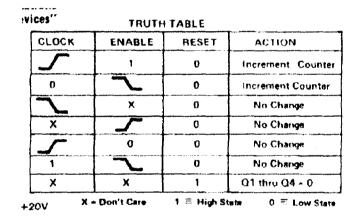

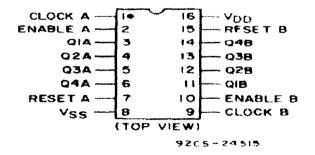

#### 3.4.1 CD4518

The CD4518 is a dual 4 - bit binary up counter indicated as shown in fig 3.4

FIG 3.7 CD4518 dual up - counter

The counter cycles through 16 distinct stages when clocked externally. The output charge stage one at a time under the influence of the external clocking signal.

| D | С | В | А |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 0 |   |   |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 |   | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | J |

| ] | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 |

Table 3.1 Output of a clocking signal.

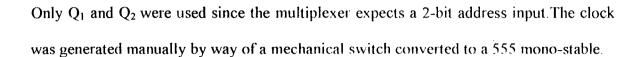

FIG3.8 555 MONOSTABLE

An NE555 monostable was used to debounce the select switch. When a mechanical switch opens or closes, the contacts make and break rapidly many times before finally assuming the intruded position.

If such a switch is corrected to a clocked device, the device will receive not only one clock pulse but numerous clock pulses, generating erroneous output.

Debouncing the switch overcomes this problem. A debouncer is an RC time relay circuit that extends or stretch the input wave form by a factor dependent on the value of the timing components.

The NE555 multivibrator is triggered when the voltage is triggered when the voltage on pin 2 (triggered input) falls

FIG 3.9 Monostable -to-counter connection

#### 3.5 LED DRIVER

To indicate the selected channel, an SN7445 1-of -10 decoder/driver was used to drive one of four light emitting diodes at a forward voltage of 2V at 10mA. The BDC Address input to the CD7445 were connected as shown below.

| SN7445 | COUNTER |

|--------|---------|

| A      | Αθ      |

| В      | Al      |

| С      | V0      |

| D      | VI      |

#### TABLE 3.2 THE BCD ADDRESS INPUTS TO THE CD7445 IC

The part can sink a maximum current of 80mA while holding its logic 0 output at 0.3V. The LEDs were driven via a currents- limiting resistor, the value of which was calculated from the expression below.

$Rs = Vs - V_{LED} l_{LED}$

Vs = System supply voltage = 5V

$V_{LED} = 2V$ ,  $I_{LED} = 10Ma$  nominal.

Rs=5 - 2/ 0.01

$= 330 \Omega$

A 330 $\Omega$  resistance was used.

FIG3.10 A CIRCUIT DIAGRAM OF FOUR CHANNEL AUDIO/VIDEO SELECTOR.

FIG3.11 Schematic circuit diagram of a four channel audio/ video selector.

#### **CHAPTER FOUR**

#### 4.0 CONSTRUCTION, TESTING AND DISCUSSION OF RESULT

#### 4.1 CIRCUIT CONSTRUCTION

The first step in the construction of the project was the purchase of the needed components and materials. They were properly and independently tested for malfunction or defect. Due to the apparent workability of the design along with my initial experience in electronics, the construction started on the bread board and not the Vero board. The power circuit was first mounted on a bread board which was before then cut into proper shape to fit the circuit. Integrated circuit sockets were soldered on the board for each involved integration circuit. The socket protects the component from heat related damage that might occur during soldering. Other components such as capacitors, resistors and diodes were directly soldered to the Vero board. The soldering operation was done as fast as possible to avoid damage of the component due to heat.

Jumper wires were extensively used for connecting the components in line with the circuit diagram. Some of these wires needed to be glued to the board to avoid unwanted removal. Afterwards the circuit connections were properly tested for any wrong or error placement. Short circuit was quite avoided and properly checked before the circuit was plugged to electricity. After such tests, the circuit was set for a real functional test.

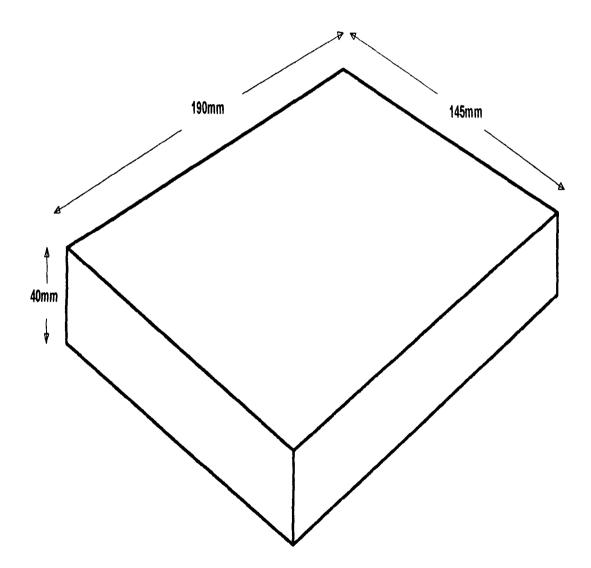

### **4.2 CASING CONSTRUCTION**

The casing was made out of plastic material (tiles). A flat rectangular plastic material was incorporated into the construction. Suitable positions were selected on the casing for external parts of the circuit. Holes were bored into the case to properly fit the project use. The kind of fitting in use is bolting and screwing.

Fig 4.1The casing dimension

#### **4.3 TESTING**

The testing was quite straight forward. The diagram below shows a description.

Fig 4.2 The test set-up

Four Audio/Video (AV) devices (such as VCD, DVD, and VCR) were connected to the constructed device through the input terminals and their output terminals. The output

sockets of the device were connected to the AV input of a television set, in use as a monitor. The signal or transmission from each input devices was carefully identified before any switching operation.

The control buttons of the construction were put into use. The four main control buttons were use in selecting a particular input or channel. The result was monitored on the connected television.

Moreover, the automatic feature was tested by set it in mode. The speed knob was turned for varying speed rate.

#### **4.4 RESULT AND DISCUSSION**

It was observed that the monitoring unit (the involved television set), picked up the selected signal from the 4-channel selector and no observed error.

A self-controlled channel selection was amazingly observed on the set-up. The rate of selection was controllable on the speed knob.

Moreover, the output video and audio quality was acceptable. The project was quite a success.

#### **CHAPTER FIVE**

#### **5.0 CONLUSION AND RECOMMENDATIONS**

#### **5.1 CONCLUSION**

The project demonstrated the use of technology in the control of electrical signals. The device has being tested and was found to meet the expected results. The selection of channels was smooth and without distortion of any sort.

#### 5.2 PROBLEMS ENCOUNTERED

- The search for needed information

- Packaging the circuit

- The soldering operation

- The circuit design

#### 5.3 **RECOMMENDATION**

The design could be improved by increasing the number of channels, incorporation of a remote control, usage of more compact integrated circuits, and possible computer interfacing with software application.

#### REFERENCE

- [1] Paul Horowitz, Winfield Hill, The art of electronics, second edition, pp 948-965.

- [2] B.L Theraja, A.K Theraja, A text book of Electrical Technology, pp 1150-1210.

- [3] www.datasheetcatog.com

- [4] <u>www.st.com</u>

- [5] www.wilkipedia.com

[6] Donald .P. Leach, Albert Paul Malvino, Digital Principles And Applications (Fourth Edition) Mcgraw – Hill International Editions. New York Atlanta Dallas. Pp 188-256.

[7] .Thomas .E. Newman ,Electrical and Electronics (first edition) Glecoe/Mcgraw – Hill

Internation Editions.The Neville Press ,Inc.Mt Pleasant,South Carolina,Pp 409-416, 497511.

#### **APPENDIX A**

**CD4052 DATASHEET**

#### **APPENDIX B**

#### **CD4518A FUNCTIONAL DIAGRAM**

# RECOMMENDED OPERATING CONDITIONS at $T_A \approx 25^{\circ}$ C, Except as Noted For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges.

| CHARACTERISTIC                                                                                                                                                                                                                                                                                                                                                                                                               | Vop           | LI   | VITS         | LINITS |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|--------------|--------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                              | IVI           | Min. | Max          | 1      |  |

| Supply Voltage Range (For Tightfull Package<br>Temperature Range)                                                                                                                                                                                                                                                                                                                                                            |               | з    | 14           | v      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 5             | 400  |              | 1      |  |

| Enable Parke Wirlth, two                                                                                                                                                                                                                                                                                                                                                                                                     | <b>י</b> ם    | 200  | Í            | 1      |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                            | 15            | 140  |              |        |  |

| , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                        | 5             | 200  | 1            | •      |  |

| Duck Pulse Width, tay                                                                                                                                                                                                                                                                                                                                                                                                        | 10            | 100  | 1            |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 15            | 70   |              | 1      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 5             | 1    | 15           | [      |  |

| Clock Input Frequency, Tru                                                                                                                                                                                                                                                                                                                                                                                                   | 10            | :05  | ۲            | 1 MH7  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 15            |      | 1            | }      |  |

| Clock Basic Fait time TrCL or tpCL                                                                                                                                                                                                                                                                                                                                                                                           | 5<br>10<br>15 |      | 15<br>5<br>5 | 913    |  |

| ny ara-daharan'ny ara-daharan'ny tanàna amin'ny taona 760864. Ilay kaominina dia kaominina | 5             | 750  |              |        |  |

| Reset Pulse Width Tuy                                                                                                                                                                                                                                                                                                                                                                                                        | 10            | 110  |              |        |  |

| **                                                                                                                                                                                                                                                                                                                                                                                                                           | 15            | 90   |              | 1      |  |

Fig. 10 - Opanie: power displaced

Fig. 12 Occases device surrent test involution

Fig. 13 - Inpur wekege-current test corcuit

# DYNAMIC ELECTRICAL CHARACTERISTICS # 1<sub>A</sub>=25°C: Input 1<sub>p</sub>:y=20 ns, CL=50 pF, RL=200 KΩ CHARACTERISTIC TEST CONDITIONS LIMITS UNITS

| CHARACTERISTIC                                                  | I TEST COM | TEST CONDITIONS |               |                  | LIMITS              |     |  |  |

|-----------------------------------------------------------------|------------|-----------------|---------------|------------------|---------------------|-----|--|--|

|                                                                 |            | VDD<br>V        | Min           | Typ              | Max                 |     |  |  |

| Propagation Delay Time, 1941, 1014<br>Ordek or Enable to Output |            | 5<br>10<br>15   |               | 280<br>115<br>80 | 560<br>230<br>169   | 15  |  |  |

| Reset to Output                                                 |            | 4<br>10<br>15   |               | 330<br>130<br>90 | 650<br>225<br>170   |     |  |  |

| Transition Time Toppe Trans                                     |            | 5<br>10<br>15   |               | 100<br>50<br>40  | 200<br>100<br>- 80  |     |  |  |

| Maximum Opek Input Frequency, FCE                               |            | 5<br>10<br>15   | • 5<br>3<br>4 | う<br>6<br>月      |                     | 947 |  |  |

| Minimum Clock Polse Width, t <sub>W</sub>                       |            | 5<br>10<br>15   |               | 100<br>50<br>35  | 200<br>102<br>10    | 0,  |  |  |

| Clock Rise or Fall Time, 17 or 14.                              |            | 5<br>10, 15     | -             |                  | 15<br>5             | 4:3 |  |  |

| Minimum Baset Polse Width, #W                                   |            | 5<br>10<br>14   |               | 126<br>56<br>40  | 2546<br>1110<br>180 |     |  |  |

| Minimum Enable Pulse Width, 3 <mark>W</mark>                    |            | 5<br>10<br>15   |               | 290<br>100<br>70 | 100<br>200<br>140   | - 3 |  |  |

| Impor Capacitance, CIN                                          | Are loper  |                 |               | 5                | 75                  | ÷F  |  |  |

#### **APPENDIX C**

SDLS110

#### SN5445, SN744 BCD TO DECIMAL DECODERS/DRIVER

DECEMBER 1972 REVISED MARCH 18

#### FOR USE AS LAMP, RELAY, OR MOS DRIVERS

featuring

- Full Decoding of Input Logic

- 80-mA Sink-Current Capability

- All Outputs Are Off for Invalid BCD Input Conditions

| FUNCTION TABLE |    |        |    |    |     |         |     |            |      |    |      |     |    |     |

|----------------|----|--------|----|----|-----|---------|-----|------------|------|----|------|-----|----|-----|

| [              | [  | INPUTS |    |    |     | QUTPUTS |     |            |      |    |      |     |    |     |

| NO.            | 0  | C      | B  | A  | 0   | 1       | 2   | 3          | 4    | 5  | 6    | 7   | 8  | 9   |

| 0              | L. | L      | Ł  | L  | L   | H       | н   | н          | ч    | Н  | H    | н   | ਜ  | H   |

| 1              | L  | ŧ      | ١. | н  | Ħ   | ١.      | 28  | ч          | 34   | м  | н    | н   | 14 | 11  |

| 2              | L  | L      | Ð  | ٤  | In. | 11      | L   | 6 <b>j</b> | 53   | į٠ | +4   | 11  | н  | н   |

| 3              | ÷. | L      | ч  | н  | 14  | н       | н   | L          | - 14 | н  | ч    | н   | ч  | н   |

| 4              | L  | H      | L. | L  | H   | н       | Ħ   | н          | L    | н  | - 14 | н   | ++ | H   |

| 5              | L  | H      | L  | Ħ  | н   | н       | H   | H          | Ħ    | L  | H    | H   | H  | H   |

| 3              | ι  | н      | 54 | L  | H.  | H       | -94 | 4          | н    | Ħ  | L    | 11  | Н  | 1Ŧ  |

| 7              | L  | н      | ч  | н  | н   | н       | ч   | н          | н    | н  | 14   | L   | н  | 11  |

| 8              | н  | L.     | L  | t. | H   | Ħ       | н   | -1         | **   | н  | 74   | •1  | ł, | ++  |

| 9              | H  | Ŀ      | ٤  | H  | **  | ŧ.      | i   | ч          | ++   | +4 | н    | +1  | H  | €.  |

| 1              | ++ | ι      | H  | τ  | н   | H       | ы   | H          | ਸ    | 14 | н    | - 4 | 11 | 11  |

| ۵              | н  | Ł      | н  | н  | н   | н       | н   | н          | н    | н  | н    | ч   | н  | н   |

| NVALD          | н  | н      | I. | ۲. | н   | Ħ       | Ħ   | H          | н    | 94 | ÷1   | •1  | 11 | 14  |

| Ž              | н  | 13     | L  | н  | н   | н       | н   | н          | н    | ¥4 | ++   | Ħ   | 11 | ŧŧ. |

|                | н  | ы      | н  | •  | н   | н       | н   | н          | м    | 14 | ы    | н   | ы  | 58  |

|                | н  | ++     | н  | н  | н   | н       | H   | н          | H    | 11 | н    | 11  | н  | н   |

H = high town lotts, c = tow town fant

#### description

These monolithic BCD-to-decimal decoders/devers consist of eight inverters and two four input NAND gates. The inverters are connected in pairs to make 8CD input deta available for decoding by the NAND gates. Full decoding of valid BCD input logic oncures that an outputs remain off for all invalid binary input conditions. These decoders feature TTL inputs and highparformance, n-p-n output transistors designed for use as indicatorizatay drivers or as open-collector logic circuit drivers. Each of the high-breakdown output transistore (30 volts) will eink up to 80 milliompores of current Each input is one normalized Series 54/24 load. lobuts and outputs are entirely compatible for use with TTL log-c circuits, and the outputs are compatible for intertacing with most MOS Integrated circuits. Power dissipation is typically 215 milliwatts

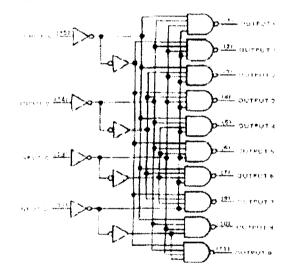

logic diagram (positive logic)

logic symbol

Promotive shown are for J. N. and W packages

#### SN5445, SN7445 BCD-TO-DECIMAL DECODERS/DRIVERS

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                                    |           |            |

|---------------------------------------------------------------------|-----------|------------|

| Input voltage                                                       | · · · · · | <b>5</b> . |

| Maximum current into any putput (offistate)                         |           | 1          |

| Operating free air temperature range: SN5445 Circuits               |           | 55 G to 22 |

| SN7445 (Circuit)                                                    |           | 01 C 10 P  |

| Sturage temperature range                                           | •         | 65°C to 15 |

| NOTE 1: Voltage values are write respective network ground terms :: |           |            |

#### recommended operating conditions

|                                   | Salbaah |     |      | I    | 1   |      |     |

|-----------------------------------|---------|-----|------|------|-----|------|-----|

|                                   | MIN     | NOM | MAX  | MIN  | NOM | MAX  | UN  |

| Supply voltage, VCC               | 4.5     | ž   | 55   | 1 15 | õ   | 5.25 | Y   |

| Othistate output voltage          |         |     | - 43 |      |     | חז   | ΓV. |

| Operating free an temperature, TA | -55     |     | 125  | Ü    |     | 70   | C   |

|                  | PARAMETER                              | TEST CONDIT             | IONS                                        | MIN | TYP    | MAX | UN          |

|------------------|----------------------------------------|-------------------------|---------------------------------------------|-----|--------|-----|-------------|

| ViH              | High-level input unitage               |                         |                                             | 2   |        |     | V           |

| VIL              | Low level input vortage                |                         | forme constraint supportantly of the second | T   |        | 0.9 | V           |

| VIK              | Input clamp voltage                    | Yec WIN 1 12 mA         | 9                                           | T   |        | 1.5 | TV          |

|                  |                                        | YCC = MIN. VHI + 7 V.   | Oleni - Hi ma                               |     | 05     | a n | <b>I</b> ., |

| VOten)           | On state output voltage                | V:L ≤ 0.8 V             | 10:00 = 20 mA                               | T   |        | 0.4 | Ĭ           |

| *****            | trinet Off-state except current        | YCC " MIN. VIH - 7 V.   | ,                                           |     |        | 250 |             |

| 10:00-73         | Constant Constituent Children          | VIL TO FV. VOION T 30 V |                                             |     |        |     |             |

| 1                | toput current at maximum input voltage | YCC-MAX VI-55V          |                                             |     |        | 1   | mA          |

| <sup>1</sup> [14 | High favel input aurient               | YCC - MAX. VI - 2.4 V   |                                             | 1   | ······ | 40  | uA          |

| 11               | Low-level input current                | VCC MAX VI TO 4 V       |                                             | -   |        | -15 | 1236        |

|                  | Supply current                         | VCE MAX See Note 2      | SN 5445                                     | 1   | 43     | 62  | -           |

| 'cc              |                                        | ACC. MUN' PLENDIN 5     | SN7445                                      | 1   | 43     | 70  | 1.136       |

\*For conditions shown as MIN or MAX, use the appropriate value specified under recommended operation conditions for the employed at each This typical whiles are at V<sub>CC</sub> = EV. T<sub>A</sub> = 25°C NOTE 2: 3<sub>CC</sub> is measured with all inputs grounded and cutputs open

#### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ} C$

| n na handa an     |                                 |                 |

|-------------------------------------------------------|---------------------------------|-----------------|

| PARAMETER                                             | TEST CONDITIONS                 | MIN TYP MAX UNI |

| IPLH Propagation delay time, low-to-high-level ou got |                                 | 50 ns           |

| IPHL Propagation delay time, high to law level output | CL - G BE AL 100 ST See Visio 3 | 50 ) 7.5        |

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

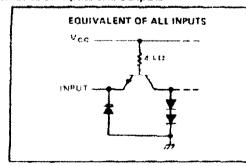

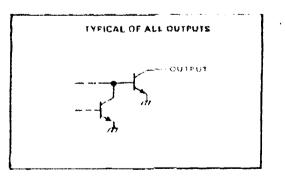

#### schematics of inputs and outputs

## MANUAL OF OPERATION FOR FOUR CHANNEL AUDIO/VIDEO

#### SELECTOR

The device prototype is operated following these simple procedures.

- 1. Supplying power to the device from P.H.C.N.

- 2. Connecting input devices to the device.

- 3. Cross-checking to make sure that all connections are made properly.

- 4. Connecting devices into the audio input terminals.

- 5. Connecting devices into video input terminals.

- 6. Connecting the output devices (i.e. the T.V) to the output audio/video output terminals.

- 7. Cross-check for proper and correct connections.

- 8. Select desired or wanted output by manually pressing the select node.

- 9. Disconnect completely from power supply.

#### PRECAUTIONS

- 1. Keep away from moist environment.

- 2. Avoid connection of device to high power supply.

- 3. Isolate completely from power supply when not in use.