## **DESIGN CONSTRUCTION AND TESTING**

OF

## A MULTI-CHANNEL WIRELESS CONTROL SYSTEM

BY

# OYEWOBI STEPHEN. S. 97/6145EE

A PROJECT SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY,

FEDERAL UNIVERSITY OF TECHNOLOGY,

MINNA.

SEPTEMBER, 2003.

## **DESIGN CONSTRUCTION AND TESTING**

OF

## A MULTI-CHANNEL WIRELESS CONTROL SYSTEM

BY

# OYEWOBI STEPHEN. S. 97/6145EE

# A PROJECT SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

SCHOOL OF ENGINEERING AND ENGINEERING TECHNOLOGY, FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA.

IN PARTIAL FULFILMENT OF THE REQUIREMENT FOR THE AWARD OF THE BACHELOR OF ENGINEERING (B.Eng.)

DEGREE IN ELECTRICAL AND COMPUTER ENGINEERING

SEPEMBER, 2003.

## **DECLARATION**

I, hereby declare that this project is an original concept wholly carried out by me, under the supervision of Mr. ABRAHAM, of the department of Electrical and Computer Engineering, Federal University of Technology, Minna.

Oyewobi S. Stephen

Student

Estept 29/10/2008

## **CERTIFICATION**

I certify that this project was carried out by **Oyewobi, S. Stephen** under the supervision of **Mr. ABRAHAM** of the Electrical and Computer Engineering Department, Federal University of Technology, Minna, Niger State, Nigeria.

| Mr. ABRAHAM Supervisor    | Sign/Date |

|---------------------------|-----------|

| ENGR. M.N. NWOHU<br>H.O.D | Sign/Date |

| External Examiner         | Sign/Date |

## **DEDICATION**

This project is dedicated to God for his grace, and to the Oyewobis for all their sacrifices.

#### **ACKNOWLEDGEMENT**

First and foremost, I give God the glory and honour for His abundance grace that has seen me through my academic pursuit.

My thanks also goes to my parents for their love and support; Elder and Deaconess Samson Adewale Oyewobi, my siblings; Victoria, Janet and Christiana and also my brothers; Michael, Benjamin and Timothy for their love and encouragement.

I am greatly indebted to my project partner Mr. Johnson O. Olakanmi.

I am also indebted to my friends; Idris, Femi, Abiodun, Maiyaki, Mohammed, Brownson, Dantala, Micheal, I.K, Alaya, Sola, K.B., Prosper, Hon. Adamu and other too numerous to mention for their support and encouragement, to you 'Guys' I say thank you.

My sincere appreciation also goees to my departmental lecturers especially to Mr. Abraham and the H.O.D. Engr.M. N. Nwohu.

Last but not the least, my appreciation goes to my numerous well-wishers and Mr. Anjoorin, Adewale for the typing of this project.

## **ABST RACT**

In the report, the design, and construction of a multi-channel wireless controller system is presented. The controller system is made of the – switches, the transmitter, the receiver, and the controlled device, which are the light emitting diodes. The switches are used to activate the transmitter, which transmits a generated signal received by the receiver and used to activate the device to be controlled.

The system had been powered by a battery because of the regular outages by NEPA.

## TABLE OF CONTENTS

| Title page                      | i   |

|---------------------------------|-----|

| Declaration                     | ii  |

| Certification                   | iii |

| Dedication                      | iv  |

| Acknowledgement                 | v   |

| Abstract                        | vi  |

| Table of content                | vi  |

| CHAPTER ONE                     |     |

| Introduction                    | i   |

| Project Description             | 1   |

| Aim and Objectives              | 2   |

| How it Works                    | 3   |

| Literature Review               | 3   |

| CHAPTER TWO                     |     |

|                                 | 5   |

| System Design and Analysis      |     |

| Switches and Low-power Diodes   | 5   |

| Circuit Analysis                | 6   |

| Inverter and Register           | 6   |

| Circuit Analysis                | 7   |

| Multiplexer and Johnson Stepper | 9   |

| Transfer Control Logic              | 11   |

|-------------------------------------|------|

| Transmitter                         | 12   |

| Antenna                             | 14   |

| Receiver                            | 15   |

| Receiving Antenna                   | 15   |

| RS flip-flop                        | 17   |

| Shift Register and Latch            | 18   |

| Decoder                             | . 19 |

| JK flip-flop                        | 21   |

| Controlled System                   | 23   |

| CHAPTER THREE                       |      |

| Introduction                        | 25   |

| Choice of Logic Family              | 25   |

| System Integration                  | 26   |

| Tools used for Project Construction | 26   |

| Testing, Result and Discussion      | 27   |

| CHAPTER FOUR                        |      |

| Conclusion and Recommendation       | 28   |

| Suggestion                          | 29   |

| Appendix                            | 30   |

| Reference                           | 31   |

#### **CHAPTER ONE**

#### INTRODUCTION

1.0

It is difficult to imagine what modern living would be like without ready access to reliable, economical and efficient means of communication.

Communication means conveying or transmission of information from one place to another. In this design, emphasis would be on transmission engineering.

Transmission engineering in telecommunication is the transmission of information or signal over comparative long distances through a network consisting of switching, signaling and transmission plants and delivering the signal to a destination through a transmission medium. Transmission medium may include the ionosphere, trosphere, free space or simply a transmission line. The choice of medium for this design is however freespace (non – wired).

Transmission system engineering deals with the production transport and delivering of quality signal from source (Transmitter) to destination (Receiver).

However, in this design, the signal received at destination is used to control a system hence, the name "multi-channel wireless control system".

## 1.1 PROJECT DESCRIPTION

This project basically consists of two main parts, which are further divided into modules. The main parts are transmitter and receiver.

The transmitter and receiver have 2 modules each, which are the analogue and digital modules.

The digital modules of the transmitter consist of the switches, register, multiplexer and the clock, while the analogue module consist of the transmitter part which modulates the waveform to the desired power level and delivers it to the transmitting antenna.

Similarly, the receiver analogue part consists of the receiving antenna; the receiver part where the signal is amplified and the digital module consist of the shift register, the decoder and the flip-flop.

The economical concept of this project is that, it is a multi-channel system, which means more than one output or systems can be controlled for a number of switches without the crucial link of cables between the transmitter and the controlled system or output.

Aside the many advantages of this project, it renders useless the wired system, which makes it almost impossible to reach the distant places, and also it makes distant point easily accessible.

## 1.2 AIM AND OBJECTIVES

The aim of this project is to make System Control more easily accessible, and this could be achieved with the following objectives:

Design of a system that would remove the setback presented by the already existing wired system; Design of transmitter and receiver to achieve a wireless nature, transmission through free space; Designing for a suitable range of distance of operation of the system; Designing a system with high reliability and low-cost, since access to cables and repeaters is extremely difficult and costly.

## 1.3

#### **HOW IT WORKS**

This project is a system in which there is an appreciable distance separating the controlled system and controlling system.

There are three essential components in a "Wireless Control System" these are; a controlling system; a transmission medium; and a controlled system.

For the sake of clarity, I would assume a robot for handling highly harmful radioactive isotope from a safe distance as the controlled system; this project is designed so that the operator can press a switch of the controlling system from a safe distance to control the activities of the robot.

## 1.4 LITERATURE REVIEW

In this section, some historical notes on communication with emphasis on digital communication and related issues is presented.

The origin of binary code, basic to the operation of digital communication may be traced back to the early work of Francis Bacon at the beginning of the 17<sup>th</sup> century. Bacon used five-letter combination of only two distinct letters to represent 24 letters of the alphabet as means of encoding secret messages.

Bacon two-letter alphabet was published in 1605. Later on, in 1641, John Wilkins published a book in which Bacon's two-letter alphabet was not only explained but also expanded by employing three-and-five letter alphabets. It was thus demonstrated for the first time that more codes elements are needed for the average code-word length to become shorter.

In 1703, Gottfried Wilhelm Leibnitz gave a lecture to the Royal Academy of Science in Paris, entitled: "explication de l'arithmetic binaire", the text of his lecture was published in the proceeding of the academy in 1705; Leibntz used the number 0 and 1 his binary code.

It appears that Leibnitz binary code was developed independently from Bacon and Wilkins.

In 1864, James Clerk Maxwell formulated the electromagnetic theory of light and predicted the existence of radio waves; Heinrich Hertz established the existence of radio waves in 1887.

It appears that digital communication techniques were first employed for microwave radio transmission in France in the 1930s.

In this report, digital communication principle was used to transfer codes from the transmitter, which are in binary codes to the receiver, and used to activate the controlled system.

And radio waves were used as the vehicle for conveying the transmitted signal to the receiving terminal [5].

## **CHAPTER TWO**

## 2.0 SYSTEM DESIGN AND ANALYSIS

The project design is complex, so the different sub-system would be analyzed in units of the whole system for better understanding.

## 2.1 THE SWITCHES AND THE LOW-POWER DIODES

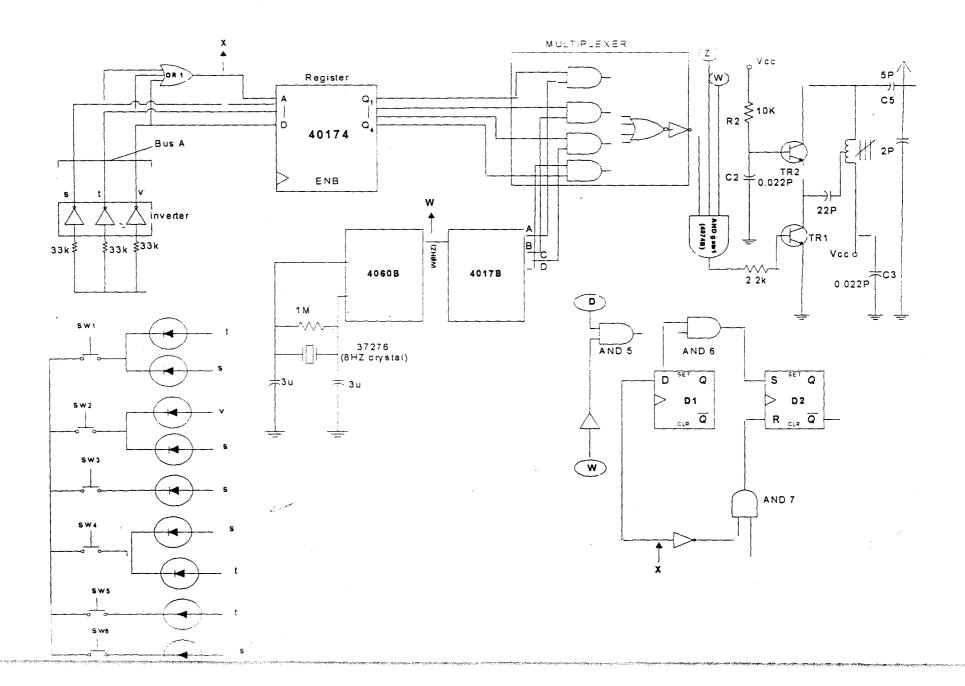

It is from this unit that the whole system is triggered-on. It consists of push buttons and low-power diode as shown below in the circuit diagram of fig.2a.

Fig. 2a Switches and Low-power Diode

The switching unit as it can be seen from the diagram above consists of six pushbutton and nine power diodes.

The whole system is triggered-on from this unit; the output of the low-power diode is connected to the inverter, which form the next unit.

Each button of the switching unit sends different codes for transmission but the buttons are similar.

It is these codes that would control the operation of the transmitter, assuming button 4 is [passed, it would send electrical signals to diode 6 and 7.

## 2.3

2.2

#### **INVERTER AND REGISTER**

This unit converts the electrical signals, which is initially made high by the diodes to be low while the low output of the diode becomes high, and it consists of three NOT gates while the Register or latch is a D-type flip-flop (40174).

## Circuit Diagram

Fig. 2b. Inverter and Register.

#### **CIRCUIT ANALYSIS**

At normal stage, the input to the inverter is a high, 1 due to the power from 9v battery, this implies that the three inputs to the inverter at normal stage will be 111(stv), so when button 4 from the switching unit is pressed signal flows from diode 6 and 7, which is fed into the input of the of the inverter.

The pressing of button 1 makes t and s become 00 while v still remains 1, which makes the input to the inverter 001.

The inverter now converts these input at its terminal to 110 at its output terminal feed into the OR gates and Register.

The truth table of the inverter at normal stage and operational stages are shown below.

#### **INVERTER**

## Normal Stage

| Push   | S | T | V |

|--------|---|---|---|

| button |   |   |   |

| SW1    | 1 | 1 | 1 |

| SW2    | 1 | 1 | 1 |

| SW3    | 1 | 1 | 1 |

| SW4    | 1 | 1 | 1 |

| SW5    | 1 | 1 | 1 |

| SW6    | 1 | 1 | 1 |

Table 2a

Operational stage

| Push button | S | T | V | S | $T^1$ | $V^{I}$ |

|-------------|---|---|---|---|-------|---------|

| SW1         | 0 | 0 | 1 | 1 | 1     | 0       |

| SW2         | 0 | 1 | 0 | 1 | 0     | i       |

| SW3         | 0 | 1 | 1 | 1 | 0     | 0       |

| SW4         | 0 | 0 | 1 | 1 | 1     | 0       |

| SW5         | 1 | 0 | 1 | 0 | 1     | 0       |

| SW6         | 0 | 1 | 1 | 1 | 0     | 0       |

Table 2b.

It can be seen from the table above that the output of the inverter when switch 4 (SW1) is pressed is 001, these 3 bits are passed on to the latch through the data bus A from fig. 2b, the OR gates sums up the input from this data bus from the output of the latch or Register, so as to have a logic 1 always, whenever a code is present at the bus A. The truth table of the register is presented below:

Register

| Push button | R | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 |

|-------------|---|----|----|----|----|----|----|----|

| SW1         | 1 | 1  | 1  | 0  | 1  | 1  | 1  | 0  |

| SW2         | 1 | 1  | 0  | 1  | 1  | 1  | 0  | 1  |

| SW3         | 1 | 1  | 0  | 0  | 1  | 1  | 0  | 0  |

| SW4         | 1 | 1  | 1  | 0  | 1  | 1  | 1  | 0  |

| SW5         | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| SW6         | 1 | 1  | 0  | 0  | 1  | 1  | 0  | 0  |

Table 2c.

From the table 2c, R is the output from the OR gate 1, and this is used to reset the receiver logic unit so that the phase difference between the transmission logic unit and the receiver logic is at its minimum.

The Register is chosen for this design to have a delay unit that causes output to follow the input, but delay by a single data input (D) and a clock input. The Register takes the value of D at a specific clock transition, in other words, the Register takes on

the value on the D-lines, with the arrival of the clock pulse, the input data are then transferred to output  $Q_0 - Q_3$ .

Once the transfer of the code has been initiated, any further changes in the input states will have no effect on the output, this way, minimum error is introduced when codes are transferred.

## 2.5 Multiplexer and Johnson's Stepper

A multiplexer is a combinational logic circuit, for the purpose of this project, a multiplexer consisting of AND and OR is used.

Circuit Diagram.

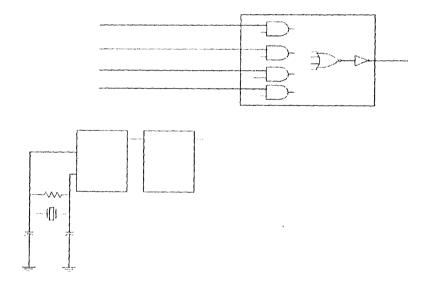

Fig. 2c Multiplexer

As it can be seen from the diagram, the multiplexer has many lines and only are output lines, and at any point in time, only one input line is connected to the output line. The multiplexer thus serves as a data selector.

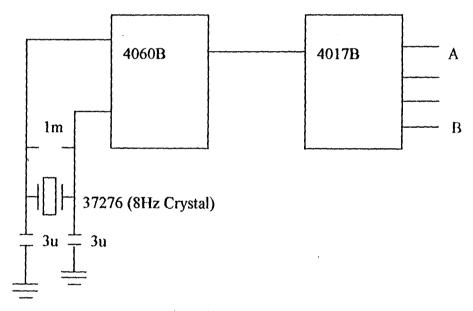

For each of the AND gate to be selected, it has to be controlled or selected by a data select, the data select used in this design is the Johnson's stepper. The operational speed of the stepper is controlled by the crystal oscillator (4060B). This oscillator provides he timing clock pulse for the stepper. The clock pulse also control the operation of the various unit of the system.

The clock pulse used in this project is 80Hz the period is then 0.125s. This is the clock pulse used by the stepper to send bit code. And the total pulse of 0.5s to send 4 bits code.

Fig. 2d Stepper

## THE TRANSFER CONTROL LOGIC

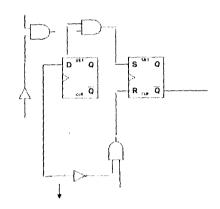

The transfer control logic unit consist of a combination of logic circuits, D and R S flip-flops.

2.6

The transfer control logic unit helps in sending a complete code for a push-button pressed, this is achieved by transferring a single complete cycle when the button is pressed, despite the fact that stepper aims to send code in series of cycles.

Fig. 2e The Transfer Control Logic

From the circuit diagram labeled x in fig. 2b comes from the OR gate 1 of the previous units and it function I already discussed, and it is to notify whether a code is present to the system or not. For the presence of a code x is high 1, and 0 for the absence of code.

The D- type flip-flop acts as a code register, which stores the presence or absence of the last code latched. The output of the D flip-flop is fed into the AND gate 6, the AND gate 6 is high only when the AND gate 5 is open. The 2 inputs of AND gates are clock pulses, that clock the stepper and the last output from the stepper, that notify that

the last code has been transferred by the multiplexer. Therefore, if actually there is a presnce of code as earlier stated, the output of D-type flip-flop will be high and the output of the AND gate 5 will also be high as long as the clock pulse is active high.

As a result, AND gate 6 will be high which now set the RS flip-flop to have a low output at Z through  $\overline{Q}$ .

The output at Z is connected to input at the transmitter, which disenables the transmitter from repeater transfer of signal to the receiver, even if the push button is still pressed after the codes are already transferred. On the other hand, AND gate 7 will generate a low which makes the Reset button to be inactive.

When the codes are present at the label x in fig. 2b, this makes x to have a code 0. the output D-type flip-flop to go low and as a result makes the output of the AND gate 6 to be low and then, the overall output at the AND gate 6 and AND gate 7 will now reset the RS flip-flop for the next codes to be transferred.

## 2.7 TRANSMITTER UNIT

Essentially the transmitter couples the message to the channel, which in this case is the free space through the transmitting antenna. [5]

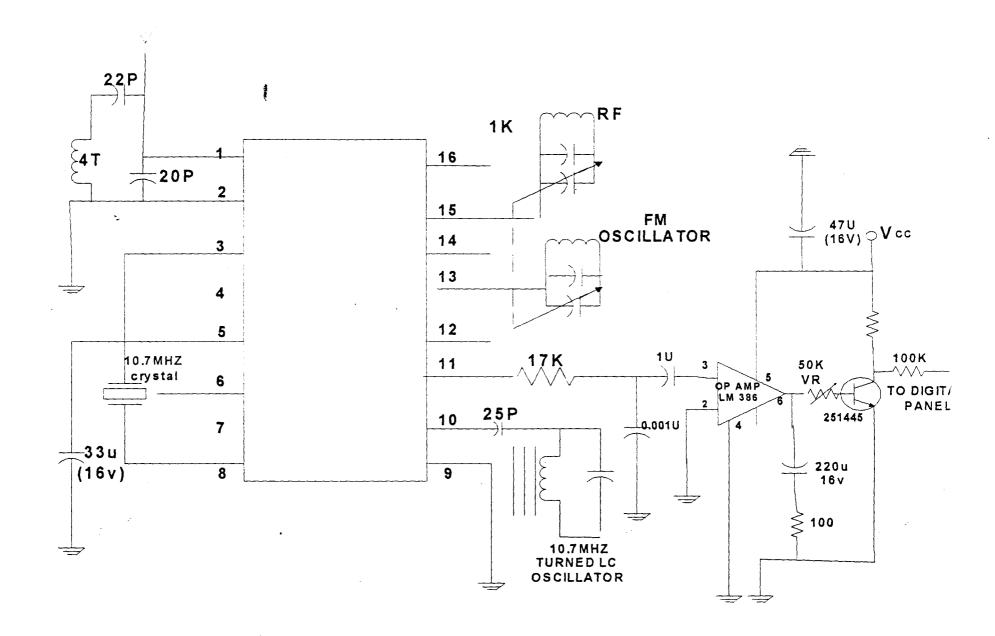

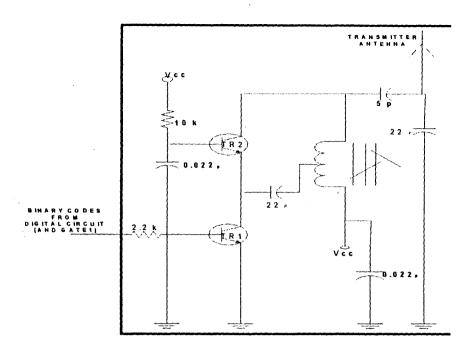

The foregoing design analysis has been on the digital module so far, the transmitter in this project has an analogue circuit, which involves continuous signals.

The transmitter generates frequency from the oscillator, which is amplified, and transmitted if there is presence of codes (high) form the logic circuit and no transmission when there is absence of codes (low) from the logic circuits.

Fig. 2f The Transmitter Circuit.

The transmitter is either activated or deactivated by the logic level of the logic circuits.

For the discussion of the operation of the transmitter push button 4 is pressed from the switching unit, codes 1001 will be serially transferred from the multiplexer to the AND gate, which activates or deactivates the transmitter one after the other by presence of high input from the transfer control logic unit and the active clock input from the timing circuit.

The resonance frequency generated by the LC oscillator in the transmitter is fed to TR2 for amplification before transmission, the frequency generated by the oscillator is fed back by the feed back coupling capacitor C1.TR1 is used as switching element fro the oscillator and it does this whenever there is a signal through its base. Whenever there is a signal at the base of TR1, TR2 is cut-off while TR1 is turned-on, as a result there would be flow of signal to the LC oscillator, which will now generate the frequency.

When the TR1 reaches its saturation point or stage, it is cut-off and its flow of signal through it stops. At this stage, TR2 is turned-on and the frequency generated in the oscillator will now be fed back to TR2 to be amplified and transmitted through then antenna.

R2 and C2 are biasing resistor and capacitor respectively, and they are used to control TR2.

The transmitter only transmits whenever there is presence of 'high' code at the output of the deactivating or activating AND gate.

## 2.8 ANTENNA

An antenna or aerial is a structure that couples the output of a transmitter or the input of a receiver to space, it either converts high frequency current into electromagnetic waves for radiation (transmitting antenna) or converts electromagnetic waves into high frequency current (receiving antenna). [5]

As a result of the important role played by antenna in transmission, it has been employed in this project as a means of transmitting the radio frequency from the transmitter to the receiver.

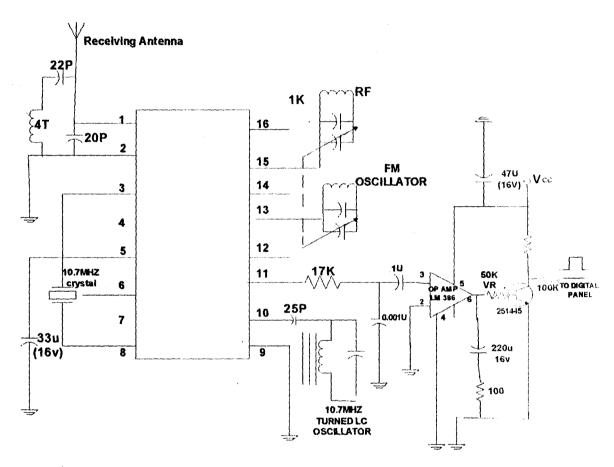

## 2.12 THE RECEIVER

The receiver consists of two modules, the digital and the analogue modules.

The digital modules consist of the flip-flop, crystal controlled oscillator, register, while the analogue part consists of the receiving antenna and the receiver part that does the extraction of the wanted signals.

The circuit analysis is done in units of the whole system for better understanding and for precision.

## 2.9 RECEIVING ANTENNA

Receiving antenna is the first part of the Receiver and its function is discussed in the foregoing analysis.

Basically, the Receiver in a communication system extracts and process the desired signal from various signal received at the channel output, the processing functions include conversion of the selected signals to a form suitable for the output or controlled system, this includes detection and amplification of the received signal level if low.

Fig.2g.TheReceiverCircuit.

From the diagram above, the receiving antenna and passes to the oscillator (FM oscillator) which produces a modulating frequency, the frequency from the FM oscillator will now be mixed by the radio frequency produced from the RE circuit and transmitted back to the KA2297 IC for amplification.

The IC had been turned to a reference frequency of 10.7MHz when it compares with received and mixed frequency, and selects the needed frequency (10.7MHz).

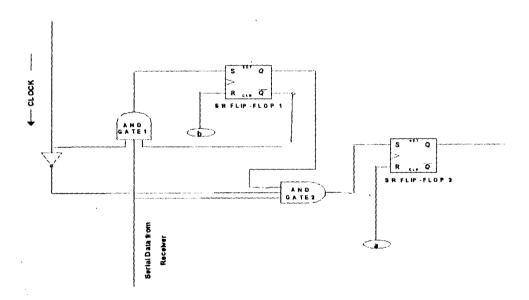

## 2.11 RS FLIP-FLOP

The 2 RS flip-flop used here are 40Band 4013 IC. The 40B is used to reset the receiving system after the completion of transmission from the transmitting part; the 4013 on the other hand are used to correct phase-error between the transmitter and the receiver.

Fig. 2h RS flip-flop

As shown from the fig. 2h flip-flop 1 and flip-flop 2 are enabled or disenabled codes of the different binary bit is used to transmit signal by the transmitter, received by the receiver and finally decoded by the logic circuit of the receiving part.

RS flip-flop are regenerative circuit with 2 active devices design so that one of the devices conducts while the other cuts-off. In this design, they are used to store binary numbers, their respective action is controlled by the AND gate 1 and 2.

The output of the RS flip-flop is then transferred to the next unit of the design of the shift Register.

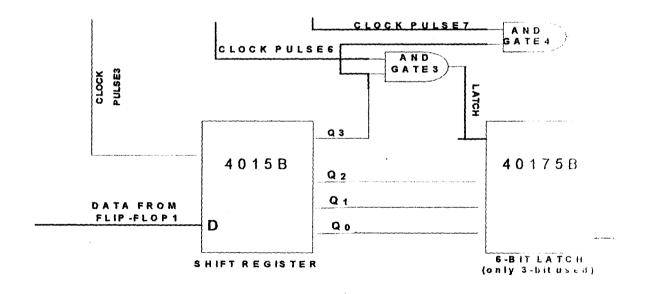

#### 2.12

#### SHIFT REGISTER AND THE LATCH

The shift register used in this project is a 4015B IC while the latch chosen for the design is a 40175 IC.

Fig. 2i Shift Register and Latch

A shift Register is a memory element used to store or transfer binary numbers.

The can be made-up RS flip-flop, D-type flip-flop or JK flip-flop.

For the purpose of this project, a D-type shift register was used, the data input to the Shift Register are serial, that is for any clock pulse generated is entered into the first flip-flop, and the next clock pulse the data is shifted into the next flip-flop as a new data is entered into the first flip-flop, the action is repeated for successive clock pulses until all the data are shift into the flip-flops.

The 40178B is a 6-bit latch but only 3bits of the 6 bits are used in this design.

It should be noted that the number of bits determines the number of flip-flops use in a shift Register, hence for a 4-bit shift, 4 flip-flops are used.

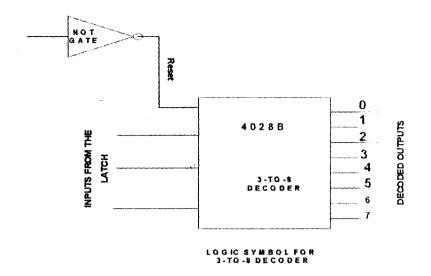

## 2.13 DECODER

Essentially, a decoder is a combinational logic circuit, which provides code conversion; it does this by making only one output line active at a time.

The decoder used for this project is 40288 IC and this is shown in the circuit diagram below:

Fig. 2j 3-to-8 Decoder.

The 3 to 8 decoder has 3 inputs line and 8 outputs. However, for this design only 6 outputs of the 8 outputs is utilized, that is line 0 to 5.

The internal circuitry of the 3 to 8 decoder is the usual combination of AND gates, which all the min-terms and the 3 – input enable lines and the 8 decoded output line.

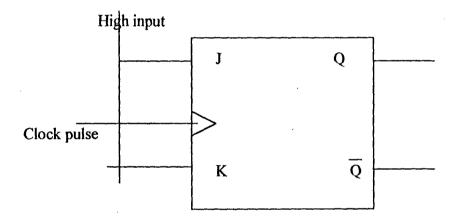

A JK flip-flop is not quite different from the SR flip-flop and the D-type flip being discussed earlier in this project, but it has addition facilities of the SR flip-flop.

JK flip-flop removes the limitation of the indeterminate input of the SR flip-flops.

The JK flip-flop achieves this additional facility by using the Q and Q to steer the input.

Fig. 2k Logic symbol for a JK flip-flop at toggle state.

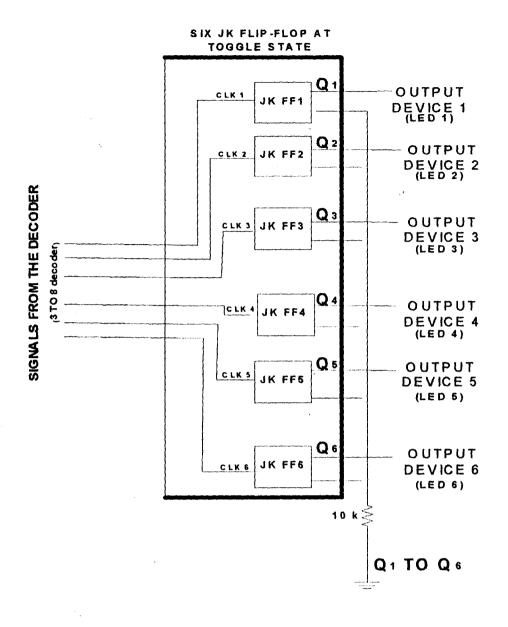

Fig. 21 JK flip-flop.

From the fig. 21 above, it can be seen that both input lines of the JK flip-flop are at toggle state, that is both are high, however, the output Q and Q can only be obtained.

Whenever the clock is enabled.

From the fig. 2h above, the Clock 1 and Clock 6 represent the output lines from the decoder while the Q1 and Q6 represent the output lines from the JK flip-flops.

The input line J and K are connected in such a way that they are both at high states. The output lines Q1 to Q6 are grounded, since they are not utilized for the project.

The output Q1 to Q6 are the outputs used to control the controlled system or output device to be controlled remotely from a distance without the usual connection of cables between the controlling system and the controlled system.

For instance, if the button 4 pressed from the switching unit of the transmitting part, signal is transmitted from the transmitter to the receiver, and the decoder in the receiving part decodes this signal.

This decoded output will now enable any one of the external outputs connected to the system.

The output or system controlled in this project is six light-emitting diodes, which can be turned-on and off by the pressing of a button and another press of the same button respectively.

#### 2.15

#### **CONTROLLED SYSTEM**

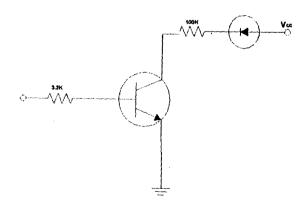

As stated above, the controlled systems in this project are light-emitting diodes.

Fig. 2m Controlled System (LED)

In this project, six LEDs are used to represent the six channels, which can be controlled separately from six switches from the transmitting part.

When the Q output of any of the JK flip-flops is high, the light-emitting diode (LED) connected to this output goes ON, and then goes OFF when Q is low.

#### CHAPTER THREE

#### 3,10

#### INTRODUCTION

In this chapter, the construction of separate unit that makes up the whole system was started, and the separate units were integrated by connecting the unit and sub-system together to yield the project.

### 3.20

## **CHOICE OF LOGIC FAMILY**

It has been a common practice to classify logic families by the circuit configuration of the basic gate technology, the earlier type being Register logic, Resistor transistor logic (RTC) and the transistor logic (DTC).

The early types are being superceded by the following IC logic families, the transistor- transistor logic (TTC) emitter, coupled logic (ECC) and complementary order silicon logic (CMOS).

CMOS are the most popular but use different technology in their manufacture.

Most of the ICs used in this project are CMOS because of the low-voltage nature, however, care should be exercised when handling CMOS devices because they are very susceptible to excessive voltage carried by static electricity and equipment, which are not properly earthed.

#### SYSTEM INTEGRATION

The first stage of construction was done on the breadboard by connecting all the components according to the circuit diagram and powered by a dc 9v battery for testing and error correction.

After error correction and testing the connection were transferred to the Veroboard for permanent soldering.

The casing provided for the project i9s made of plywood, two separate casings were made: one for the transmitter part and the other one for the receiving part also containing the controlled system, the light emitting diodes.

## 3.40 TOOLS USED FOR THE PROJECT CONSTRUCTION

The following were used during project construction:

1. Breadboard

3.30

- 2. Vero board

- 3. Soldering Iron and Lead

- 4. Lead sucker

- 5. Cutter

- 6. Hammer

- 7. Nails

- 8. Digital multimeter

- 9. Drilling machines

## 3.5 TESTING, RESULT AND DISCUSSION

The following test were carried out during construction:

- Testing the output of each unit during construction process by the use of digital multimeter.

- 2. Physical connection of wire between the transmitter and the receiver to confirm if both are working as expected.

- 3. Finally, disconnection of the connection between the transmitter and the receiver to see if the wireless nature has been achieved.

It was discovered that there was transmission between the transmitter and the receiver when the wire was connected between them, but when the wire was disconnected to confirm wireless nature of the project, it was discovered that the transmission was not so perfect, and the tuning of the receiver was adjusted and appreciable distance was observed.

So a switch could be used to control the light-emitting diode from an appreciable distance.

#### **CHAPTER FOUR**

#### 4.0 CONCLUSION

The multi-channel wireless control system was complete. It worth mentioning how fascinating it was when one designs a system, constructs it, and see it working satisfactorily. This project has given a great experience especially in the design, construction of the system.

It has also increased the knowledge and understanding of the use of different kinds of transmitter and receiver circuits.

From the results, it showed the aim and the objective stated in chapter one were achieved since, the principle used in the system worked as expected.

### 4.1 RECOMMENDATION

For the improvement of this project, it is recommended that some sort of feedback should be incorporated in the system, which would notify the transmitter part if the intended controlled system have been controlled or not in order to increase the effectiveness and efficiency of the system.

## 4.2 SUGGESTION

Due to difficulties encountered during the cause of this project, some suggestions have been made for future improvement.

The National Institution of University Education should endeavour to widen the scope of the syllabus of the National Degree programme course so that it will be theoretically and practically oriented.

Because the current syllabus used in school lay more emphasis on the theoretical aspects and neglect the practical aspect and thus make the student unexposed to practical aspect.

Also, government should make provision for standard libraries and research centre where students can go and do their project research and design.

## **APPENDIX**

## Components used for the construction are:

| 1. Resistors (in ohms) | 2. ICs | 3. Capacitors (in farads) |

|------------------------|--------|---------------------------|

| 100                    | 40174  | 0.022p                    |

| 10K                    | 4060B  | 2p                        |

| 80K                    | 4017B  | 5p                        |

| 100K                   | 4022B  | 20p                       |

| 17K                    | 4017B  | 22p                       |

| 1M                     | 4015B  | 25p                       |

|                        | 4028B  | 27p                       |

|                        | 4027B  | 30p                       |

|                        | 4013B  | 47p                       |

|                        | 40B    |                           |

- 4 Switches

- 6 Push buttons

- 5 Diodes

- 9 Low-power diodes

- 6 light emitting diodes

- 6 variable and fixed inductors.

## REFERENCES

- 1. Floyd. Digital Fundamental, 6<sup>th</sup> Edition

- 2. Durell, H.J. Encyclopedia of Technology, vol.11

- 3. D. Dupontel, J. C. Element of digital communication.

- 4. Sparks, R.A. Introduction to Electronics.

- 5. Adediran, Y.A. Telecommunication Principle and Systems.

- 6. Reinaldo Perez. Wireless communication design.