# DESIGN AND CONSTRUCTION OF A METAL DETECTOR

BY

REUBEN. O. EZEH

**REG. NO. 99/8352EE**

A PROJECT REPORT SUBMITTED IN PARTIAL

FULFILMENT OF THE REQUIREMENTS FOR THE

AWARD OF BACHELOR OF ENGINEERING (B. ENG)

DEGREE IN ELECTRICAL/COMPUTER ENGINEFRING.

FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA

NIGERIA

NOVEMBER, 2005.

# **DECLARATION**

I hereby declare that this project has been carried out by me and that it is a record of my research work. It has not been presented in any previous application for a first degree.

RR

7-12-05

REUBEN .O . EZEH

DATE

# **CERTIFICATION**

This is to certify that this project entitled DESIGN AND CONSTRUCTION OF A METAL DETECTOR by Reuben .O. Ezeh, meets the regulations governing the award of the degree of Bachelor of Engineering (B.Eng) of the Federal University of Technology, Minna and is approved for its contribution to Knowledge and literacy presentation. MR. U.S Dauda Signature and Date Project supervisor Signature and Dat Engr. M. D Abdullahi Head of Department of Elect / Computer Engineering Engr. Dr. J.D Jiya Signature and Date

**External Examiner**

# **ACKNOWLEDGEMENT**

Firstly special thanks to the Almighty God for his mercies. Also, I thank my apervisor Mr. U.S Dauda who took time to supervise and guide me during this project

I am indebted to my parents Ichie and Mrs R.M Ezeh, for their wonderful love. inancial support and arrangement without their support I would not have got to this point in fe.

Furthermore, I will like to thank my friends Terence Adams, Chinwe Ezeh, Uju Ezeh, Magdalene and Bukky who helped me during this project.

# **DEDICATION**

I dedicate this work specially to my mother Mrs. C. N. EZEH.

٧

# **ABSTRACT**

This project is a record for designing a metal based on the method electromagnetic induction.

Electromagnetic induction is a phenomenon whereby an electromotive force, hence urrent is induced in a coil when magnetic flux is linked to it. This causes the inductance of he coil to be increased.

An increase in the inductance of a coil is caused by the presence of a metal, hence this eads to a drop in frequency.

The aim of this project which is to design a metal detector, is achieved by designing a ircuit sensitive to a drop in frequency.

The metal detector can be used for land mine detection and also for archeological exploration.

# TABLE OF CONTENTS

| ITLE                                      | i    |

|-------------------------------------------|------|

| EDICATION                                 | ii   |

| ERTIFICATION                              | iii  |

| DEDICATION                                | iv   |

| CKNOWLEDGEMENT                            | v    |

| ABSTRACT                                  | vi   |

| ABLE OF CONTENTS                          | vii  |

| CHAPTER ONE                               | PAGE |

| 1 INTRODUCTION                            | 1    |

| 2 IMPORTANT APPLICATION OF METAL DETECTOR | 2    |

| .3 AIMS OF PROJECT                        | 2    |

| CHAPTER TWO                               |      |

| .1 LITERATURE REVIEW                      | 3    |

| CHAPTER THREE                          | PAGE |

|----------------------------------------|------|

| SYSTEM DESIGN                          | 8    |

| 2 OSCILLATOR                           | 9    |

| 3 SAMPLER                              | 10   |

| 4 LATCH                                | 14   |

| 5 CONTROL UNIT                         | 17   |

| 5. 1 RC OSCILLATOR                     | 17   |

| 6 FREQUENCY DIVIDER                    | 18   |

| 7 COUNTER                              | 22   |

| 8 OUTPUT UNIT                          | 22   |

| 9 THE OR GATE                          | 23   |

| 10 CONSTRUCTION AND TESTING            | 26   |

| 11 CONSTRUCTION                        | 27   |

| 11. 1 STEPS CARRIED OUT IN FIRST STAGE | 27   |

| 11.2 STEPS CARRIED OUT IN SECOND STAGE | 28   |

| 12 TESTING                             | 28   |

| 13 OBSERVATION                         | 28   |

| 14 POWER SUPPLY                        | 28   |

| 15 EXPLANATION OF CIRCUIT DIAGRAM      | 29   |

| 15.1 THE FREQUENCY SAMPLER             | 30   |

# **Design and Construction of a Metal Detector**

#### CHAPTER ONE

#### 1.1 INTRODUCTION

Following the discovery towards the tail end of the Stone Age, man in conscious effort to better himself, began to evolve contrivances from this relatively new discovery and later popularized by the then struggle for survival and supremacy, creating a problem of security and safety

However the constantly growing security problems in private as well as public sector has made the desire for security of mans basic needs. These constantly increasing danger potential as well as the growing intelligence of the criminal mind have necessitated the need for a special technical equipment to aid the protection of lives and properties as well as to ensure that the privacy of those to the protected is not put into jeopardy. Intruder detection faces not only the importance challenge of reducing threats to lives and properties but also in reducing the delay times as well as the reaction time of security personnel. This means that it must be ensured that damage can be prevented or minimized after the danger has been detected.

All intrusion detectors make use of sensors. The sensor, which is based on very different basic physical principles, indicates the presence of an "intrude" by opening alarm contacts in closed circuit signal lines. This leads us to another form of security in detecting various forms of intrusion using a metal detector.

Metal detectors are devices used to locate or to detect the presences of a metal or metallic object. The metal detector designed in this project makes use of electromagnetic

determing component. The oscillator operates at a particular frequency. The output frequency from the oscillator is fed into the sampler, which samples the frequency and passed it on to a latch. This latch holds this frequency and gives an output based on whether the value of its input changes or remains the same. The output frequency of the oscillator is synchronized with the sampler. The output of the latch is connected to an alarm. The sampler, the latch as well as the alarm are all connected to a mini controller. The function of the controller is to monitor and control the operation of the whole unit. The control unit senses any change in the output frequency of the oscillator through the response of both the sampler and the latch.

If a metallic object is brought close to the inductor, which is the frequency-determing component of the oscillator, there will be a magnetic field generated around the metal which will distort the original magnetic field around the inductor. This will cause the frequency of operation of the oscillator to be changed. This change in the output frequency of the oscillator will be sensed by the sampler and the latch. The control unit which is sensitive to any change in the sampler and the latch, will trigger the alarm by transmitting a signal to the output device.

# 1.2 Some important applications of metal detectors are:-

- i) Item recovery: to help an individual search for a lost item such as a piece of jewelry, coins e t c

- ii) Engineering: To locate pipes and cables buried inside the ground and wall.

- iii) Building security: To screen people entering a particular building such as school, officers, prisons e t c

- iv) Event Security: To screen people entering a sporting event, concert or other large gathering of people.

- iii) Airport security: To search people before allowing them access to the boarding area and plane.

- iv) Treasure hunting: For Archeological exploration to find metallic items of historical significance.

- v) Geological Research: To detect metallic composition of soil

# Aims of the project

- i) To design and construct an effective means of detecting dangerous weapons made of metal so as to reduce the rate of crime in the society.

- ii) To construct a metal detector that can be used for treasure hunting.

- iii) To construct a metal detector using the principle if magnetic induction.

# **CHAPTER TWO**

#### 2.1 Literature review

There are five main ways of detecting metals.

- 1) Beat frequency oscillator (BFO)

- 2) Off resonance

- 3) The magnetometer

- 4) Pulse induction

- 5) Induction Balance

- 1) The MAGNETOMETER: this works by detecting small anomalies in the earth's magnetic field strength. This type of metal detector is fascinating, but unless for treasure hunting, since it can also only detect famous objects.

- 2) **OFF-REASONANCE**: this type operates by detecting, the small change in the search coil inductance, which occurs when metal object is present. It suffers from a basically poor sensitivity.

- heterodyne circuits: this is the simplest way to detecting metal, but it suffers from poor sensitivity. It operates just like the off-resonance by detecting small change in the search coil inductance, which occur when a metal object is present.

Thus, this metal detector works on beat frequency oscillation principles. When the output from the two oscillations are mixed together, two total different frequencies are produced. One is the sum of the frequency of the individual oscillators, the other are the difference in the frequencies. The latter is made use of, to beat or mix the output from the two oscillators in a mixer to obtain the difference frequency called the beat frequency. In the working state of this device, the operation of the BFO metal detector circuit is based on super heterodyning principle used in "superhet" receivers. In the absence of a metal, this device produces a zero beat frequency and thus no sound from the loudspeaker. But when a metal is brought around (within) its capture range, the magnetic flux of this metal changes its inductance, making the beat frequency not to be zero and then loudspeaker being activated sounds after the mixer / detector output gas been amplified to a reasonable level to drive the loudspeaker.

4) PULSE INDUCTION: - The pulse induction metal detector uses a simple coil as both transmitter and receiver, or they have two or even three coils working together. This device operates by exposing the ground to powerful, short bursts (pulses)

of current through its coil of wire. Each pulse generates brief magnetic field. It also listens between pulses for signals due to eddy current set up in any metal object present in the field. These types of metal detectors are very sensitive but the most expensive detector type available. Despite their sensitivity, they have a couple of important drawbacks; their battery consumption is heavy due to the power required by the pulse transmitter, and they are extremely sensitive to even tiny famous objects. Their use is primarily restricted to beach searching, where object are likely to be buried at considerable depths, and where large holes can be easily and rapidly dug.

- INDUCTION BALANCE: this type of detector is also known as the very low frequency or Audio frequency metal detector. It has become more or less the standard general-purpose detector for the both serious treasure hunters and detecting hobbyist alike. It has two distinct coils in its search coil head; the Driven coil (the transmitting coil) is fed with a signal which sets up an alternating field around it. The other coil (pick up or receiving coil) is placed so that normally the field around it balances and it has no electrical output. A metal object approaching the coil will distort the field, resulting in an imbalance such that the pick up coil will produce an electrical output. This can be amplified and used to inform the operators, of a "find" in a variety of ways. Frequently in simple detectors an audio modulated transmitted signal is used, the output from the pickup coil then amplified and demodulated like an Am (Amplitude Modulated) audio signal. There are many possible coil arrangement, but most detectors available today use one of the two common coil arrangements listen below

- i) "Wide scan" coil arrangement, in which case its most sensitive area extends right across the coil.

#### CHAPTER THREE

# 3.1 SYSTEM DESIGN

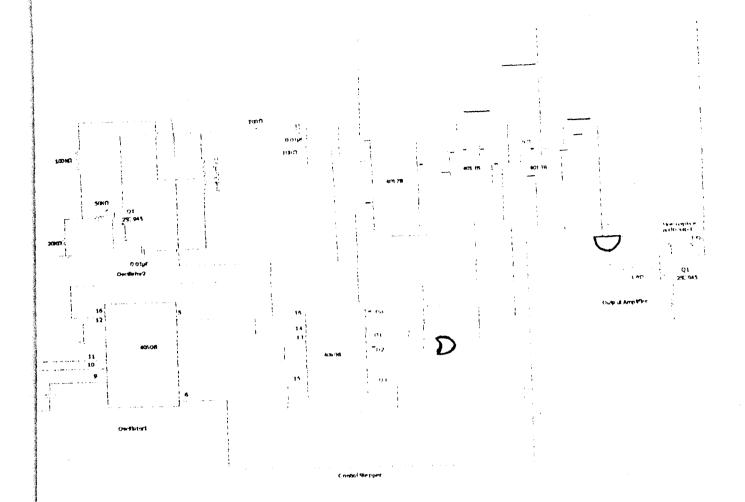

The unit can be illustrated using the above block diagram.

#### 3.2 OSCILLATOR

An oscillator is an electronic circuit that generates signal, which is in a waveform. Within nearly ever electronic instrument, it is essential to have an oscillator or waveform generator of some sort. Apart from the obvious case of signal generator, a source of regular oscillation is necessary in any cyclical measuring instrument or any instrument that initiates process and in any instrument whose function involves periodic states or periodic waveforms.

We have RC, LC and crystal types of oscillator. Due to the purpose of this project an LC oscillator is going to be used. In an LC oscillator, the indicator, L and the capacitor, C. constitute the frequency determining components of the oscillator. The LC type of oscillator is suitable for high frequency signals generation.

A typical LC oscillator can be illustrated as shown below

FIGURE 3.2 An LC Oscillator

It is the function of the oscillator to generate signal at a particular frequency. The frequency at which the generated signal operates is changed as soon as a metallic object is brought close to the inductor of the oscillator. Since inductor is a frequency determining component of the oscillator. The signal generated is being connected to the sampler as shown in the block diagram figure 2.1 above.

#### 3.3 SAMPLER

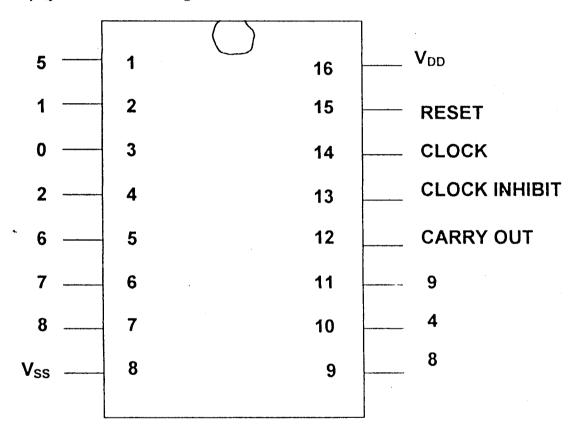

The CD4017 IC (integrated circuit) is used as sampler in this project. The IC is capable of working as counter.

Counters are just flip – flops connected together to perform counting operations.

The number of flip – flops used and the way in which they are connected determine the number of states as well as the specific sequence of states that the counter goes through during each complete circle

Counters can be classified in two ways according to the way they are clocked. These are asynchronous counters and synchronous counters. In asynchronous counters, the first flip flop is clocked by the external clock pulse and then each successive flip – flop is clocked by the output of the preceeding flip – flop.

In synchronous counters, the clock input is connected to all the flip-flops so that they are clocked simultaneously. Within each of these two categories, counters can be classified by the number of states or the number of flip flops in the counter.

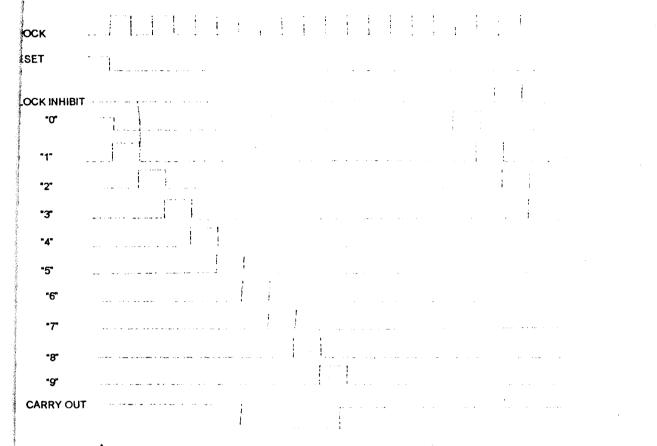

The CD4017 IC is a synchronous decade counter with five flip – flops in its internal circuitry. It is a five stage Johnson counter having ten decoded outputs. Inputs include a CLOCK, a RESET and a CLOCK INHIBIT signal. Schmitt trigger action in the clock input circuit provides pulse shaping that allows unlimited clock input pulse rise and fall times.

These counters are advanced one count at the positive clock signal transition if the CLOCK INHIBIT signal is low. Counter advancement via the clock line is inhabited when the CLOCK INHIBIT signal is high.

A high RESET signal clears the counter to its zero count. Use of the Johnson counter configuration permits high – speed operation, 2 – input decode – gating and spike

free decoded outputs. The decoded outputs are normally low and go high only at their respective decoded time slot. Each decoded output remains high for one full clock cycle.

A CARRY OUT signal completes one cycle every ten clock inputs cycles and is used to ripple – clock the succeeding device in a multi device counting chain.

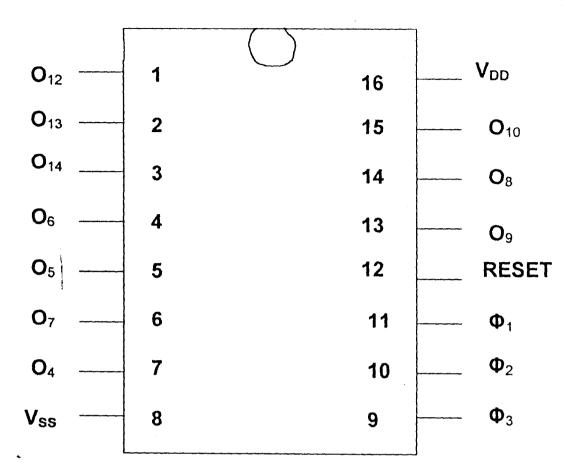

The CD4017 IC functions as decade stepper with ten decoded outputs for this particular project. The terminal diagram of CD4017 is as shown below.

FIGURE 3.3A TERMINAL DIAGRAM OF CD4017 IC

FIGURE 3.3B TIMING DIAGRAM CD4017 FUNCTIONING AS DECADE STEPPER

| O <sub>0</sub> | O <sub>1</sub> | 0, | Ο, | O <sup>4</sup> | O, | $\mathbf{O}_6$ | O <sub>7</sub> | $O_8$ | O |

|----------------|----------------|----|----|----------------|----|----------------|----------------|-------|---|

| 1              | 0              | 0  | 0  | 0              | 0  | 0              | 0              | 0     | 0 |

| 0              | 1              | 0  | 0  | 0              | 0  | 0              | 0              | 0     | 0 |

| 0              | 0              | 1  | 0  | 0              | 0  | 0              | 0              | 0     | 0 |

| 0              | 0              | 0  | 1  | 0              | 0  | 0              | 0              | 0     | 0 |

| 0              | 0              | 0  | 0  | 1              | 0  | 0              | 0              | 0     | 0 |

| 0              | 0              | 0  | 0  | . 0            | 1  | 0              | 0              | 0     | 0 |

| 0              | 0              | 0  | 0  | 0              | 0  | 1              | 0              | 0     | 0 |

| 0              | 0              | 0  | 0  | 0              | 0  | 0              | 1              | 0     | 0 |

| 0              | 0              | 0  | 0  | 0              | 0  | 0              | 0              | 1     | 0 |

| 0              | 0              | 0  | 0  | 0              | 0  | 0              | 0              | 0     | 1 |

FIGURE 3.3C TRUTH TABLE OF CD4017 IC FUNCTIONING AS

A DECADE STEPPER

#### 3.4 LATCH

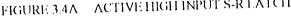

The CD4013 IC is used as S - R latch in this unit. Latch is a type of bistable storage device that is normally placed in a category separate from that of flip flops. Latches are basically similar to flip – flops because they are both bistable devices that can reside in either of two states by virtue of a feedback arrangement, in which the outputs are connected back to the opposite inputs. The main difference between latches and flip-flops is in the method used for changing their state.

We have an S - R type Latches and D- Type latches.

S-R latch, which is the type used in this unit is a type of bistable multivibrator. An active high input S-R (SET – RESET) latch is formed with two cross – coupled NAND gates. In both cases, the output of each gate is connected to an input of the opposite gate. This produces the regenerative feedback that is characteristics of all multivibrators. The active high S-R latch and the active low S-R latch can be illustrated with the logic diagrams shown below.

Q Q FIGURE 3.4A ACTIVE HIGH INPUT S-R LATCH

S

FIGURE 3.4B ACTIVE LOW INPUT S-R LATCH

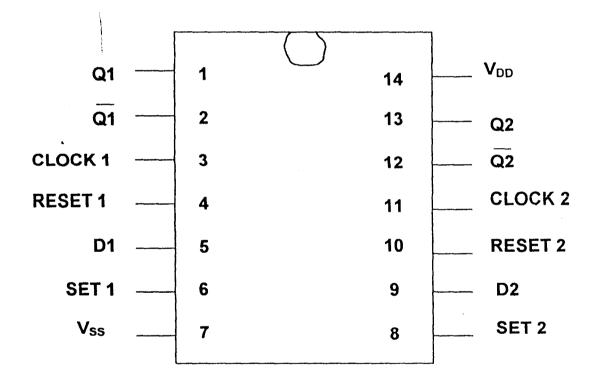

The CD4013 IC is used as the storage device in this unit consists of two identical independent data – type flip-flops. Each flip-flop has independent DATA, SET, RESET and CLOCK inputs as well as Q and Q outputs. These devices can be used for shift register applications and by connecting the Q output to the data input, for counter and toggle applications. The logic level present at the D input is transferred to the Q output during the positive going transition of the cock pulse. Setting or resetting is independent of the clock and is accomplished by a high level on the SET or RESET line respectively.

The terminal diagram is as shown below

FIGURE 3.4C TERMINAL DIAGRAMS FOR CD 4013 IC

#### 3.5 CONTROL UNIT

The control unit consists of a crystal oscillator connected to a frequency divider circuit. It also consists of a counter.

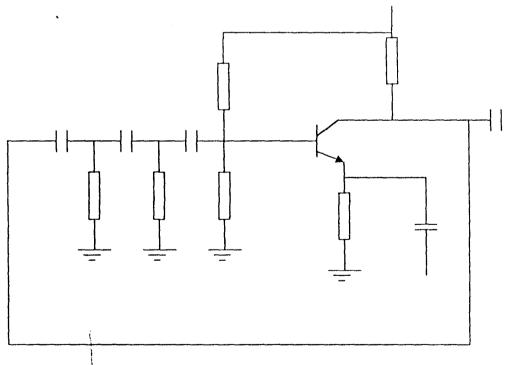

#### 3.5.1 RC OSCILLATOR

Figure 3.5A shows a transistor phase shift oscillator, which uses a three – section R – C feedback network fro producing a total phase shift of 180 – degrees in the signal feedback to the base. Since CE amplifier produces a phase reversal of the input signal, total pahse shift becomes 360 – degrees which is essential for regeneration and hence for sustained oscillation. Values of R & C are so selected that each RC section produces of phase advance of 60 degrees. It is found that phase shift of 180 degree occurs only at one frequency which becomes the oscillator frequency.

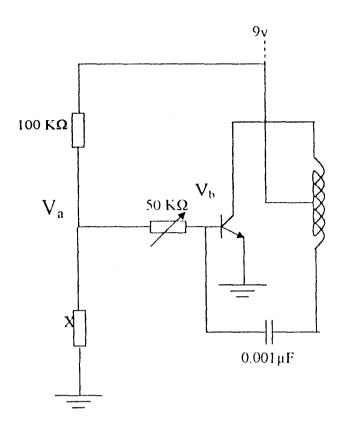

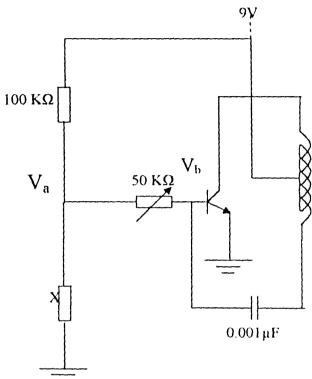

FIGURE 3.5A RC OSCILLATOR

#### 3.6 FREQUENCY DIVIDER

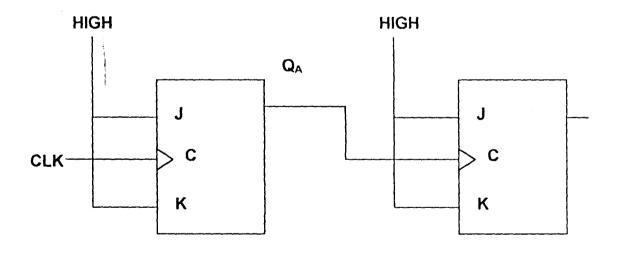

The CD4060 IC is used in this unit as frequency divider. It works based on the principle of J – K type flip-flop (toggle state)

The J-K flip – flop is versatile and is perhaps the most widely used type of flip – flop. The J and K are the designations for the inputs. The functioning of the J-K flip – flop is identical to that of the S-R flip – flop in the SET, RESET and no-change conditions of operation. The difference is that the J-K flip-flop has no invalid state, as does the S-R flip-flop.

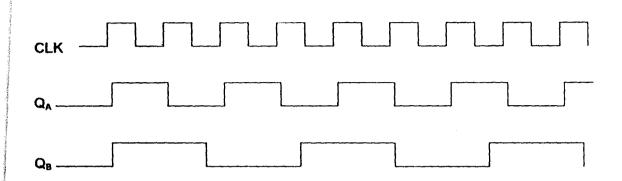

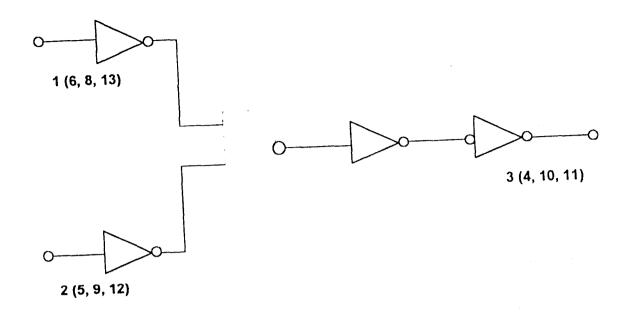

When a pulse waveform is applied to the clock input of a J - K flip flop that is connected to toggle (J = K = 1) the Q output is a square wave with one – half frequency of the clock input. Thus a J - K single flip – flop can be applied as a divide by 2 devices. Also two J - K single flip – flop can be applied as a divide by 4 devices. Two J - K flip flops functioning as a divide by 4 devices is illustrated below.

FLIP FLOP A

FLIP FLOP B

FIGURE 3.6B EXAMPLE OF TWO J – K FLIP-FLOPS USED TO DIVIDE THE CLOCK FREQUENCY BY FOUR

The CD4060 IC consists of an oscillator section and 14 ripple carry – binary counter stages. The oscillator configuration allows design of either RC or crystal oscillator circuits. A RESET input is provided, which resets the counter to all – 0's state and disables the oscillator. A high level on the RESET line accomplishes the reset function. All counter stages are master slave flip flops. The state of the counter is advanced one step in binary order on the negative transition of  $\phi_1$  (and  $\phi_0$ ). All inputs and outputs are fully buffered. Schmitt trigger action on the input pulse line permits unlimited input – pulse rise and fall times. The terminal diagram is as shown below.

FIGURE 3.6C TERMINAL DIAGRAM FOR CD4060 IC

#### 3.7 COUNTER

The counter is constructed by using the CD4017 IC, which is a five stage decade counter with ten decoded outputs. The principle of operation of CD4017 IC has earlier been described above.

#### 3.8 OUTPUT UNIT

The output unit for this project uses an alarm system. It consists of a D - type latch and earphone. The Q output of the latch is ORed with a suitable audio frequency from output of the Frequency divider (CD4060 IC)

D – Type latch is a type of latch that has only input in addition to EN. This input is called the D (data) input. When the D input is high and the EN input is high, the latch will SET. When the D input is low and EN is high, the latch will RESET. In other words, the output Q follows the input D when EN is high.

# 3.9 THE OR GATE

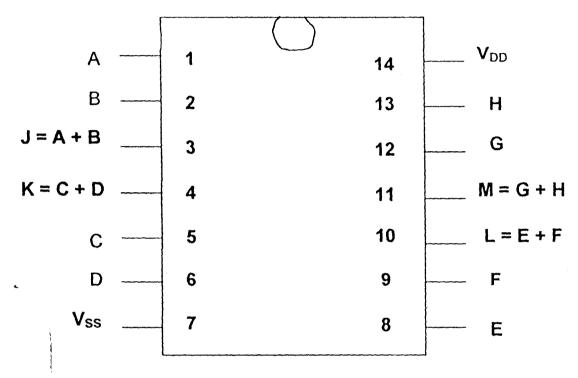

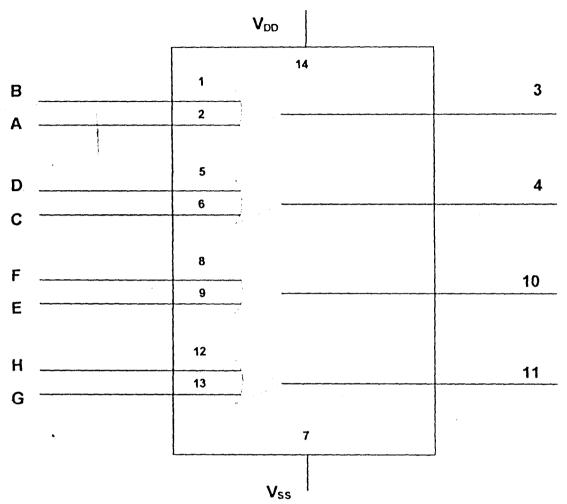

CD4071 IC is a quad 2 - input OR gate. It provides the system designer with direct implementation of the positive - logic OR function and supplement the existing family of CMOS gates.

FIGURE 3.9 TERMINAL DIAGRAM FOR CD4071 IC

FIGURE 3.9B FUNCTIONAL DIAGRAM OF CD4071 IC

FIGURE 3.9C LOGIC DIAGRAM OF CD4071 IC

#### 3.11 CONSTRUCTION

The initial construction was done on the breadboard. This involved arrangement of components according to the circuit diagram. Power was supplied using a 9v dry cell battery.

The second stage was the transferring the components from the breadboard on to the Vero board and soldered.

The instruments used at this stage are:

- 1) Breadboard

- 2) Vero board

- 3) Jumper wires

- 4) Soldering iron

- 5) Soldering led

- 6) Soldering sucker

- 7) Multimeter

- 8) Cutter

#### 3.11.1 Steps carried out at the first stage:

- ✓ The coils were wounded on a non metallic object, which in this case is plywood

- The terminals of the coils were then connected to the oscillator circuit, which is connected to the breadboard according to the circuit diagram.

- The sampler circuit was arranged on the breadboard by connecting the legs of the CD4017 IC to the appropriate places

- The latches were arranged on the breadboard by connecting the legs of the CD4013IC to the appropriate places.

- The control unit was arranged by connecting the crystal oscillator, the CD4060 IC and the CD4017 IC on the breadboard according to the circuit diagram shown at the end of chapter three.

- ✓ The buzzer was also connected according to the circuit diagram

- ✓ The resulting circuit was provided using a 9v battery.

#### 3.11.2 Steps are carried out in the second stage

All the units connected on the breadboard were transferred on to the Vero board accordingly. The power led was extended out.

#### 3.12 TESTING

Components used in testing includes

- ✓ A metallic object

- ✓ An earphone

The buzzer was used as the output device from which we can hear alarm sound, while the metallic object serves as the object to be detected using the metal detector.

The metallic object was brought close to the coils that form the inductive component of the LC oscillator.

#### 3.13 OBSERVATION

It was observed that when the metallic object was brought close to the coil, there was a sound output heard from the earphone.

#### 3.14 POWER SUPPLY

The power supply unit used in this project is chosen to be the one that is compact, cheap and easy to access. In view of this the power supply has been chosen to be a dry cell battery of 9 volts and of moderate current rating.

#### 3.15 EXPLANATION OF CIRCUIT DIAGRAM

The circuit is divided into seven main units or sub – circuits. They work together to achieve the forward task of metal detection through frequency sampling. The technique is achieved by the use of complementary metallic oxide semi – conductor (CMOS) logic. The use of such leading logic provides an enhanced mode of digitizing the circuit.

The first unit is the oscillator. It is an LC oscillator (a simple conventional type) with a limited number of components. The oscillator serves as the input of the whole circuit. By making the inductor side of the circuit external, any alteration to the coil simply varies the resultant frequency of the oscillator. The frequency output of the LC oscillator can be estimated with the frequency formula involving only the inductor and capacitor as variable parameters.

$$F = 1/2\pi\sqrt{LC} \qquad \qquad L = \text{value of inductor used} \qquad \qquad F = 3700 \text{Hz}$$

$$C = \text{value of capacitor used} \qquad \qquad C = 0.001 \, \mu\text{F}$$

$$L = \frac{1}{2\pi 3700} \times \frac{1}{0.001 \, \mu} \times \frac{1}{2\pi 3700} \times \frac{1}{2\pi 37$$

= 1.85H

The formula can be simply explained by the fact that for every increase in the value of the inductance or capacitance in the circuit the frequency drops. And a decrease causes an opposing effect to the early result. Therefore, the frequency output from the oscillator is inversely proportional to the value of both the capacitance and inductance. In the design, the capacitance is kept constant. So the only parameter that varies the frequency output of the oscillator is the inductance.

Moreover an inductor or coil responds to metallic influence in its electromagnetic region. For instance putting a metal close to a closed circuit inductor causes the inductance to vary or increase. And by putting the metallic object away the inductance drops down. For the circuit the inductor in the oscillator serves as the metal sensor. The metallic influence on the coil varies or alters the output frequency of oscillator 2.

The oscillator 2 has a  $100 \mathrm{K}\Omega$  resistor for the base bias. Also incorporated in the circuit is a current variable resistor for the base. The resistor serves for altering the base current and slightly the frequency of the oscillator. The technique enhances the frequency adjustment of the oscillator. Another resistor  $20 \mathrm{K}\Omega$  is connected to the ground and base of transistor Q1. The resistor alongside with the  $100 \mathrm{K}\Omega$  behaves as a potential divider to supply a voltage around 0.7V for the base of the transistor.

The output of the oscillator to the other stages or units passes through a RC filter.

The filter links the oscillator to a frequency sampler.

# 3.15.1 The frequency sampler

It is designed to sample the incoming frequency. It simply shows how high or low. In other words it indicates whether the frequency from the oscillator 2 has diverted from the initial null setting. The sampling result is through terminal 7 of the 4017B. The clock input of the integrated circuit is pin 14 and the result is connected to the control

stepper. At this leading terminal, the control of the sampler's input is achieved. For the circuit enabling pulse is fed into the terminal (reset) from the control stopper. The operation results to a timing that allows a specific or constant arte of sampling. For more clarity, the sampling ratio is constant despite the value of the incoming frequency of oscillator 2, so that whenever the incoming frequency is low or high it is recognized through terminal 7 of the frequency sampler.

For at normal state or setting, the pin 7 is high after sampling enabling pulse goes high. So that the control latch Q output becomes HIGH logical level, while the  $\overline{Q}$  is low. But assuming a metal is brought near the window (sensor), the frequency output of the oscillator drops and results in to 5the pin 7 having a low logical state of sampling. In this case,  $\overline{Q}$  retains a low logical level and  $\overline{\overline{Q}}$ , the reverse.

The control stepper is designed to put the whole circuit in a well organized working pattern. It is done by the 4017B and in the next stage, the output latch is checked to store result from the sampling latch Q output. This last command is attributed to the resetting of the sampling latch so far as to start a new step of operation. The operation results into a cycle and done at a very high speed which is governed by the oscillator 1.

Oscillator 1 is designed based on the 4060B. It is the heart of the circuit, because it feeds the whole circuit with two breathing pulses. One pulse goes for the control stepper and the other for the audio alarm.

The frequency of operation of the oscillator is

Fo =

$$\frac{1}{2.3 \text{RC}}$$

=  $\frac{1}{2.3 \times 33 \times 10^{-3} \times 100 \times 10^{-12}}$  = 1.31.75KHz

And the frequency output for terminal 5 is

Fpin5 =

$$\frac{\text{fo}}{2^5}$$

=  $\frac{131.75\text{k}}{2^5}$  = 4117.19Hz

For terminal 6 (the audio alarm) is

Fpin6 =

$$\frac{\text{fo}}{2^7} = \frac{131.75 \text{k}}{2^7} = 1029.3 \text{Hz}$$

The formula is based on the manufacturer's data sheet of the integrated circuit

The control stepper staying or period of clock pulse is

To =

$$2 \times (3) = 0.00155s$$

Fpin5

Moreover, the 2 – input OR gate at the control stepper stage is designed to sum up the two inputs involved to the enabling terminal of the frequency sampler. It helps to disable the sampler whenever the operation is either output latch clocking or sampling latch resetting.

The output latch gives the final logical description of the environment around the sensor. At correct initial adjustment the Q output of the output latch is at a low logical level, it shows that the device is away from the external electromagnetic or metallic influence. But whenever the output changes, high level logic, it indicates that a metallic object is extremely close to the sensor. The Q output is connected to a light emitting diode (LED) that shows that there is a metallic influence on the device by the switching on of the indicator. Also, the same input is connected to one of the inputs of a 2 – input AND gate.

The output enables the AND gate, by allowing the passage of the frequency or pulse from terminal 6 of the oscillator 1 into the output amplifier (a single NPN transistor) that connects the amplified audio frequency to a mono ear piece. Moreover, the audio alarm sounds whenever a metal is detected.

The range or sensitivity of the device is around 5cm, and lower for high effectiveness

How the value of X was gotten

Ic =5mA- So that we can high enough swing (amplitude variation) at the collector to the input of the 4017

And to also keep the transitor in the linear region And also because the circuit is a low power oscillator

Now

$$V_{bc} = 0.7v$$

$I_c = 5 \text{ mA}, h_{fc} = 250.$

$I_b = \underbrace{5 \times 10^{-3}}_{250} = 20 \times 10^{-6} \text{A}$

For

$$R_b = \underline{V_a - V_{bc}}$$

$I_b$

$$40 \times 10^3 \times 20 \times 10^{-6} = V_a - 0.7$$

$$0.8 + 0.7 = V_a$$

$$V_a = 1.5 \text{ V}$$

To get our potential divider

A potential of 9V is applied to the  $100k\Omega$

$$1.5 = \frac{X}{1.00}$$

$$(1.67 \times 10^{-1}) (X+100k) = X$$

| HAPTER FOUR      | PAGE       |

|------------------|------------|

| CONCLUSION       | 3 <b>4</b> |

| 2 RECOMMENDATION | 3 <b>6</b> |

| HATER FIVE       |            |

| 1 REFERENCE      | 3 <b>7</b> |

$$X - 1.67 \times 10^{-1} X = 16.7$$

$0.833 X = 16.7$

$X = 16.7$

$0.833$

$=20.048k\Omega$

FIG 3.15 CIRCUIT DIAGRAM OF METAL DETECTOR

#### CHAPTER FOUR

#### 4.1 CONCLUSION

The metal detector was found to be sensitive to change in frequency, which is due to digital circuit employed in the designed of the unit.

Also from the result obtained, it has shown that aim of the project stated earlier in chapter one was achieved since the principle used for the system work as required.

#### 4.2 RECOMMENDATION

At the end of the work, the recommendations were made with respect to the difficulties encountered during the project work.

- There should be proper monitoring and assistance for students working on their projects.

- 2) There should be a proper project course schedule in the University syllabus to get students prepared for their final project work

- 3) The University laboratory should be well equipped with the equipments that will help in their project work

- 4) Any one willing to take on this project work for development should take into consideration.

# CHAPTER FIVE

# 5.1 REFERENCES

Reference was made to a number of books and websites during all phases of this project to facilitate the entire process. The following is the list of references made:

- [1] T.L. Roger, Digital Electronics: principle and applications, *Glencoe McGraw Hill, Woodland Hills, California*, 1999, pp.154-164.

- [2] B.L. Theraja, Electrical Technology: S.Chand and Company Ltd, Ram Nagar, New Delhi, 1999.pp541-522.

- [3] www.electronicstoru.com

- [4] www.howstuffworks.com

- [5] www.espanprama.com

- [6] www.eircuitlab.com