### DESIGN, CONSTRUCTION AND TESTING OF A

## ZONE SECURITY SYSTEM

BY

### **MUHAMMAD HASSAN**

## **MATRIC NO. 2003/15403EE**

A PROJECT SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF DEGREE OF BACHELOR OF ENGINEERING, IN THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING, FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA, NIGER STATE.

#### **NOVEMBER 2008**

### DECLARATION

I hereby declare that this work was carried out by me. To the best of my knowledge and belief, this work has never been submitted either in Federal University of Technology Minna, or any other institution for the award of any degree of certificate.

Muhammad Hassan

Date

### CERTIFICATION

This is to certify that this project titled "Zone security system" was carried out by MUHAMMAD HASSAN. It satisfies the regulations/standards governing the award of the degree of bachelor of Engineering in Electrical and computer engineering, School of Engineering and Engineering Technology of Federal University of Technology, Minna, Niger state.

**CERTIFIED BY**

J Ajiboye (MR) Supervisor

Yunus Adediran (DR) Head of Department Date

Date

Date

External supervisor

#### ACKNOWLEDGEMENT

The history of man cannot be made from nature apart from his surrounding and people around him. Certainly there some people that my history cannot be told without them being mentioned.

It is on the note that I give thanks to the Almighty Allah who has been faithful in reserving my life to witness the day.

I am also acknowledging the great contribution done by my supervisor, Mr. J. Ajiboye for his effort in overseeing the work and making valuable suggestion towards the completion of this work. I must confess that it was a rare privilege to be his student.

This project was sincerely made possible through the unending support of my parents Mallam and Mallama Muhammad Zubairu, who has laboured so much to see that I succeeded even at times when it was not convenient for them. I also say a big thanks to my step-mum (Mallama Aishat Muhammad), for her effort to see that I succeeded. May you all live long to eat out of the fruit of your labour.

My appreciation will not be complete without thanking the Head of Department of Electrical and Computer Engineering in person of Dr. Yunus Adediran and the entire lecturers of Electrical and Computer Engineering. They are wonderful set of people.

Special thanks also go to my big brother and his wife, Mr. and Mrs. Kasim Idris for their immense support contributions towards the success of this work.

Also my appreciation goes to my brothers and sisters for their moral and financial support. In the list are:- Zubairu Mohammed Alhaji, Abubakar Kasim, Jibrin Mohammed, Ahmed Kasim, Zubairu Kasim, Kasim Mohammed, Abdulkadir Sha'aba Mohammed, Sadiq Mohammed, Asmau Mohammed, Hadiza Mohammed and little Zaynab Mohammed. May Almighty Allah sustain you all.

My appreciation goes to Mr. Emmanuel Agbo of Power Holding Company of Nigeria (PHCN) for his advice, support and attention. My appreciation will not be complete without thanking my dearest and caring one, Maryam Isah for her advice and prayers. Also, my appreciation goes to Zulai Abdulmalik for her prayers.

I cannot forget my colleagues that worked with me inspite of our various "differences" to ensure that this work was a reality. In the list are; Moses O. Ibrahim, Wilson Uchola, Samson Anuwe, Abdullah Alfa, Idris Bakare, Abdulquadri Zakariya, Kelani Sheriff, Bashirat Bolaji and others too numerous to mention. Thank you all and God bless (Amin).

vi

### **DEDICATION**

This work is dedicated to Allah subhanahu wata'ala (The Allah), my parents Mallam and Mallama Muhammad Zubairu and to the memory of my late uncle, Alhaji Kasim Zubairu.

### ABSTRACT

This project work provides an electronic security system to operate when you break a certain circuit i.e. it is design for four doors in such a way that when the first door is crossed, it locks out the remaining entries and the corresponding decimal number of door is displayed on the seven segment and an alarm is activated to draw the attention of the security man.

### LIST OF TABLE

Table 2.1 truth table of a 2-to-4 decoder Table 2.2 truth table of 3-to-8 binary decoder Table 2.3 truth table of an octal-to-binary encoder Table 2.4 truth table of a 10-to-4 decimal to binary encoder Table 3.1 truth table of dual 2-bit transparent latch Table 3.2 truth table of the 10-line-to-4-line priority encoder LIST OF FIGURES Fig 2.1 block diagram of a decoder Fig 2.2 representation of binary n-to 2<sup>n</sup> decoder Fig 2.3 symbol of a 2-to-4 binary decoder Fig 2.4 symbol of a 3-to-8 decoder Fig 2.5 symbol of a 2<sup>n</sup>-to-n binary encoder Fig 2.6 circuit diagram of an 8-to-3 encoder. Fig 3.1 block diagram of power supply stage Fig 3.2 a transformer circuit symbol Fig 3.3 circuit of a bridge rectifier

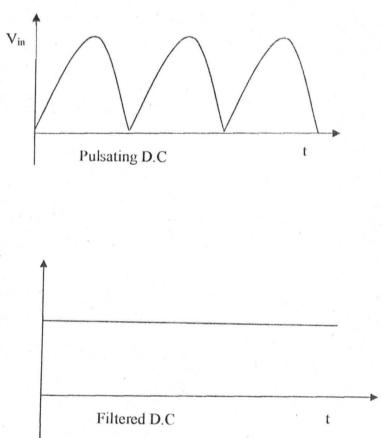

Fig 3.4 diagram of a filter circuit

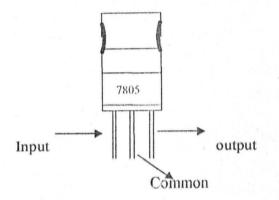

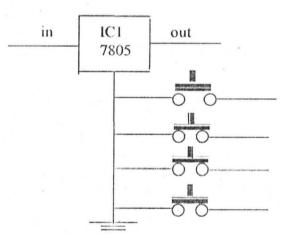

Fig 3.5 pin configuration of a 7805 voltage regulator

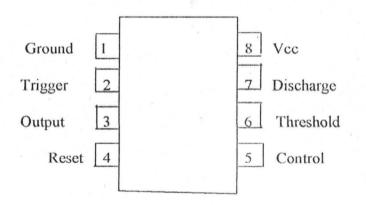

Fig 3.6 pin configuration of a 555 timer IC

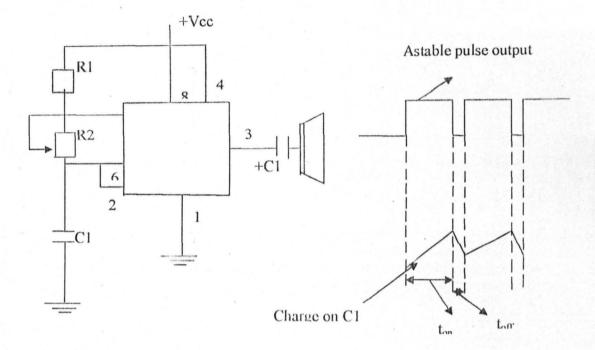

Fig 3.7 IC 555 timer in astable mode

Fig 3.8 push-to-on switches as input channels

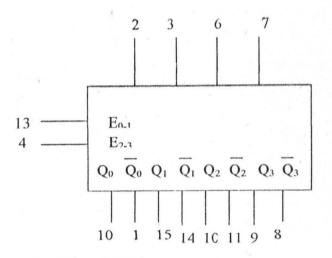

Fig 3.9 pin configuration of 7475

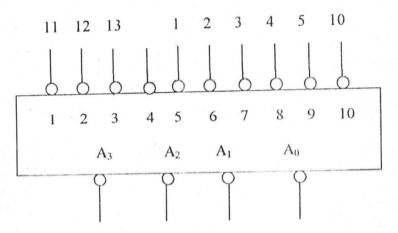

Fig 3.10 pin configuration of a priority encoder (74LS147)

Fig 3.11 pin configuration of logic inverter

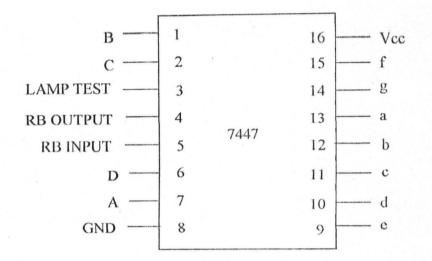

Fig 3.12 pin configuration of 7447 IC

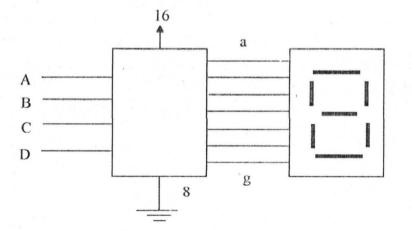

Fig 3.13 circuit representation of 7447 IC

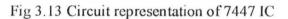

Fig 3.14 pin configuration of a dual-4-input NAND gate IC (7420)

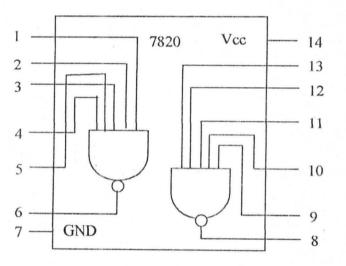

Fig 3.15 circuit operation of the reset switch.

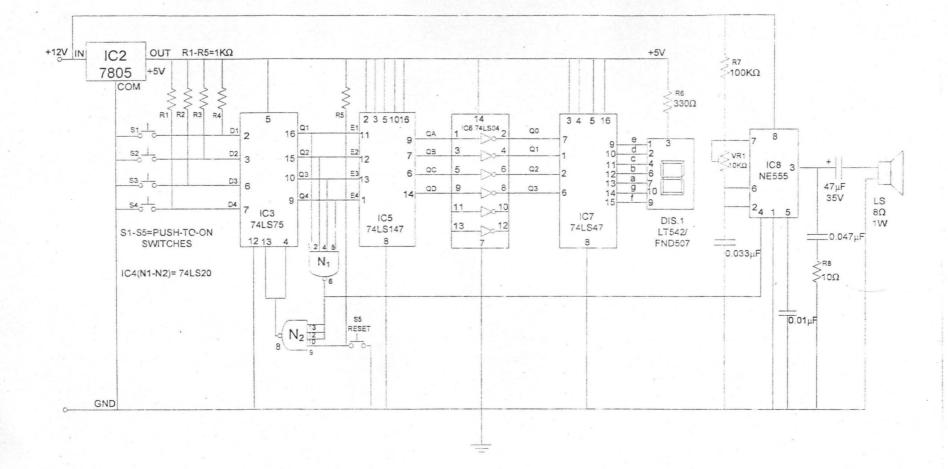

Fig 3.16 complete circuit diagram of a zone security system.

# TABLE OF CONTENTS

| CONTENT                                    | PAGE |

|--------------------------------------------|------|

| Cover page                                 | i    |

| Declaration                                | ii   |

| Certification                              | iii  |

| Dedication                                 | iv   |

| Acknowledgement                            | v    |

| Abstract                                   | vi   |

| List of tables                             | vii  |

| List of figures                            | vii  |

| CHAPTER ONE                                |      |

| 1.1 introduction                           | 1    |

| 1.2 aims and objectives                    | 2    |

| 1.3 methodology                            | 2    |

| 1.4 block diagram                          | 3    |

| 1.5 project layout                         | 4    |

| CHAPTER TWO                                |      |

| 2.1 literature review                      | 5    |

| 2.1.1 Space intrusion detector             | 6    |

| 2.1.2 Perimeter intrusion                  | 6    |

| 2.2 The review of some components required | 8    |

| 2.2.1 Decoder                              | 8    |

| 2.2.1.1 Binary n-to-2 <sup>n</sup> decoder | 9    |

| 2.2.2 Encoder                                  | 11 |

|------------------------------------------------|----|

| 2.2.2.1 octal-to-binary encoder                | 12 |

| 2.2.2.2 Decimal to binary encoder              | 13 |

| 2.2.2.3 Priority encoder                       | 14 |

| 2.2.3 Capacitors                               | 14 |

| 2.2.3.1 Charging of a capacitor                | 15 |

| 2.2.4 Diodes                                   | 16 |

| 2.2.4.1 Light Emitting Diode (LED)             | 17 |

| 2.2.4.2 Energy of Light Emitting Diode         | 18 |

| 2.2.4.3 Finding energy of Light Emitting Diode | 18 |

| CHAPTER THREE                                  |    |

| 3.1 design analysis                            | 19 |

| 3.2 power supply unit                          | 19 |

| 3.2.1 Transformer stage                        | 19 |

| 3.2.2 Rectification stage                      | 20 |

| 3.2.3 Filtration stage                         | 21 |

| 3.2.4 Regulation stage                         | 21 |

| 3.3 transducer stage                           | 22 |

| 3.4 The switching stage                        | 24 |

| 3.5 The latch stage                            | 25 |

| 3.6 The encoder stage                          | 26 |

| 3.7 The logic inverter stage                   | 28 |

| 3.8 The decoder stage                          | 29 |

# 3.9 The reset stage

| CHAPTER FOUR                                      |    |

|---------------------------------------------------|----|

| 4.1 constructions and testing                     | 32 |

| 4.2 materials used in the design and construction | 32 |

| 4.3 precautions taken                             | 33 |

|                                                   | 33 |

| 4.4 maintenance                                   |    |

| CHAPTER FIVE                                      | 34 |

| 5.1 Recommendations                               |    |

| 5.2 Conclusion.                                   | 34 |

30

### CHAPTER ONE

### **1.1 INTRODUCTION**

We are in information age. An age where information is ultimate, and our success or progress in life depends on how much of it we can accumulate for this information to be passed on and be interpreted without bias or prejudice; we need a clear and simple method to achieve that.

Safety and security are basic needs. They affect practically every area of our lives and are very important for companies to operate successfully in a globally networked economy by safeguarding against a wide range of threats [1].

A security system is a system that detects the presence of an intruder and gives an alarm. If the primary aim is to detect intruders, a bell horn, siren light is used to give the alarm, if the primary aim is to apprehend intruders; a signal is transmitted by wire to a nearby police station or security office [2]. In recent times, there has been a rapid increase in the incidence of breaking into offices and companies to rob citizens of their hard earned money and valuables. Thieves usually take advantage of the absence of security system in some offices and where there is an alarm, such alarm may not be able to provide adequate protection from the intruders. This is because thieves are generally familiar with the simple forms of alarm and have learnt ways of overcoming them. With this, it becomes necessary that more sophisticated security system with intruder alarm, such as the one described in this project are made. Due to the advantages of alarm system, I have chosen to design a unique feature of it called zone security system. The circuit can be used to guard many zones in an office from a place and make alarm sound.

1

In the project undertaken, the circuit is designed for four doors, if any of the four doors is opened, the opened door locks out the remaining entries and the corresponding number of door opened is displayed on the seven segment display and the alarm is triggered.

### **1.2 AIMS AND OBJECTIVES**

The aim of this project work is to design and construct an efficient electronic alarm system to be used in different zones in offices as a security device to detect and apprehend intruders.

The objectives are;

i) Fabricating an electronic alarm system for different zones in an office.

ii) Installing and testing of the security system.

### **1.3 METHODOLOGY**

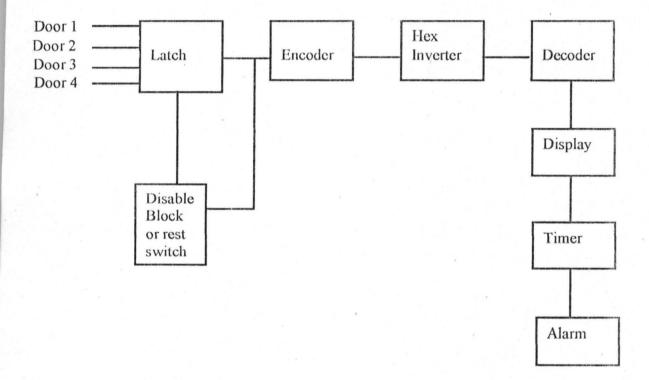

The circuit presented here determines as to which of the four doors was first crossed and locks out all the entries. Simultaneously, an audio alarm and the correct decimal number display of the corresponding door are activated. When an intruder gets inside a door, the corresponding output of latch IC3 (7475) changes its logic state from 1 to 0. The combinational circuitry comprising dual 4 input NAND gates of IC4 (7420) locks out all entries by producing appropriate latch-disable signal. Priority encoder IC5 (74147) encodes the active-low input condition into the corresponding binary coded decimal (BCD) number output. The outputs of IC5 after inversion by inverter gates inside hex inverter 74LS04 (IC6) are coupled to BCD to-7- segment decoder/display driver IC7 (7447). The output of IC7 drives common anode 7-segment LED display (Dis.1, FND507 or LT543). The audio alarm generator comprises clock oscillator IC8 (555), whose output

drives a loudspeaker. The oscillator frequency can be varied with the help of preset VR1.Logic 0 state at one of the outputs of IC3 produces logic 1 input condition at pin 4 of IC8, thereby enabling the audio oscillator.IC8 needs +12V regulated DC supply which is obtained using IC1 (7812) for sufficient alarm level. The remaining circuit operates on regulated +5V DC supply which is obtained using IC2 (7805).

### **1.4 BLOCK DIAGRAM**

Fig 1.1 the block diagram of the zone security system.

### **1.5 PROJECT LAYOUT**

CHAPTER ONE gives a brief introduction to security alarm system discussing the aims and objectives, the methodology along discussing the type produced in this project and also showing the block diagram. CHAPTER TWO discusses the literature review of security system from the early age, middle age and the present age it also discusses the type produced in this project and also reviews of some components required. CHAPTER THREE explains the design analysis in stages i.e. modules. CHAPTER FOUR is the construction and testing of the project. CHAPTER FIVE contains the recommendations and conclusion.

#### CHAPTER TWO

#### 2.1 LITERATURE REVIEW

When someone mentions security alarm it is not unreasonable to think of high technical devices developed in the silicon age. The truth is the concept of an alarm system is the one that was invented long before that. For thousand of years, man has used animals, more notable the dog to guard and alert him of anyone trying to tamper or steal his valuables. In the middle ages large gongs were used to warn a population of impending doom or large bonfires lit to warn off imminent invasion. [3]

As important as these developments were, it was not until 1852 that the first electro-mechanical alarm system was invented. Edwin Holmes was an American inventor from Boston Massachusetts; the alarm he devised was simplistic but effective. A solenoid struck a gong when a trip wire was disturbed. Although his alarm system is nothing compared to today's offering, it was positively received in its day. These early alarm systems continued to make use of simple electrical circuits and relays. A typical installation would see wire wound along windowsills and around door frames coupled with conductive lead foils and mechanical or magnetic switches laced with thin wire. [4]

The security conscious had to wait until the next century for further alarm system advances, which heralded the advent of the transistor and the integrated circuit. This technology allowed smaller units integrated with microwave and ultrasonic motion sensors along with features such as entrance and exit delays to be introduced. [5]

As far as the future of alarm system development goes, there is one thing you can be sure of and that's that it will continue to evolve the pressure to continue development is driven by the professional security system who continues the cat and mouse game of coming up with new ways to beat the latest alarm technology.[6]

The basic function of a security system is to detect as fast as possible an unauthorized entry into a defined area. Furthermore, the ideal security system should also be difficult to bypass or override, must be highly reliable and operate under adverse conditions e.g. should not be subject to false alarming. In security system there are two basic categories:

i) Space intrusion detectors

ii) Perimeter intrusion detector

**2.1.1 Space intrusion detector:** these are devices which can detect an intrusion in volumetric (three dimensional) space. In operation, a space intrusion detector generates an energy field in all direction this energy field is distributed, as by the entry of human being or other mass, a signal is initiated which triggers alarm. Obviously, a space intrusion detector is most difficult to JAM because one has to pass through the emission of an invisible infra-red ray. [7]

**2.1.2 Perimeter intrusion detectors:** in the field of industrial security system, the methodology of protection is quite different. First is to detect, second to delay and third to alarm. Perimeter intrusion detectors essentially consist of different types of switches which are strategically located around the perimeter of the protected premises. A classic example of the perimeter intrusion detector is the popular magnetic which can be mounted in any door or window. Such a device consist of two pieces of a magnet and a reed or slide switch which usually supply in the electrically closed position when the magnet is moved away from the switch as a result opens up triggering an alarm. Most

perimeter detectors work on this basic switch principle and are employed in wide variety of applications. Another type of perimeter switch is a mat or ribbon which is laid around or at the entrance point of the area protected. The mat is constructed in such a way that anyone stepping on it will close an electrical contact triggering an alarm. [8]

Another common form of perimeter detection is metallic window foil in which a conductive thin foil is glued to the glass. When the glass is broken, the foil opens up the circuit triggering the alarm. A more sophisticated type of perimeter detector consists of a light beam employing a light source and a photoelectric cell, whenever the beam is broken by someone passing through it, an alarm circuit is fired. Still another type of perimeter detector is a vibration switch; this device has adjustable contact which closes when vibration is exerted on a wall or panel. Vibration perimeter switches are very useful in protecting roofs or walls where the intruder might employ a saw or a hammer to gain entry. Note that, these perimeter detectors, though having various forms, have one thing in common in that they produce the circumference of an area i.e. they do not offer protection in three dimensional (volumetric) space. Furthermore, as most intruders know, a perimeter type of detector can easily be "jumped". Such jumping is accomplished merely by paralleling the electrical connection prior to breaking it. That's by putting a jumper wire across a normally closed magnetic switch prior to entry (this might be done by sawing a hole through the door). The effectiveness of a magnetic switch can completely be defeated by electrically shunting it out. Normally electrically open perimeter detectors (i.e. circuit that are closed upon intrusion) are even more easily defeated by simply cutting the wires leading to them. [8]

All these result to a research in designing a circuit which is more effective, efficient and reliable that will protect our valuables in different zones in our offices and companies. It is designed for four doors, in which if an intruder crosses a door by pressing the push-to-on switches, it locks out the remaining entries. Simultaneously, an audio alarm and the correct decimal number display of the corresponding door are activated. Also in the project undertaken, there is reduction in false alarm.

#### 2.2 THE REVIEW OF SOME COMPONENTS REQUIRED

#### **2.2.1 DECODERS**

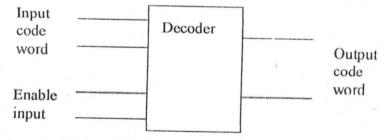

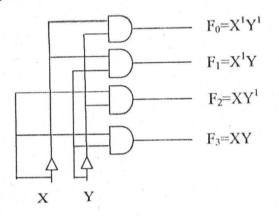

A decoder is a multiple-input, multiple output logic circuits that converts coded input into coded outputs, where the input and output codes are different. E.g. n-to-2n, BCD decoders.

Enable inputs must be on for the decoder to function, otherwise its output assumes a single 'disable' output code word. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding. [9] Figure below shows the block diagram of a decoder.

Fig 2.1

Block diagram of a decoder

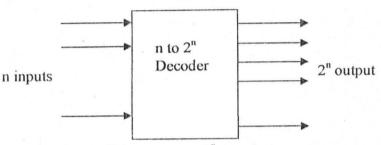

### 2.2.1.1 BINARY n- to-2n DECODER

A binary has n inputs and 2n outputs. Only the one output is active at any point of time, corresponding to the output value. The figure below shows the representation of binary n-to-2n decoder.

Fig 2.2 representation of binary n- to  $-2^n$  decoder.

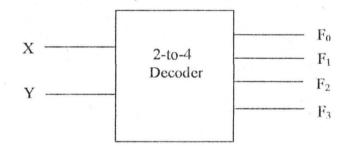

### Example 2-to-4 Binary decoder

A 2-4 decoder consists of two inputs and four outputs, the truth table is shown below. [9]

| 1 D |   | th. | ta | hi         | 63 |

|-----|---|-----|----|------------|----|

|     | u |     | ua | <b>N</b> 1 |    |

| х | Y   | $\mathbf{F}_{0}$ | Fı | F <sub>2</sub> | $F_3$ |

|---|-----|------------------|----|----------------|-------|

| 0 | 0   | 1                | Ō  | 0              | 0     |

| 0 | 1   | 0                | 1  | 0              | 0     |

| 1 | 0   | 0                | 0  | 1              | 0     |

| 1 | 1 . | 0                | 0  | . 0            | 1     |

Table 2.1 truth table of a 2-to-4 decoder

Fig 2.3 symbol of a 2-to-4 binary decoder

To minimize above truth table, we may use kernough map, but doing that we realize that it is a waste of time. One can directly write down the function of each of the outputs. The circuit diagram is as shown below. [9]

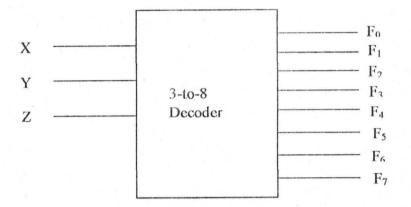

Another example of decoder is 3-to-8 Binary Decoder.

3-to-8 Binary Decoder; A 3 to 8 decoder consist of three inputs and eight outputs. The truth table is shown below.[9]

| Х | Y | Z | Fo | Fı | F <sub>2</sub> | F <sub>3</sub> | F4 | F <sub>5</sub> | F <sub>6</sub> | F7 |

|---|---|---|----|----|----------------|----------------|----|----------------|----------------|----|

| 0 | 0 | 0 | 1  | 0  | 0              | 0              | 0  | 0              | 0              | 0  |

| 0 | 0 | 1 | 0  | 1  | 0              | 0              | 0  | 0              | 0              | 0  |

| 0 | 1 | 0 | 0  | 0  | 1              | 0              | 0  | 0              | 0              | 0  |

| 0 | 1 | 1 | 0  | 0  | 0              | - 1            | 0  | 0              | 0              | 0  |

| 1 | 0 | 0 | 0  | 0  | 0              | 0              | 1  | 0              | 0              | 0  |

| 1 | 0 | 1 | 0  | 0  | 0              | 0              | 0  | 1              | 0              | 0  |

| 1 | 1 | 0 | 0  | 0  | 0              | 0              | 0  | 0              | 1              | 0  |

| 1 | 1 | 1 | 0  | 0  | 0              | 0              | 0  | 0              | 0              | 1  |

Table 2.2 Truth table of a 3-to-8 binary decoder

## Fig 2.4 Symbol of a 3-to-8 decoder

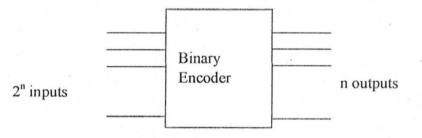

#### 2.2.2 ENCODER

An encoder is a combinational circuit that performs the inverse operation of a decoder. If the decoders' output code has fewer bits than the output code, the device is usually called an encoder. E.g.  $2^n$  to n binary encoder

The simplest encoder is a  $2^n$  to n binary encoder, where it has only one  $2^n$  inputs is the n-bit binary number corresponding to active input. [10]

Fig 2.5 Circuit symbol of a 2<sup>n</sup>-to-n binary encoder

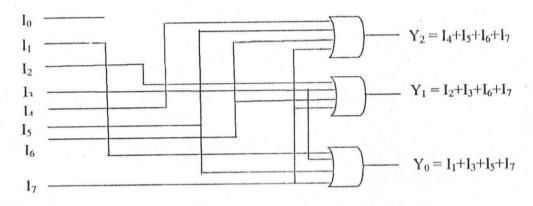

# 2.2.2.1 OCTAL-TO-BINARY ENCODER

Octal-to-binary take 8 inputs and provides 3 outputs, thus doing the opposite of a 3-to-8 decoder. At any time, only one input line has a value of 1. Below is the truth table of an octal-to-binary encoder. [10]

| Io | I | I <sub>2</sub> | I <sub>3</sub> | I4 | I <sub>5</sub> | I <sub>6</sub> | I <sub>7</sub> | Y <sub>2</sub> | Y1 | Y <sub>0</sub> |

|----|---|----------------|----------------|----|----------------|----------------|----------------|----------------|----|----------------|

| 1  | 0 | 0              | 0              | 0  | 0              | 0              | 0              | 0              | 0  | 0              |

| 0  | 1 | 0              | 0              | 0  | 0              | 0              | 0              | 0              | 0  | 1              |

| 0  | 0 | 1              | 0              | 0  | 0              | 0              | 0              | 0              | 1  | 0              |

| 0  | 0 | 0              | 1              | 0  | 0              | 0              | 0              | 0              | 1  | 1              |

| 0  | 0 | 0              | 0              | 1  | 0              | 0              | 0              | 1 .            | 0  | 0              |

| 0  | 0 | 0              | 0              | 0  | 1              | 0              | 0              | 1              | 0  | 1              |

| 0  | 0 | 0              | 0              | 0  | 0              | 1              | 0              | 1              | 1  | 0              |

| 0  | 0 | 0              | 0              | 0  | 0              | 0              | 1              | 1              | 1  | 1              |

Table 2.3 truth table of an octal-to-binary encoder

For an 8-to-3 binary encoder with inputs I1-I7 the logic expressions of outputs Y0-Y2 are;

- $Y_0 = I_1 + I_3 + I_5 + I_7$

- $Y_1 = I_2 + I_3 + I_6 + I_7$

$Y_2 = I_4 + I_5 + I_6 + I_7$

Based on the above equations, the circuit diagram can be drawn as shown below.[10]

Fig 2.6 Circuit diagram of an 8-to-3 binary encoder.

## 2.2.2.2 DECIMAL TO BINARY ENCODER

Decimal to binary encoder takes 10 inputs and provides 4 outputs, thus doing the opposite of 4-to-10 decoder. At any time, only one input line has a value 1.Below is the truth table.

| Io | Iı | I <sub>2</sub> | I <sub>3</sub> | I4 | 15 | I <sub>6</sub> | 17 | I <sub>8</sub> | 19 | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>2</sub> | Y <sub>0</sub> |

|----|----|----------------|----------------|----|----|----------------|----|----------------|----|----------------|----------------|----------------|----------------|

| 1  | 0  | 0              | 0              | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0              | 0              | 0              |

| 0  | 1  | 0              | 0              | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0              | 0              | 1              |

| 0  | 0  | 1              | 0              | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0              | 1              | 0              |

| 0  | 0  | 0              | 1              | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0              | 1              | 1              |

| 0  | 0  | 0              | 0              | 1  | 0  | 0              | 0  | 0              | 0  | 0              | 1              | 0              | 0              |

| 0  | 0  | 0              | 0              | 0  | 1  | 0              | 0  | 0              | 0  | 0              | 1              | 0              | 1              |

| 0  | 0  | 0              | 0              | 0  | 0  | 1              | 0  | 0              | 0  | 0              | 1              | 1              | 0              |

| 0  | 0  | 0              | 0              | 0  | 0  | 0              | I  | 0              | 0  | 0              | 1              | 1              | 1              |

| 0  | 0  | 0              | 0              | 0  | 0  | 0              | 0  | 1              | 0  | 1              | 0              | 0              | 0              |

| 0  | 0  | 0              | 0              | 0  | 0  | 0              | 0  | 0              | 1  | 1              | 0              | 0              | 1              |

Table 2.4 Truth table of a 10-4-decimal to binary encoder is shown above

From the above truth table, we can derive the functions  $Y_3$ ,  $Y_2$ ,  $Y_1$ , and  $Y_0$  as given below.

$Y_3 = I_8 + I_9$  $Y_2 = I_4 + I_5 + I_6 + I_7$

$Y_1 = l_2 + l_3 + l_6 + l_7$

$Y_0 = I_1 + I_3 + I_5 + I_7 + I_9$

### 2.2.2.3 PRIORITY ENCODER

If we look carefully at the encoder circuits that we got, we see some limitations. If more than two inputs are active simultaneously, the output is unpredictable.

This ambiguity is resolved if priority is established so that only one input is encoded no matter how many inputs are active at the giving point in time. Priority encoder is the one which include priority function. The operation of a priority encoder is such that if two or more inputs are active at the same time, the input having the highest priority will take the precedence. [10]

### 2.2.3 CAPACITORS

Capacitor is an electrical active device which consist of two conducting surface Separated by a layer of an isolating medium called dielectric. The conducting surface may be in the form of circular, cylindrical or spherical shape. The purpose of a capacitor is to store electrical energy by electrostatic stressing of the dielectric. The ability of the capacitor to store charge is called capacitance.

Mathematically,

$$C = \frac{Q}{V}$$

Hence, capacitance is the charge required per unit potential difference. By definition, the unit of capacitance is coulomb/volt which is also called Farad (I in honor Michael Faraday) [11]

## 2.2.3.1 CHARGING OF A CAPACITOR

In Fig 2.6a shown below, an arrangement by which a capacitor C may be charged through a high resistance R from a battery of V volt. The voltage across C can be measured by a suitable voltmeter. When switch S is connected to terminal (a), C is charged but when it is connected to b, C is short circuited through R and thus discharged. As shown in Fig 2.6b, switch is shifted to (a) for charging the capacitor for the battery. The voltage across C does not rise to V instantaneously but, builds up slowly i.e. exponentially and not linearly. Charging current  $I_C$  is maximum at the start i.e. when C is uncharged, then it decreases exponentially and finally ceases when p.d across capacitor plates become equal and opposite to the battery voltageV.

Let,  $V_C = p.d$  across C;  $I_C$  = charging current; q = charge on capacitor plates. The applied voltage V is equal to the sum of:

$$V = I_C R + V_C \tag{1}$$

Now,

$$I_c = \frac{dq}{dt} = \frac{d(CV_c)}{dt} = C \frac{dV_c}{dt}$$

(2)

Therefore,

$$V = V_c - CR \frac{dV_c}{dt}$$

(3)

$$-\frac{dV_C}{V-V_C} = -\frac{dt}{CR} \tag{4}$$

Integrating both sides, we get;

$$\int -\frac{dV_C}{V - V_C} = -\frac{1}{CR} \int dt$$

$$\log(V - V_C) = -\frac{t}{CR} + K$$

(5)

Where K is constant of integration. We know that at the start of charging when t=0, v=0.

(6)

Substituting these values we get

$$log V = K$$

Therefore,

$$log(V - V_c) = -\frac{t}{cR} + logV$$

Therefore,

$$\frac{v-v_c}{v} = e^{-\frac{t}{\lambda}}$$

Where  $CR = \lambda$  [11]

### **2.2.4 DIODES**

A P-N junction diode is a two- terminal device consisting of a P- N junction found either in Ge or Si crystal. Is a one- way device offering low resistance when forward biased and behaving almost as an insulator when reverse- biased. Hence, it is mostly used as rectifier i.e. in converting alternating current to direct current.

Diode is said to be forward bias if the positive terminal of the potential is connected to the P- region and the negative terminal of the potential to the N- region. The current voltage equation of P-N junction is represented mathematically thus;

$$I = I_0 \left( e^{\frac{\nu}{\eta kT} - 1} \right) Ampere$$

I = diode current (amp)

$I_0$  = diode reverse saturation current

V = voltage across junction

$K = \text{Boltzman constant} = 1.33 \times 10^{-23} \text{ J/}^{\circ}\text{K}$

T = crystal temperature in °K

$\eta = 1$  for germanium

$\eta = 2$  for silicon. [12]

Fig 2.2 circuit symbol of diode

#### 2.2.4.1 THE LIGHT – EMITTING DIODE (LED)

Nowadays, we can hardly avoid the brightly colored "electronic" numbers that glow at us from cash registers and gasoline pumps, microwave ovens and alarm clocks, we cannot seem to do without the invisible infrared beans that control elevator door and operate television sets via remote control. In nearly all cases this light is emitted from a p-n junction operating as a light – emitting diode (LED). LED's fabricated from different semiconductors cover a broad range of wavelengths, from infrared to ultraviolet. Each time an electron recombines with a positive charge; electric potential energy is converted into electromagnetic energy. [12]

For each combination of a negative and a positive charge a quantum of electromagnetic energy is emitted in the form of a photon of light with a frequency characteristic of a semiconductor material. Only photon in a very narrow frequency range can be emitted by any material. LED's that emit different colors are made of different semi- conductor materials, and required different energies to light them.

# 2.2.4.2 ENERGY OF LIGHT EMITTING DIODE

The electric energy is proportional to the voltage needed to cause electrons to flow across the p-n junction. The different colored LEDs emit predominantly light of a single colour. The energy (E) of the light emitted by an LED is related to the electric charge (q) of an electron and the voltage (v) requires to light the LED by the expression:

### E = qv (Joule)

This expression simply says that the voltage is proportional to the electric energy and is a general statement which applied to any circuit as well as to LEDs

#### 2.2.4.3 FINDING THE ENERGY OF LED FROM THE VOLTAGE

Suppose, we measure the voltage across the leads of an LED, and the corresponding energy required to light the LED. Assuming, the LED to be calculated is red, and voltage measured between the leads is 1.71volts. So, the energy required to light the LED is

E = qv Or  $E = 1.6 \times 10^{-19}$  (1.71) joule, since a coulomb is a joule.

Therefore,  $E = 2.74 \times 10^{-19}$  joule. [12]

## CHAPTER THREE

#### 3.1 Design analysis

Having considered the availability, effectiveness, comparative advantages, portability, cost and ease of discrete components mentioned in the literature review, it is reasonable that this component, which has the best generational characteristics, be used. The integrated circuits used are the 555 timers IC, Dual 4-input NAND gate, transparent latch, Priority encoder, Hex inverter, Decoder besides the seven segment display.

#### 3.2 Power supply unit

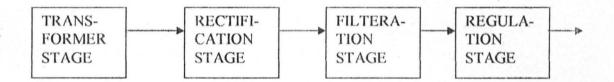

Most electronic circuit use direct current (d.c) supply for operation and the conversion of an a.c supply can be achieved through the power supply stage of the security system shown below.

Fig 3.1 Block diagram of power supply stage.

#### **3.2.1 TRANSFORMER STAGE**

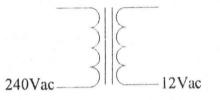

A  $240V_{rms}$  step-down transformer was used to reduce the 220Vac from PHCN (Power Holding Company of Nigeria) to 12Vac. This is fed to the rectifier to produce the required by the security system. The transformer circuit symbol is shown below.

Fig 3.2 transformer circuit symbol

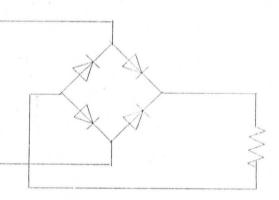

### **3.2.2 RECTIFICATION STAGE**

The term rectification is defined as the process of changing an alternating current (a.c) into a direct current (d.c) or process of changing pulsating a.c voltage to d.c voltage by eliminating the negative half cycle of the alternating voltage. A full wave bridge rectifier was used because of its ability to produce the approximate varying and reference voltage. The maximum instantaneous voltages between the terminals are:

$$V_{RMS} = \frac{V_{MAX}}{\sqrt{2}} \tag{1}$$

Fig 3.3 circuit of a Bridge Rectifier

### **3.2.3 FILTERATION STAGE**

The main function of the filter is to maximize the ripple content at the full wave bridge rectifier output. The capacitor used has a value of  $2200\mu F/25V$  for proper filtration. The input and output waveform of the filtering circuit is shown in the figure below:

Fig 3.4 Diagram of filter circuit

### **3.2.4 REGULATION STAGE**

In this stage, two voltage regulators were used i.e. LM 7812 and LM 7805. The 7812 gives a regulated 12V output which is supplied to the 555 timer to drive the speaker for sufficient audio alarm which was connected in astable mode. The 7805 gives a

regulated 5V output which is supplied to the control circuit. The control circuit requires 5V supply because of the use of the use of Transistor-Transistor-Logic (TTL) integrated circuit which requires a maximum of 5V supply.

Fig 3.5 Pin Configuration of a 7805 Voltage Regulator IC

### **3.3 TRANSDUCER STAGE**

The transducer used was a loud speaker. It has a resistance of  $8\Omega$  and a power rating of 1 watt. The speaker was used as the output of the astable circuit that is built around a 555 timer IC.

Fig 3.6 Pin Configuration of a 555 timer IC

The 555 in astable mode is shown below.

Fig 3.7 IC 555 in Astable mode.

Pin 4 is the next pin. This is active low meaning that if pin 4 is tied, the 555 is disabled or permanently reset. Pin 6 and Pin 2(The threshold and trigger input respectively) are tied together such that the timer is self triggered.  $R_1$  and  $R_2$  charges  $C_1$  while only  $R_2$  discharges it. The turn on of the pulse out is the charge time for  $C_1$  while the turn off is the discharge time.

$$t_{on} = 0.693(R_1 + R_2)C_1 \tag{1}$$

$$I_{off} = 0.693(R_2C_1) \tag{2}$$

For a complete pulse, the period T is given by

$$T = t_{on} + t_{off} \tag{3}$$

$$=0.693 (R_1 + R_2)C_1 + 0.693R_2C_1$$

$$= 0.693 (R_1 + 2R_2)C_1 [13]$$

(4)

The frequency of the astable circuit is

$$f = \frac{1}{T}$$

[14]

Therefore,

$$f = \frac{1}{0.693(R_1 + 2R_2)C_1}$$

$R_1 = 10 \mathrm{K} \Omega$

$$R_1 = 100 \text{K}\Omega;$$

$2R_2 = 2 \times 100 = 200 \text{K}\Omega$

Therefore

$$f = \frac{1.44}{(R_1 + 2R_2)C_1}$$

Frequency

$$f = \frac{1.44}{(10 \times 1000 + 2 \times 100 \times 1000) \times 0.033 \times 10^6}$$

= 207.8 Hz

### **3.4 THE SWITCHING STAGE**

The type of switches used here were the push-to –on switches, and one of their legs was each tied to the common leg of the regulator LM 7805, while other legs are connected to the inputs  $D_1$ ,  $D_2$   $D_3$  and  $D_4$  of the Dual 2-Bit transparent latch of IC<sub>2</sub> (7475). The diagram is shown below.

Fig 3.8 push-to-on switches as input channels.

# 3.5 THE LATCH STAGE

Here, the latch IC used is a Dual 2-Bit transparent latch (7475). The resulting output from any of the switches  $S_1$  to  $S_4$  is made available to the Dual 2-Bit transparent latch IC (7475).

Fig 3.9 Pin configuration of 7475

Vcc = Pin 5

GND = Pin 2

D<sub>0</sub>-D<sub>3</sub> are outputs

Q<sub>0</sub>-Q<sub>3</sub> are inputs

When an intruder presses a switch, the corresponding output of latch IC2 (7475) changes its logic state from 1 to 0. This means that the Dual 2-Bit transparent latch is active low. The output then enters into the dual 4-input NAND gates of IC3 (7420) and the priority encoder IC4 (74LS147).

|  | • |  |  |  |  |

|--|---|--|--|--|--|

|  |   |  |  |  |  |

|  |   |  |  |  |  |

Table 3.1 the truth table for Dual 2-Bit transparent latch operation is shown below.

-

|                | Input |   | Output |   |

|----------------|-------|---|--------|---|

| Operating mode | E     | D | Q      | Q |

| Data           | Н     | L | L      | Н |

| Enabled        | Н     | Н | H      | L |

| Data           | L     | X | q      | q |

Q= the state of reference output set up time prior to the high to low enable transition.

### 3.6 THE ENCODER STAGE

The resulting output from the transparent latch is made available to the priority encoder (74LS147).

The q input encoder accepts data from active low inputs  $(I_1-I_9)$  and provides a binary representation on the four active low inputs  $(A_0-A_3)$ . A priority is assigned to each input so that when two or more inputs are simultaneously active, the input with the highest priority is represented on the line T<sub>9</sub> having the highest priority.

The device provides the 10-line-to 4-line priority encoding function by use of implied decimal zero. The zero is encoded when all the nine data inputs are high, forcing all four outputs high.

Fig 3.10 Pin configuration of a priority encoder IC (74LS147)

Table 3.2 Truth table for the 10-line-to 4-line priority encoder.

| T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | T <sub>4</sub> | T <sub>5</sub> | T <sub>6</sub> | T <sub>7</sub> | T <sub>8</sub> | T9 | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----------------|----------------|----------------|----------------|

| Н              | H              | H              | H              | H              | H              | H              | H              | Н  | H              | Н              | H              | H              |

| X              | X              | X              | X              | X              | x              | X              | X              | L  | L              | Н              | H              | L              |

| X              | X              | X              | X              | X              | X              | X              | L              | H  | L              | H              | H              | H              |

| X              | X              | X              | X              | X              | X              | L              | Н              | H  | H              | L              | L              | L              |

| X              | X              | x              | X              | x              | L              | H              | H              | H  | H              | L              | L              | H              |

| X              | X              | X              | X              | L              | H              | H              | Н              | H  | H              | L              | H              | L              |

| X              | X              | X              | L              | Н              | Н              | Н              | H              | H  | Н              | L              | Н              | Н              |

| X              | X              | L              | Н              | Н              | Н              | H              | Н              | H  | H              | H              | L              | L              |

| X              | L              | Н              | Н              | Н              | Н              | Н              | Н              | Н  | H              | H              | L              | H              |

| L              | н              | Н              | н              | H              | H              | н              | II             | Н  | Н              | Н              | Н              | L              |

H = High or 1

L=Low or 0

X=Lower priority

### **3.7 THE LOGIC INVERTER STAGE**

Since the priority encoder used is active low, there is a need for its output to be inverted so that when it enters into the common anode 7- segment decoder, it will decode it properly.

The hex inverter used has NOT gates inside it. The IC number is 74LS04 (IC5).

|            |                | 74LS04                                                                                                                                                                         | ]  |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1          | A <sub>1</sub> |                                                                                                                                                                                | 2  |

| 3          | A <sub>2</sub> | $-\bigcirc \bigcirc $ | 4  |

| 5          | A <sub>3</sub> | $ \bigcirc \bigcirc$  | 6  |

| 9          | A <sub>4</sub> | — D Q4                                                                                                                                                                         | 8  |

| <b>Î</b> 1 | A <sub>5</sub> | ————— Q5                                                                                                                                                                       | 10 |

| 13         | A <sub>6</sub> |                                                                                                                                                                                | 12 |

| 7          | GNI            | O Vcc                                                                                                                                                                          | 14 |

|            |                |                                                                                                                                                                                | 1  |

Fig 3.11 Pin configuration of a logic inverter IC (74LS04).

A1-A6 are the 6 inputs

Q1-Q6 are the 6 outputs

Pin 14 is the power supply pin

The output from the priority encoder is made available to the input of the inverter IC. The outputs of the inverter IC, after inversion by the NOT gates inside are coupled to the input of the BCD- to-7-segment decoder driver of IC6 (74LS47) which converts it to decimal.

# 3.8 THE DECODER STAGE

In this stage, the 7447-BCD to 7 segment Decoder/Drive.

Fig 3.12 Pin configuration of 7447 IC

Its circuit representation is shown below.

This converts the binary number from the inverter to decimal and drives the seven segment display. The seven segments is a common anode display. This implies that the internal codes are tied together with a common point tap out to the Vcc.

# **3.9 THE RESET STAGE**

Here, the reset switch  $(s_5)$  and a 4-input NAND IC (7420) gate was used to achieve this (i.e. to force the digital display to 0).

Fig 3.14 the pin configuration of a Dual-4-input NAND gate IC (7420)

Fig 3.15 below is the circuit operation of the reset switch.

The output of  $N_2$  is connected to the pin 13 and 4 of the transparent latch so that when the reset switch is pressed, it encodes a logic 1 to all its four outputs and the priority encoder (IC 74LS147) encodes the BCD as 0 so that 0 will be displayed at the display seven segment.

### **CHAPTER FOUR**

#### 4.1 CONSTRUCTION AND TESTING

In this chapter, we are mostly concerned with the construction and testing of the device. After designing the various modules illustrated in the previous chapter, they were assembled on a project board (bread board). After the assembling, the various modules were tested using a DC 12V from the lead-acid accumulator.

Discovery 1

The various passive modules functioned well separately, but when assembled together in one piece, the expected output was not obtained.

Reason;

The pin configuration of the IC used was not strictly adhered to.

**Discovery 2**

The alarm level of the oscillator part was low when a voltage of 5V was used to power it. But when a 9V was used the alarm level increased.

Reason;

Voltage is proportional to the intensity of sound.

# 4.2 MATERIALS USED IN THE DESIGN AND CONSTRUCTION

The materials used to achieve the zone security system are;

(1) Bread board (project board)

(2) Soldering iron

(3) Conducting wire

(4) Vero board

(5) The case

(6) Saw

(7) Switches

(8) Gum

4.3 PRECAUTION TAKEN

(1) During the purchase of the component especially the IC, they were tested for workability before usage.

(2) The components were fixed on a bread board being soldered on a Vero board.

(3) A 40W soldering iron was used to avoid excess heat which may damage the sensitive component.

(4) Rigid soldering was also ensured and the wires checked properly for continuity.

### **4.5 MAINTENANCE**

This device has been designed in such a way to allow room for maintenance. Therefore, it is advised that when it develops fault, the casing can be opened and all possible damaged parts removed and replaced. However, care must be taken not to drop the device into water or allow contact with any corrosive liquid. Do not power the system with a voltage higher than 12Vdc. It should be stored in a cool dry place.

### **CHAPTER FIVE**

### **5.1 RECOMMENDATIONS**

The prototype of this device was made using 74147 (priority encoder). But it could be scarce. Therefore a high frequency diode can also be used in place of that. On slight modification, the design can be used for more than four doors when more than four input latch IC is used.

# **5.2 CONCLUSION**

As far as the future of alarm system development goes, there is one thing you can be sure of and that's that it will continue to evolve the pressure to continue development that is driven by the professional security system who continues the cat and mouse game of coming up with new ways to beat the latest alarm technology.

### REFERENCES

- [1] http://www.electronicsforu.com/project viewer-zone security system\_files

- [2] The encyclopedia AMERICANA international Edition Volume 4 first published in 1829

- [3] http://ezinearticles.com/?A-short-history-of-burglar alarm & id=475162

- [4] "http://en.wikipedia.org/wiki/burglar alarm"

- [5] www.alarmsystemreviews.com

- [6] www.wikipedia.org/wiki/burglar\_alarm

- [7] AGHA 1997

- [8] www.adt.co.uk/burglar-alarm-installers-and-intruder-detection.html

- [9] Samuel C. Lee [1978] "Digital circuit and logic design "page 107, 189"

- [10] Christopher E. Strangio [1980] "digital electronics fundamental concept and application" page 13, 65, 230

- [11] B.L Theraja and A.K Theraja, A text book of Electrical Technology

- [12] B.L Theraja and A.K Theraja, A text book of Electrical Technology

- · [13] Jacob Willman, microelectronics

- [14] P.N Okeke, a New Secondary Physics.

- [15] www.datasheetarchive.com

COMPLETE CIRCUIT DIAGRAM OF THE ZONE SECURITY SYSTEM

the states