#### FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA, NIGERIA

#### CENTRE FOR OPEN DISTANCE AND e-LEARNING (CODeL)

#### INTRODUCTION TO DIGITAL DESIGN AND MICROPROCESSOR

(CPT 322)

#### COURSE DEVELOPMENT TEAM

#### **CPT 322**

#### INTRODUCTION TO DIGITAL DESIGN AND MICROPROCESSOR

#### **Course Developer/Writers**

Dr. S. A. ADEPOJU Department of Computer Science Federal University of Technology, Minna, Nigeria.

#### **Programme Coordinator**

Mrs O. A. Abisoye Computer Science Department Federal University of Technology, Minna, Nigeria.

#### **Instructional Designers**

Prof. Gambari, Amosa Isiaka Mr. Falode, Oluwole Caleb Centre for Open Distance and e-Learning, Federal University of Technology, Minna, Nigeria.

#### **Editor**

Chinenye Priscilla Uzochukwu Centre for Open Distance and e-Learning, Federal University of Technology, Minna, Nigeria.

#### Director

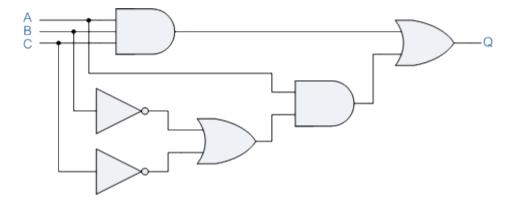

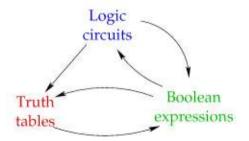

Prof. J. O. Odigure Centre for Open Distance and e-Learning, Federal University of Technology, Minna, Nigeria **CPT 322 Introduction to Digital Design and Microprocessor** is a 3 credit unit course for students studying towards acquiring a Bachelor of Science in Computer Science and other related disciplines. The course is divided into 4 modules and 13 study units. It will first introduce the history of digital computers. Then number system with emphasis on binary numbers will be discussed. Thereafter, logic circuit, Boolean algebra, K-map, combinational circuit and sequential circuits will be discussed.

The course guide therefore gives you an overview of what the course; CPT 322 is all about, the textbooks and other materials to be referenced, what you expect to know in each unit, and how to work through the course material.

#### What you will learn in this Course

The overall aim of this course, CPT 322 is to introduce you to basic concepts of digital electronic and microprocessor in order to enable you to understand the basic elements of logic circuits used in building microprocessor used in today's digital computer

#### Course Aim

This course aims to introduce students to the basics, concepts and design of digital circuits and microprocessor. It is believed the knowledge will enable the reader understand the basic logic circuits used to design the processors in use today and hence know how to build a smaller and faster ones with minimal cost and stress

#### **Course Objectives**

It is important to note that each unit has specific objectives. Students should study them carefully before proceeding to subsequent units. Therefore, it may be useful to refer to these objectives in the course of your study of the unit to assess your progress. Youshould always look at the unit objectives after completing a unit. In this way, you can besure that you have done what is required of you by the end of the unit.

However, below are overall objectives of this course. On completing this course, you should be able to:

now the history of digital computers.

Carry out binary arithmetic operations

Understand different codes used in computer

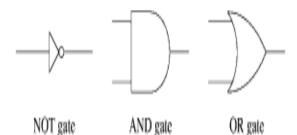

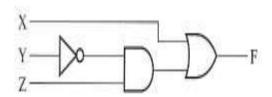

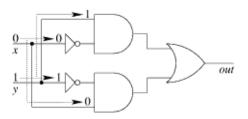

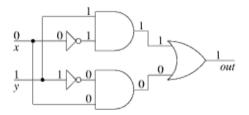

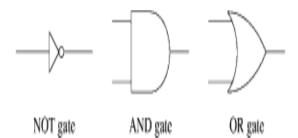

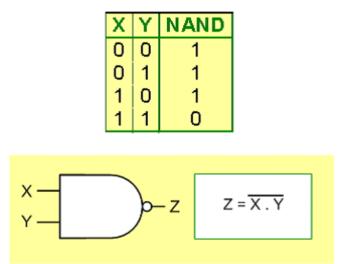

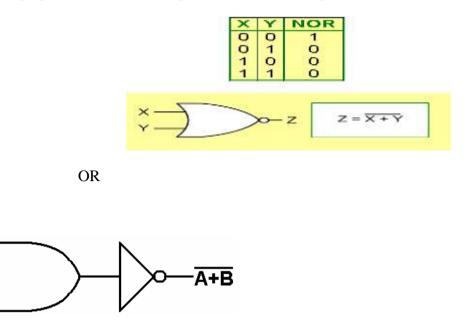

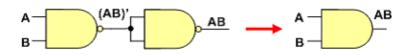

Describe logic circuits and gates, know their symbols and truth table

Simplify Boolean expressions

Know standard form and canonical expression

Know min term and max terms

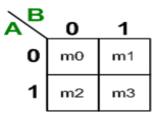

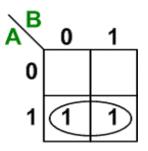

Draw Karnaugth (K) map Distinguish between combinational and sequential circuit. Discuss the various types of combinational circuits and sequential circuit and their operations

#### Working through this Course

To complete this course, you are required to study all the units, the recommended text books, and other relevant materials. Each unit contains some self assessment exercises and tutor marked assignments, and at some point in this course, you are required to submit the tutor marked assignments. There is also a final examination at the end of this course. Stated below are the components of this course and what you have to do.

#### **Course Materials**

The major components of the course are:

- 1. Course Guide

- 2. Study Units

- 3. Text Books

- 4. Assignment File

- 5. Presentation Schedule

#### **Study Units**

There are 13 study units and 4 modules in this course. They are:

Module 1: Introduction To Computer & Number System

UNIT 1 History of Digital Computer

UNIT 2 Number system

UNIT 3 Binary Codes and Arithmetic

Module 2: Logic Gates

UNIT 1 Basic Logic

UNIT 2 Boolean Algebra

#### UNIT 3 KarnaughMaps

UNIT 4 Standard forms, Min term and Max term

Module 3: Combinational Logic

UNIT 1 Adder and Subtractor

UNIT 2 Multiplexer and demultiplexer

UNIT 3 Decoder, Encoder and Comparator

Module 4: Sequential Logic

UNIT 1Latches and Flip flop

UNIT 2 multi vibrator

UNIT 3 Shift Register and counter

**Recommended Texts**

These texts and especially the internet resource links will be of enormous benefit to you in learning this course:

Ronald J. T.& Neal S., (2001).WidmerDigital Systems: Principle and Applications (8thEd.) Prentice Hall, Thomas L F., (2006). Digital Fundamentals, (9th Ed.). Prentice Hall. Morris M. & Charles R. K. (2004) Logic and Computer Design Fundamentals. (2004) NJPrentice Hall Wakerly J.F. (2000). Digital Design: Principles and Practices (3rd Ed.) Upper Saddle **River NJ: Prentice** http://www.computersciencelab.com/ComputerHistory/HistoryPt3.htm http://drstienecker.com/tech-332/3-logic-circuits-boolean-algebra-and-truth-tables/ http://www.courses.ebe.uct.ac.za/eee317w/1.%20Basic%20Logic%20Design.pdf http://www.circuitstoday.com/half-adder-and-full-adder http://www.electronics-tutorials.ws/combination/comb\_5.html http://www.circuitstoday.com/half-adder-and-full-adder http://www.ccse.kfupm.edu.sa/~amin/eCOE200/Lesson4 4.pdf http://www.indiabix.com/digital-electronics/combinational-logic-circuits /116006 http://www.allaboutcircuits.com https://maxwell.ict.griffith.edu.au/yg/teaching/.../dns\_module3\_p3.pd... http://www.ce.rit.edu/studentresources/reference.../341/.../EECC341-08.pdf http://www.techterms.com/definition/integratedcircuit

#### Assignment File

The assignment file will be given to you in due course. In this file, you will find all the details of the work you must submit to your tutor for marking. The marks you obtain for these assignments will count towards the final mark for the course. Altogether, there are tutor marked assignments for this course.

#### **Presentation Schedule**

The presentation schedule included in this course guide provides you with important dates for completion of each tutor marked assignment. You should therefore endeavour to meet the deadlines.

#### Assessment

There are two aspects to the assessment of this course. First, there are tutor marked assignments; and second, the written examination. Therefore, you are expected to take note of the facts, information and problem solving gathered during the course. The tutor marked assignments must be submitted to your tutor for formal assessment, in accordance to the deadline given. The work submitted will court for 40% of your total course mark.

At the end of the course, you will need to sit for a final written examination. This examination will account for 60% of your total score.

#### Tutor Marked Assignments (Tmas)

There are TMAs in this course. You need to submit all the TMAs. The best 10 will therefore be counted. When you have completed each assignment, send them to your tutor as soon as possible and make certain that it gets to your tutor on or before the stipulated deadline. If for any reason you cannot complete your assignment on time, contact your tutor before the assignment is due to discuss the possibility of extension. Extension will not be granted after the deadline, unless on extraordinary cases.

#### Final Examination and Grading

The final examination for CIT 322 will last for a period of 3 hours and have a value of 60% of the total course grade. The examination will consist of questions which reflect the self assessment exercise and tutor marked assignments that you have previously encountered. Furthermore, all areas of the course will be examined. It would be better to use the time between finishing the last unit and sitting for the examination, to revise the entire course. You might find it useful to review your TMAs and comment on them before the examination. The final examination covers information from all parts of the course.

The following are practical strategies for working through this course

1. Read the course guide thoroughly

2. Organize a study schedule. Refer to the course overview for more details. Note the time you are expected to spend on each unit and how the assignment relates to the units. Important details, e.g. details of your tutorials and the date of the first day of the semester are available. You need to gather together all these information in one place such as a diary, a wall chart calendar or an organizer. Whatever method you choose, you should decide on and write in your own dates for working on each unit.

3. Once you have created your own study schedule, do everything you can to stick to it. The major reason that students fail is that they get behind with their course works. If you get into difficulties with your schedule, please let your tutor know before it is too late for help.

4. Turn to Unit 1 and read the introduction and the objectives for the unit.

5. Assemble the study materials. Information about what you need for a unit is given in the table of content at the beginning of each unit. You will almost always need both the study unit you are working on and one of the materials recommended for further readings, on your desk at the same time.

6. Work through the unit, the content of the unit itself has been arranged to provide a sequence for you to follow. As you work through the unit, you will be encouraged to read from your set books

7. Keep in mind that you will learn a lot by doing all your assignments carefully. They have been designed to help you meet the objectives of the course and will help you pass the examination.

8. Review the objectives of each study unit to confirm that you have achieved them.

If you are not certain about any of the objectives, review the study material and consult your tutor.

9. When you are confident that you have achieved a unit's objectives, you can start on the next unit. Proceed unit by unit through the course and try to pace your study so that you can keep yourself on schedule.

10. When you have submitted an assignment to your tutor for marking, do not wait for its return before starting on the next unit. Keep to your schedule. When the assignment is returned, pay particular attention to your tutor's comments, both on the tutor marked assignment form and also written on the assignment. Consult you tutor as soon as possible if you have any questions or problems.

11. After completing the last unit, review the course and prepare yourself for the final examination. Check that you have achieved the unit objectives (listed at the beginning of each unit) and the course objectives (listed in this course guide).

#### **Tutors and Tutorials**

There are 8 hours of tutorial provided in support of this course. You will be notified of the dates, time and location together with the name and phone number of your tutor as soon as

you are allocated a tutorial group. Your tutor will mark and comment on your assignments, keep a close watch on your progress and on any difficulties you might encounter and provide assistance to you during the course. You must mail your tutor marked assignment to your tutor well before the due date. At least two working days are required for this purpose. They will be marked by your tutor and returned to you as soon as possible.

Do not hesitate to contact your tutor by telephone, e-mail or discussion board if you need help. The following might be circumstances in which you would find help necessary: contact your tutor if:

You do not understand any part of the study units or the assigned readings.

You have difficulty with the self test or exercise.

You have questions or problems with an assignment, with your tutor's comments on an assignment or with the grading of an assignment.

You should endeavour to attend the tutorials. This is the only opportunity to have face to face contact with your tutor and ask questions which are answered instantly. You can raise any problem encountered in the course of your study. To gain the maximum benefit from the course tutorials, have some questions handy before attending them. You will learn a lot from participating actively in discussions.

GOODLUCK!

# Module 1

### Introduction

UNIT 1: History of Digital Computer

UNIT 2 : Number system

UNIT 3 : Binary Codes and Arithmetic

## Unit 1

## History of Digital Computer

#### Content

| 1.0 | Introduction |

|-----|--------------|

|     |              |

- 2.0 Learning Outcomes

- 3.0 learning Contents

- 3.1 Steps toward Modern Computing

- 3.2 The Technological Edge, Electronic

- 3.3 The Eniac

- 3.4 The Stored Program Concept

- 3.5 The Computer Generations

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Readings

#### **1.0** Introduction

Digital Computer has undergone many developmental stages before we have what is available today. The word 'computer' is an old word that has changed its meaning several times in the last few centuries. Originating from the Latin, by the mid-17th century it meant 'someone who computes'. The American Heritage Dictionary gives its first computer definition as "a person who computes." The computer remained associated with human activity until about the middle of the 20th century when it became applied to "a programmable electronic device that can store, retrieve, and process data" as Webster's Dictionary defines it. Today, the word computer refers to computing devices, whether or not they are electronic, programmable, or capable of 'storing and retrieving' data.

This unit examines the chain of events that led to today's digital computers. We'll begin by looking at the computing equivalent of ancient history, including the first mechanical calculators and their huge, electromechanical offshoots that were created at the beginning of World War II. Next, you'll examine the technology—electronics—that made today's computers possible, beginning with what is generally regarded to be the first successful electronic computer, the ENIAC of the late 1940s. We'll then examine the subsequent history of electronic digital computers, divided into different "generations" of distinctive—and improving—technology.

#### 2.0 Learning Outcomes

At the end of this unit, you should be able to:

Define the term "electronics" and describe some early electronic devices that helped launch the computer industry.

Discuss the role that the stored-program concept played in launching the commercial computer industry.

List the generations of computer technology.

Identify the key innovations that characterize each generation.

#### 3.1 Steps Toward Modern Computing

Today's electronic computers are recent inventions, stemming from work that began during World War II. Yet the most basic idea of computing—the notion of representing data in a physical object of some kind, and getting a result by manipulating the object in some way—is very old. In fact, it may be as old as humanity itself. Throughout the ancient world, people used devices such as notched bones, knotted twine, and the abacus to represent data and perform various sorts of calculations..

First Steps: CalculatorDuring the sixteenth and seventeenth centuries, European mathematicians developed a series of calculators that used clockwork mechanisms and cranks . As the ancestors of today's electromechanical adding machines, these devices weren't computers in the modern sense. A **calculator** is a machine that can perform arithmetic functions with numbers, including addition, subtraction, multiplication, and division.

Figure1 :Pascal's calculator (1642)

French mathematician and philosopher Blaise Pascal, the son of an accountant, invents an adding machine to relieve the tedium of adding up long columns of tax figures.

Figure 2:Leibniz's calculator (1674)

German philosopher Gottfried Leibniz invents the first mechanical calculator capable of multiplication.

Figure 3: Babbage's difference engine (1822)

English mathematician and scientist Charles Babbage designs a complex, clockwork calculator capable of solving equations and printing the results. Despite repeated attempts, Babbage was never able to get the device to work.

#### Self Assessment Questions

Identify the early types of Electronic calculators

#### Self Assessment Answers

Pascal Calculator

Babbage's difference Engine

Leibniz's calculator

#### 3.2 The Technological Edge: Electronics

Today's computers are **automatic**, in that they can perform most tasks without the need for human intervention. They require a type of technology that was unimaginable in the nineteenth century. Nineteenth century inventor Charles Babbage came up with the first design for a recognizably-modern computer. It would have used a clockwork mechanism, but the technology of his day could not create the various gears needed with the precision that would have been required to get the device to work.

The technology that enables today's computer industry is called electronics. In brief, electronics is concerned with the behavior and effects of electrons as they pass through devices that can restrict their flow in various ways. The earliest electronic device, the vacuum tube, is a glass tube, emptied of air, in the flow of electrons that can be controlled in various ways. Created by Thomas Edison in the 1880s, vacuum tubes can be used for amplification, which is why they powered early radios and TVs, or switching, their role in computers. In fact, vacuum tubes powered all electronic devices (including stereo gear as well as computers) until the advent of solidstate devices. Also referred to as a semiconductor, a solid-state device acts like a vacuum tube, but it is a "sandwich" of differing materials that are combined to restrict or control the flow of electrical current in the desired way.

#### 3.3. The Electronic NumericalIntegrator AndComputer (ENIAC)

With the advent of vacuum tubes, the technology finally existed to create the first truly modern computer—and the demands of warfare created both the funding and the motivation. In World War II, the American military needed a faster method to calculate shell missile trajectories. The military asked Dr. John Mauchly (1907–1980) at the University of Pennsylvania to develop a machine for this purpose. Mauchly worked with a graduate

student, J. Presper Eckert (1919–1995), to build the device. Although commissioned by the military for use in the war, the ENIAC was not completed until 1946, after the war had ended .Although it was used mainly to solve challenging math problems, **ENIAC** was a true programmable digital computer rather than an electronic calculator.

One thousand times faster than any existing calculator, the ENIAC gripped the public's imagination after newspaper reports described it as an "Electronic Brain." The ENIAC took only 30 seconds to compute trajectories that would have required 40 hours of hand calculations.

ENIAC

#### 3.4 The Stored-Program Concept

ENIAC had its share of problems. It was frustrating to use because it wouldn't run for more than a few minutes without blowing a tube, which caused the system to stop working. Worse, every time a new problem had to be solved, the staff had to enter the new instructions the hard way: by rewiring the entire machine. The solution was the stored program concept, an idea that occurred to just about everyone working with electronic computers after World War II.

With the *stored-program concept*, the computer program, as well as data, is stored in the computer's memory. One key advantage of this technique is that the computer can easily go back to a previous instruction and repeat it. Most of the interesting tasks that today's computers perform stem from repeating certain actions over and over. But the most important advantage is convenience. You don't have to rewire the computer to get it to do something different. Without the stored-program concept, computers would have remained tied to specific jobs, such as cranking out ballistics tables. All computers that have been sold commercially have used the stored program concept.

#### Self Assessment Questions

What is full Meaning of the ENIAC

What is the fundamental electronic device employed on the ENIAC

ENIAC stands for Electronic Numerical Integrator And Computer

The fundamental Electronic device is the Vaccum Tube.

#### 3.5 The Computer Generations

The computer has evolved through many generations and it is being view differently by many authors. According to The Computational Science Education Project, US, the computer has evolved through the following stages from the mechanical era which have been described above:

#### First Generation Electronic Computers (1937-1953)

These devices used electronic switches, in the form of vacuum tubes, instead of electromechanical relays. The earliest attempt to build an electronic computer was by J. V. Atanasoff, a professor of physics and mathematics at Iowa State in 1937. Atanasoff set out to build a machine that would help his graduate students solve systems of partial differential equations. By 1941 he and graduate student Clifford Berry had succeeded in building a machine that could solve 29 simultaneous equations with 29 unknowns. However, the machine was not programmable, and was more of an electronic calculator.

A second early electronic machine was Colossus, designed by Alan Turing for the British military in 1943. The first general purpose programmable electronic computer was the Electronic Numerical Integrator and Computer (ENIAC), built by J. Presper Eckert and John V. Mauchly at the University of Pennsylvania. Research work began in 1943, funded by the Army Ordinance Department, which needed a way to compute ballistics during World War II. The machine was completed in 1945 and it was used extensively for calculations during the design of the hydrogen bomb. Eckert, Mauchly, and John von Neumann, a consultant to the ENIAC project, began work on a new machine before ENIAC was finished.

The main contribution of EDVAC, their new project, was the notion of a stored program. ENIAC was controlled by a set of external switches and dials; to change the program required physically altering the settings on these controls. EDVAC was able to run orders of magnitude faster than ENIAC and by storing instructions in the same medium as data, designers could concentrate on improving the internal structure of the machine without worrying about matching it to the speed of an external control. Eckert and Mauchly later designed what was arguably the first commercially successful computer, the UNIVAC; in 1952. Software technology during this period was very primitive.

#### Second Generation (1954-1962)

The second generation witnessed several important developments at all levels of computer system design, ranging from the technology used to build the basic circuits to the programming languages used to write scientific applications. Electronic switches in this era were based on discrete diode and transistor technology with a switching time of approximately 0.3 microseconds. The first machines to be built with this technology include TRADIC at Bell Laboratories in 1954 and TX-0 at MIT's Lincoln Laboratory. Index registers were designed for controlling loops and floating point units for calculations based on real numbers.

A number of high level programming languages were introduced and these include FORTRAN (1956), ALGOL (1958), and COBOL (1959). Important commercial machines of this era include the IBM 704 and its successors, the 709 and 7094. In the 1950s the first two supercomputers were designed specifically for numeric processing in scientific applications.

The transistor heralded the second generation of computers.

Early second-generation computers were frustrating to use because they could run onlyone job at a time. Users had to give their punched cards to computer operators, who would run their program and then give the results back to the user.

#### Self Assessment Questions

What were the punched cards used for on the Second Generation computers

The main electronic device on the second generation computer is the \_\_\_\_\_

#### Self assessment Answers

The Punched cards were used as storage devices

The main electronic device on the second generation computer is the Transistors

#### Third Generation (1963-1972)

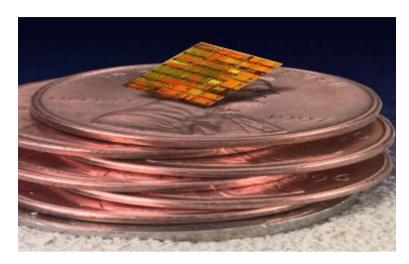

Technology changes in this generation include the use of integrated circuits, or ICs (semiconductor devices with several transistors built into one physical component), semiconductor memories, microprogramming as a technique for efficiently designing complex processors and the introduction of operating systems and time-sharing. The first ICs were based on small-scale integration (SSI) circuits, which had around 10 devices per circuit (or 'chip'), and evolved to the use of medium-scale integrated (MSI) circuits, which had up to 100 devices per chip. Multilayered printed circuits were developed and core memory was replaced by faster, solid state memories.

In 1964, Seymour Cray developed the CDC 6600, which was the first architecture to use functional parallelism. By using 10 separate functional units that could operate simultaneously and 32 independent memory banks, the CDC 6600 was able to attain a computation rate of one million floating point operations per second (Mflops). Five years later CDC released the 7600, also developed by Seymour Cray. The CDC 7600, with its pipelined functional units, is considered to be the first vector processor and was capable of executing at ten Mflops. The IBM 360/91, released during the same period, was roughly twice as fast as the CDC 660.

Early in this third generation, Cambridge University and the University of London cooperated in the development of CPL (Combined Programming Language, 1963). CPL was, according to its authors, an attempt to capture only the important features of the complicated and sophisticated ALGOL. However, like ALGOL, CPL was large with many features that were hard to learn. In an attempt at further simplification, Martin Richards of Cambridge developed a subset of CPL called BCPL (Basic Computer Programming Language, 1967). In 1970 Ken Thompson of Bell Labs developed yet another simplification of CPL called simply B, in connection with an early implementation of the UNIX operating system. comment):

Integrated chips are shown here with first-generation vacuum tubes and second generation transistors

An integrated circuit ("silicon chip") [photo courtesy of IBM]

#### Fourth Generation (1972-1984)

Large scale integration (LSI - 1000 devices per chip) and very large scale integration (VLSI - 100,000 devices per chip) were used in the construction of the fourth generation computers. Whole processors could now fit onto a single chip, and for simple systems the entire computer (processor, main memory, and I/O controllers) could fit on one chip. Gate delays dropped to about 1ns per gate. Core memories were replaced by semiconductor memories. Large main memories like CRAY 2 began to replace the older high speed vector processors, such as the CRAY 1, CRAY X-MP and CYBER

In 1972, Dennis Ritchie developed the C language from the design of the CPL and Thompson's B. Thompson and Ritchie then used C to write a version of UNIX for the DEC PDP-11. Other developments in software include very high level languages such as FP (functional programming) and Prolog (programming in logic).

IBM worked with Microsoft during the 1980s to start what we can really call PC (Personal Computer) life today. IBM PC was introduced in October 1981 and it worked with the operating system (software) called 'Microsoft Disk Operating System (MS DOS) 1.0. Development of MS DOS began in October 1980 when IBM began searching the market for an operating system for the then proposed IBM PC and major contributors were Bill Gates, Paul Allen and Tim Paterson. In 1983, the Microsoft Windows was announced and this has witnessed several improvements and revision over the last twenty years.

#### Self Assessment Questions

What electronic devices serve as backbone of the third and fourth generation computers.

The Large scale Integrated Circuit and the Microprocessors respectively are the backbone electronics for the third and fourth Generation computers

#### Fifth Generation (1984-1990)

This generation brought about the introduction of machines with hundreds of processors that could all be working on different parts of a single program. The scale of integration in semiconductors continued at a great pace and by 1990 it was possible to build chips with a million components - and semiconductor memories became standard on all computers. Computer networks and single-user workstations also became popular.

Parallel processing started in this generation. The Sequent Balance 8000 connected up to 20 processors to a single shared memory module though each processor had its own local cache. The machine was designed to compete with the DEC VAX-780 as a general purpose Unix system, with each processor working on a different user's job. However Sequent provided a library of subroutines that would allow programmers to write programs that would use more than one processor, and the machine was widely used to explore parallel algorithms and programming techniques.

#### \*Please Insert Relevant Images /Graphics

The Intel iPSC-1, also known as 'the hypercube' connected each processor to its own memory and used a network interface to connect processors. This distributed memory architecture meant memory was no longer a problem and large systems with more processors (as many as 128) could be built. Also introduced was a machine, known as a data-parallel or SIMD where there were several thousand very simple processors which work under the direction of a single control unit. Both wide area network (WAN) and local area network (LAN) technology developed rapidly.

#### Sixth Generation (1990 - )

Most of the developments in computer systems since 1990 have not been fundamental changes but have been gradual improvements over established systems. This generation brought about gains in parallel computing in both the hardware and in improved understanding of how to develop algorithms to exploit parallel architectures.

Workstation technology continued to improve, with processor designs now using a combination of RISC, pipelining, and parallel processing. Wide area networks, network bandwidth and speed of operation and networking capabilities have kept developing tremendously. Personal computers (PCs) now operate with Gigabit per second processors, multi-Gigabyte disks, hundreds of Mbytes of RAM, colour printers, high-resolution graphic monitors, stereo sound cards and graphical user interfaces.

Thousands of software (operating systems and application software) are existing today and Microsoft Inc. has been a major contributor. Microsoft is said to be one of the biggest companies ever, and its chairman – Bill Gates has been rated as the richest man for several years.

Finally, this generation has brought about micro controller technology. Micro controllers are 'embedded' inside some other devices (often consumer products) so that they can control the features or actions of the product. They work as small computers inside devices and now serve as essential components in most machines.

#### Self Assessment Questions

What is the common characteristic feature of the fifth and sixth generation computers

#### Self Assessment Answers

The common feature is the parallel computing capability

#### 4.0 Conclusion

This unit has given a broad view of chronological order on the genesis of modern day digital computers. You also read abou the various developmental stages which digital computers have gone through. This is to enable us trace the history of the modern day digital computers,

#### 5.0 Summary

You have learnt:

The technology that enables today's computer industry is called electronics. Electronics is concerned with the behavior and effects of electrons as they passthrough devices that can restrict their flow in various ways. The vacuum tube was the earliest electronic device.

The first successful large-scale electronic digital computer, the ENIAC, laid the foundation for the modern computer industry.

The stored-program concept fostered the computer industry's growth because it enabled customers to change the computer's function easily by running a different program.

First-generation computers used vacuum tubes and had to be programmed in difficultto-use machine languages.

Second-generation computers introduced transistors and high-level programming languages such as COBOL and FORTRAN.

Third-generation computers introduced integrated circuits, which cut costs and launched the minicomputer industry. Key innovations included timesharing, wide area networks, and local area networks.

Fourth-generation computers use microprocessors. Key innovations include personal computers, the graphical user interface, and the growth of massive computer networks.

An unparalleled public medium for communication and commerce, the Internet has created a massive public computer network of global proportions

As computers become more powerful and less expensive, the rise of global networking is making them more valuable. The combination of these two forces is driving major changes in every facet of our lives.

#### 6.0 Tutor Marked Assignment

1.Explain why ENIAC is considered the first true programmable digital computer. What kinds of problems did it have?

2. Explain the stored-program concept. How did this concept radically affect the design of computers we use today?

3. What major hardware technology characterized each of the four generations of computers?

4. What are the differences between a command line interface and a user interface? Which one is easier to use and why?

5. How does a machine language differ from a high-level programming language?

#### 7.0 References/Further Readings

Ronald J. T. & Neal S., (2001). Widmer Digital Systems: Principle and Applications (8th Ed.) Prentice Hall, Thomas L F., (2006). Digital Fundamentals (9th Ed.). Prentice Hall. Morris M. & Charles R. K. (2004) Logic and Computer Design Fundamentals. (2004) NJPrentice Hall Wakerly J.F. (2000). Digital Design: Principles and Practices (3rd Ed.) Upper Saddle River NJ; Prentice http://www.en.wikipedia.org/wiki/Computer http://www.computersciencelab.com/ComputerHistory/HistoryPt3.htm http://www.computersciencelab.com/ComputerHistory/HistoryPt3.htm http://www.ieeeghn.org/wiki/images/5/57/Onifade.pdf http://www.cs.ncl.ac.uk/publications/articles/papers/398.pdf

## Unit 2

### Number Systems

#### Content

- 1.0 Introduction

- 2.0 Learning Outcomes

- 3.0 Learning Contents

- 3.1 Weighted Number System

- 3.2 Important Number System

- 3.3 Octal System

- 3.4 Hexadecimal System

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

#### 1.0 Introduction

Before the inception of *digital* computers, the only number system that was in common use is the *decimal* number system which has a total of 10 digits (0 to 9). However, signals in *digital* computers may represent a digit in some number system. It was also found that the binary number system is more reliable to use compared to the more familiar decimal system. The binary number system and digital codes are fundamental to computers and to digital electronics in general.

In this unit, the binary number system and its relationship to other number systems such as decimal, hexadecimal, and octal is presented. Arithmetic operations with binary numbers are covered to provide a basis for understanding how computers and many other types of digital systems work. Also, digital codes such as binary coded decimal (BCD), the Gray code, and the ASCII will be covered in the next unit..

#### 2.0 Learning Outcomes

At the end of this unit, you should be able to:

Know what is meant by a weighted number system. Know the asic features of weighted number systems. Know and review commonly used number systems, e.g. decimal, binary, octal and hexadecimal. Convert from decimal to binary and from binary to decimal Convert between the binary and hexadecimal number systems Convert between the binary and octal number systems How to convert from one number system to another

#### 3.0 Learning Contents

#### 3.1 Weighted Number Systems:

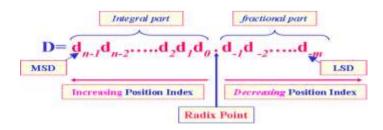

A number D consists of *n* digits with each digit has a particular *position*.D =  $d_{n-1} d_{n-2} d_{2} d_{2} d_{0}$

Every digit *position* is associated with a *fixed weight*. If the weight associated with the *i*th.position is *wi*, then the value of D is given by:

#### $D = d_{n-1} w_{n-1} + d_{n-2} w_{n-2} + \ldots + d_2 w_2 + d_1 + d_0 w_0$

Example of Weighted Number Systems:

• The Decimal number system is a weighted system.

• For Integer decimal numbers, the weight of the rightmost digit (*at position 0*) is 1, the weight of *position 1* digit is 10, that of *position 2* digit is 100, *position 3* is 1000, etc.

Thus,

$w_0 = 1$ ,  $w_1 = 10$ ,  $w_2 = 100$ ,  $w_3 = 1000$ , etc.

Example Show how the value of the decimal number 9375 is estimated

| Position | 3         | 2     | 1    | 0   |

|----------|-----------|-------|------|-----|

| Number   | 9         | 3     | 7    | 5   |

| Weight   | 1000      | 100   | 10   | 1   |

| Value    | 9x1000    | 3x100 | 7x10 | 5x1 |

| Value    | 9000 +300 | +70+5 |      |     |

The Radix (Base)

For *digit position i*, most weighted number systems use weights (w*i*) that are *powers* of some constant value called the radix (r) or the base such that w*i*= r*i*. A number system of radix r, typically has a set of r allowed digits  $\in \{0, 1, ..., (r-1)\}$ . The leftmost digit has the highest weight Most Significant Digit (MSD). The rightmost digit has the lowest weight Least Significant Digit (LSD)

Self assessment questions

What Is The Weight Value Of 7 In 9786

Self assessment Answers

The weight value of 7 in 9786 is 100

Example Decimal Number System

1. Radix (Base) = Ten

2. Since  $w_i = r^i$ , then  $w_0 = 10^0 = 1$ ,  $w_1 = 10^1 = 10$ ,  $w_2 = 10^2 = 100$ ,  $w_3 = 10^3 = 1000$ , etc.

3. Number of Allowed Digits is Ten = {0, 1, 2, 3, 4, 5, 6, 7, 8, 9}

Thus:

$9375 = 5x10^0 + 7x10^1 + 3x10^2 + 9x10^3$

= 5x1 + 7x10 + 3x100 + 9x1000

| Position | 3                | 2         | 1                | 0                |

|----------|------------------|-----------|------------------|------------------|

|          | 1000             | 100       | 10               | 1                |

| Weight   | =10 <sup>3</sup> | $=10^{2}$ | =10 <sup>1</sup> | =10 <sup>0</sup> |

|          |                  |           |                  |                  |

The Radix Point

Consider a number system of radix r, a number D of *n integral* digits and *m fractional* digits is represented as shown

Digits to the left of the radix point (*integral digits*) have positive position indices, while digits to the right of the radix point (*fractional digits*) have negative position indices.

Position *indices* of digits to the *left* of the *radix point* (*the integral part of D*) start with a 0 and are incremented as we move lefts  $(d_{n-1} d_{n2} \dots d_2 d_1 d_0)$ .

Position *indices* of digits to the *right* of the *radix point* (*the fractional part of D*) are *negative* starting with -1 and are decremented as we move rights ( $d_{-1}d_{-2}...,d_{-m}$ ).

The weight associated with digit position *i* is given by  $w_i = r_i$ , where *i* is the position index

$\forall i = -m, -m+1, ..., -2, -1, 0, 1, ..., n-1$

The Value of D is Computed as :

Example Show how the value of the following decimal number is estimated

D = 5 2. 9 4 6

| Number   | 5               | 2          | •   | 9     | 4      | 6        |

|----------|-----------------|------------|-----|-------|--------|----------|

| Position | 1               | 0          |     | -1    | -2     | -3       |

| Weight   | 10 <sup>1</sup> | 100        | •   | 10-1  | 10-2   | 10-3     |

|          | =               | =          |     | =     | =      | =        |

|          | 10              | 1          |     | 0.1   | 0.01   | 0.001    |

|          |                 |            |     |       |        |          |

| Value    | 5x10            | 2x1        |     | 9x0.1 | 4x0.01 | 6x0.001  |

| Value    | 50 +2+0.        | 9+0.04+0.0 | 006 | 1     | •      | <u>.</u> |

$D = 5x10^{1} + 2x10^{0} + 9x10^{-1} + 4x10^{-2} + 6x10^{-3}$

Notation

• Let  $(D)_r$  denotes a number D expressed in a number system of radix r.

Note: In this notation, r will be expressed in decimal

Example:

$(29)_{10}$  Represents a decimal value of 29. The radix "10" here means ten.

$(100)_{16}$  is a Hexadecimal number since r = "16" here means sixteen. This number is equivalent to a decimal value of 162.

$(100)_2$  is a Binary number (radix =2, i.e. two) which is equivalent to a decimal value of  $2^2 = 4$ .

Self assessment questions

Show how the decimal value of 100.01 is evaluated

Self assessment answers

$1x10^{2}+0x10^{1}+0x10^{0}+0x10^{-1}+1x10^{-2}$

#### 3.2 Important Number Systems

#### The Decimal System

In the decimal number system each of the ten digits, 0 through 9.represents a certain quantity. The ten symbols (digits) do not limit you to expressing only ten different quantities because you use the various digits in appropriate positions within a number to indicate the magnitude of the quantity. You can express quantities up through nine before running out of digits; if you wish to express a quantity greater than nine, you use two or more digits, and the position of each digit within the number tells you the magnitude it represents. So,

r = 10 (ten Radix is not a Power of 2)

Ten Possible Digits {0, 1, 2, 3, 4, 5, 6, 7, 8, 9}

#### The Binary System

The binary number system is another way to represent quantities. It is less complicated than the decimal system because it has only two digits. The decimal system with its ten digits is a base-ten system; the binary system with its two digits is a base-two system. The two binary digits (bits) are 1 and O. The position of a 1 or 0 in a binary number indicates its weight. or value within the number, just as the position of a decimal digit determines the value of that digit. The weights in a binary number are based on powers of two. So,

r = 2

Two Allowed Digits {0, 1}

#### A **B**inary Dig**IT** is referred to as Bit

The leftmost bit has the highest weight i.e. Most Significant Bit (MSB)

The rightmost bit has the lowest weight i.e. Least Significant Bit (LSB)

#### Conversion from Binary to decimal

The decimal value of any binary number can be found by adding the weights of all bits that are 1 and discarding the weights of all bits that are 0.

#### Examples

Find the decimal value of the two Binary numbers (101)2 and (1.101)2

$$(1 \ 0 \ 1)2 = 1x2^3 + 0x2^1 + 1x2^0$$

$$= 1x4 + 0x2 + 1x1$$

$$= (5)_{10}$$

$$(1. 1 0 1)^{2} = 1x^{2^{0}} + 1x^{2^{-1}} + 0x^{2^{-2}} + 1x^{2^{-3}}$$

$$= 1 + 0.5 + 0.25 + 0.125$$

$$= (1. 8 7 5)_{10}$$

Conversion from decimal to base 2 (Binary).

Example: Convert (53) 10 to base 2 (binary)(?)2

#### Soln

| Division Step | Quotient      | Remainder |

|---------------|---------------|-----------|

| 53 ÷ 2        | Q0 = 26       | 1 = a0    |

| $26 \div 2$   | Q1 =13        | 0 = a1    |

| $13 \div 2$   | Q2 = 6 1 = a2 |           |

|               |               |           |

$$6 \div 2$$

Q3 = 3 0 = a3s

$$3 \div 2$$

Q4 =1 1 = a4

$$1 \div 2$$

0  $1 = a5$

Thus (53)<sub>10</sub>=(110101)<sub>2</sub>

Or by using sum of weigth method

$$53 = 32 + 16 + 4 + 1 = 2^5 + 2^4 + 2^2 + 2^0 = 110101_2$$

To convert  $546_{10}$  to binary

| 546 ÷2  | Q0=273 | R=0 <b>↑</b> |

|---------|--------|--------------|

| 273 ÷ 2 | Q1=136 | R=1          |

| 136 ÷ 2 | Q2=68  | R=0          |

| 68 ÷2   | Q3=34  | R=0          |

| 34÷2    | Q4=17  | R=0          |

| 17÷2    | Q5=8   | R=1          |

| 8÷2     | Q6=4   | R=0          |

| 4÷2     | Q7=2   | R=0          |

| 2÷2     | Q8=1   | R=0          |

| 1÷2     | 0      | R=1          |

Thus  $546_{10} = 1000100010_2$

To convert Fraction:

Convert  $(0.731)_{10}$  to base 2

soln

0.731\*2=**1**.462

0.462\*2=**0**.924 0.924\*2=**1**.848 0.848\*2=**1**.696 0.696\*2=**1**.392 0.392\*2=**0**.784 0.784\*2=**1**.568

$(0.731)_{10} = (.1011101)2$

For a number that has both integral and fractional parts, conversion is done separately for both parts, and then the result is put together with a system point in between both parts.

E.gconvert 5.  $275_{10}$  to base 2

For the integral part.

$5_{10}$  is  $101_2$  from example above

Then the fraction part is computed as follows

|          |       | <b>A</b> |

|----------|-------|----------|

| .275 *2= | 0.550 |          |

| .550*2=  | 1.100 |          |

| .100*2=  | 0.200 |          |

| .200*2=  | 0.400 |          |

| .400*2=  | 0.800 |          |

| .800*2=  | 1.600 |          |

| .600*2=  | 1.200 |          |

|          |       |          |

5.  $275_{10} = 101.\ 0100011_2$

Convert the following base 10 numbers into their binary equivalent

50, 100, 10.2, 0.234

$50 = 110010_2$  $100 = 1100100_2$ 10.2 =0.234 =

#### 3.3 Octal System

The octal number system provides a convenient way to express binary numbers and codes. However, it is used less frequently than hexadecimal in conjunction with computers and microprocessors to express binary quantities for input and output purposes. Here we have,

r = 8 (Eight =  $2^3$ )

Eight Allowed Digits {0, 1, 2, 3, 4, 5, 6, 7}

#### Conversion from octal to decimal

Examples

Find the decimal value of the two Octal numbers  $(375)_8$  and  $(2.746)_8$

$$(375)_8 = 3x8^2 + 7x8^1 + 5x8^0$$

= 3x64+ 7x8 + 5x1

= (253)\_{10}

$$(2.746)_8 = 2x8^0 + 7x8^{-1} + 4x8^{-2} + 6x8^{-3}$$

=2 + 7/8+4/64 + 6/512

$= (2.94921875)_{10}$

Binary To Octal Conversion

| Group of 3 binary bits | Octal equivalence |

|------------------------|-------------------|

| 0 0 0                  | 0                 |

| 0 0 1                  | 1                 |

| 0 1 0                  | 2                 |

| 0 1 1                  | 3                 |

| 1 0 0                  | 4                 |

| 1 0 1                  | 5                 |

| 1 1 0                  | 6                 |

| 1 1 1                  | 7                 |

Example :

Convert (1110010101.1011011)2 into Octal.

We first partition the Binary number into groups of 3 bits

$001\_110\_010\_101\_101\_101\_100$

=1625.5548

Convert 11110010100010100 into octal

Group into group of 3 bits

011 /110 /010 /100 /010/100

=3624248

3.4 Hexadecimal System:

The hexadecimal number system has sixteen characters; it is used primarily as a compact way of displaying or writing binary numbers because it is very easy to convert between binary and hexadecimal. As you are probably aware, long binary numbers are difficult to read and write because it is easy to drop or transpose a bit.

Since computers and microprocessors understand only 1 s and 0s, it is necessary to use these digits when you program in "machine language." Imagine writing a sixteen bit instruction for a microprocessor system in 1s and 0s. It is much more efficient to use hexadecimal or octal; octal numbers are covered in the previous section. Hexadecimal is widely used in computer and microprocessor applications. So,

r = 16 (Sixteen =  $2^4$ )

Sixteen Allowed Digits {0-to-9 and A, B, C, D, E, F} Where: A = ten, B = Eleven, C = Twelve, D = Thirteen, E = Fourteen & F = Fifteen.

• Q: Why is the digit following 9 assigned the character A and not "10"?

• A: What we need is a *single* digit whose value is *ten*, but "10" is actually

*two digits* not *one*. Thus, in Hexadecimal system the 2-digit number  $(10)_{16}$  actually represents a value of *sixteen* not *ten* { $(10)_{16} = 0x_{16}^1 + 1x_{16}^0 = (16)_{10}$ }.

#### Conversion from Hexadecimal to Decimal

One way to convert a hexadecimal number to its decimal equivalent is to multiply the decimal value of each hexadecimal digit by its weight and then take the sum of these products. The weights of a hexadecimal number are increasing powers of 16 (from right to left). Anotherway is to convert first to binary and then to decimal

#### Example

Find the decimal value of the two Hexadecimal numbers (9E1)<sub>16</sub> and(3B.C)<sub>16</sub>

$$(9E1)_{16}$$

or  $9E1_{hex} = 9x16^2 + Ex16^1 + 1x16^0$

$= 9x256 \times 14x16 \times 1x1$

= (2529)<sub>10</sub>

$$(3B.C)_{16} = 3x16^1 + Bx16^0 + Cx16^{-1}$$

$$= 3x16^{1} + 11x16^{0} + 12x16^{-1}$$

$= (59.75)_{10}$

Conversion from Binary To Hexadecimal

Converting a binary number to hexadecimal is a straightforward procedure. Simply break the binary number into 4-bit groups, starting at the right-most bit and replaces each 4-bit group with the equivalent hexadecimal symbol.

| Group of 4 bits | Hexadecimal |

|-----------------|-------------|

| equivalence     |             |

| 0000            | 0           |

| 0 0 0 1         | 1           |

| 0010            | 2           |

| 0011            | 3           |

| 0100            | 4           |

| 0101            | 5           |

| 0110            | 6           |

| 0111            | 7           |

| 1000            | 8           |

| 1001            | 9           |

| 1010            | А           |

| 1011            | В           |

| 1100            | С           |

| 1101            | D           |

| 1110            | Е           |

| 1111            | F           |

Example :

Convert (1110010101.1011011)2 into Hexadecimal.

First group into 4bits

0011\_1001\_0101\_.1011\_0110

$=(395.B6)_{16}$

#### Convert 11001010010101111 in binary to hexadecimal

Break into four 4bits

To convert from a hexadecimal number to a binary number, reverse the process and replace each hexadecimal symbol with the appropriate four bits.

CF8E  $_{16}$ = C-1100 F-1111 8- 1000 E-1110 = 1100111110001110<sub>2</sub>

Conversion from Octal to Hexadecimal

Example: Convert 356<sub>8</sub> to hexadecimal Soln

$356_8 = 11101110_2$

= 1110/1110

$= EE_{16}$

Question. What is the result of adding 1 to the largest digit of some number system?? Answer.

For the decimal number system,  $(1)_{10} + (9)_{10} = (10)_{10}$

For the octal number system,  $(1)_8 + (7)_8 = (10)_8 = (8)_{10}$

For the hex number system,  $(1)_{16} + (F)_{16} = (10)_{16} = (16)_{10}$

For the binary number system,  $(1)_2 + (1)_2 = (10)_2 = (2)_{10}$

Conclusion. Adding 1 to the largest digit in any number system always has a result of (10) in that number system.

Question. What is the largest value representable in 3-integral digits?

Answer. The largest value results when all 3 positions are filled with the largest digit in the number system.

\_\_\_\_\_

For the decimal system, it is (999)10

For the octal system, it is (777)8

For the hex system, it is (FFF)16

For the binary system, it is (111)2

\_\_\_\_\_

Clarification (c)

Q. What is the result of adding 1 to the largest 3-digit number?

#### ?

A.

For the decimal system, (1)10 + (999)10 = (1000)10 = (103)10

For the octal system, (1)8 + (777)8 = (1000)8 = (83)10

For the hex system, (1)16 + (FFF)16 = (1000)16 = (163)16

For the binary system, (1)2 + (111)2 = (1000)2 = (23)10

In general, for a number system of radix r, adding 1 to the largest n-digit

number =  $r^n$

Accordingly, the value of largest *n*-digit number =  $r^{n}$ -1

Convert A4C in Hex to Decimal

#### Self assessment Answers

A4C= 2636

#### **Conclusions.**

1. In any number system of radix r, the result of adding 1 to the *largest n-digit* number equals  $r^{n}$

2. Thus, the value of the *largest n-digit* number is equal to  $r^n - I$

3. Thus, *n* digits can represent *r n* different values (digit combinations) starting from a 0 value up to the largest value of  $r^{n}$  -1

The table below gives the comparison between decimal, binary, octal and hexadecimal

| Table 1:Comparison Table |

|--------------------------|

|--------------------------|

| Base, b     | Byte (8-bits)                | Word (16-bits)                         |

|-------------|------------------------------|----------------------------------------|

| Decimal     | 0<br>to                      | 0<br>to                                |

|             | $255_{10}$                   | 65,53510                               |

|             | 0000                         | 0000 0000 0000 0000 0000               |

| Binary      | to<br>1111 1111 <sub>2</sub> | to<br>1111 1111 1111 1111 <sub>2</sub> |

|             | 00                           | 0000                                   |

| Hexadecimal | to                           | to                                     |

|             | $FF_{16}$                    | FFFF <sub>16</sub>                     |

|             | 000                          | 000 000                                |

| Octal       | to                           | to                                     |

|             | 3778                         | 177 7778                               |

#### Self Assessment Questions

- 1. The octal equivalent of  $247_{10}$

- 2. The hexadecimal number for 95.5 10 is

- 3. Convert (10001011.011)<sub>2</sub> to decimal

- 4. Convert 5678 to hexadecimal

- 5. The binary equivalent of FA 16 is

#### Self Assessment answers

#### 4.0 Conclusion

In this unit various number system are considered namely decimal, binary, hexadecimal and octal. How to convert from one number system to another were also discussed.

#### 5.0 Summary

You have learnt:

A binary number is a weighted number in which the weight of each whole number digit is a positive power of two and the weight of each fractional digit is a negative power of two.

The whole number weights increase from right to left-from least significant digit to most significant.

. A binary number can be converted to a decimal number by summing the decimal values of the weights of all the Is in the binary number.

.A decimal whole number can be converted to binary by using the sum-of-weights or the repeated division-by-2 method.

A decimal fraction can be converted to binary by using the sum-of-weights or the repeated multiplication-by-2 method.

The hexadecimal number system consists of 16 digits and characters, 0 through 9 followed by A through F.

One hexadecimal digit represents a 4-bit binary number, and its primary usefulness is in simplifying bit patterns and making them easier to read.

A decimal number can be converted to hexadecimal by the repeated division-by-16 method.

The octal number system consists of eight digits, 0 through 7.

A decimal number can be converted to octal by using the repeated division-by-8 method.

Octal-to-binary conversion is accomplished by simply replacing each octal digit with its 3-bit binary equivalent. The process is reversed for binary-to-octal conversion.

#### 6.0 Tutor Marked Assignment

Convert each binary number to decimal, octal and hexadecimal:

(a) 11001111 (d) 1111000.101 (g) 10110101010 (e) 1011100.10101 (h) 111111 1.1 1111

Convert the following from Hexadecimal to binary ,octal and decimal  $ADE_{16}$  (b)  $FFFF_{16}$  (c)  $52C_{16}$ Convert the following from decimal to binary, octal and hexadecimal

(a)245 (b)75 (c) 120

#### 7.0 References/Further Reading

Ronald J. T. & Neal S., (2001). Widmer Digital Systems: Principle and Applications (8th Ed.) Prentice Hall,

Thomas L F., (2006). Digital Fundamentals (9th Ed.). Prentice Hall.

Morris M. & Charles R. K. (2004) Logic and Computer Design Fundamentals. (2004) NJPrentice Hall

Wakerly J.F. (2000). Digital Design: Principles and Practices (3rd Ed.) Upper Saddle River NJ; Prentice

<a href="http://www.swarthmore.edu/NatSci/.../BinaryMath/BinaryMath.html">http://www.swarthmore.edu/NatSci/.../BinaryMath/BinaryMath.html</a>

<a href="http://www.allaboutcircuits.com">http://www.allaboutcircuits.com</a>

<a href="http://www.13d.cs.colorado.edu/courses/CSCI1200-96/binary.html">http://www.ltml</a>

# Unit 3

## Binary Codes and Arithmetic

#### Content

- 1.0 Introduction

- 2.0 Learning Outcomes

- 3.0 Learning Contents

- 3.1 Binary Codes for Decimal

- 3.2 Compliment Representation

- 3.3 Error detection codes

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

#### 1.0 Introduction

Internally, digital computers operate on binary numbers. When interfacing to humans, digital processors, e.g. pocket calculators, communication is decimal based. Input is done in decimal then converted to binary for internal processing. For output, the result has to be converted from its internal binary representation to a decimal form. To be handled by digital processors, the decimal input (output) must be coded in binary in a digit by digit manner.

#### 2.0 Learning Outcomes

At the end of this unit, you should be able to:

Explain several binary codes includingBinary Coded Decimal (BCD), Error detection codes, and Character codes Differentiate between coding and binary conversion. Calculate the 2's complement of a given n-bit binary number. Explain the differences between signed-magnitude, signed-1's complement and signed-2's complement representations of negative binary numbers. Perform subtraction problems in base 2 using the 2's complement method. Express numbers in binary-coded decimal (BCD), Perform integer binary arithmetic that is addition and subtraction Describe and use two's complement and sign and magnitude to represent negative integers

#### 3.0 Learning Contents

#### 3.1 Binary Codes for Decimal Digits

There is a variety ofdecimal binary codesand they are shown in table 3.1

#### **BINARY CODED DECIMAL (BCD)**

One commonly used code is the *Binary Coded Decimal* (**BCD**) code which corresponds to the first 10 binary representations of the decimal digits 0-9. Binary Coded Decimal is one of the early memory encodings. Rather than converting the entire denary value into its pure binary form, it converts each digit, separately, into its 4-bit binary equivalent. The table below shows the 4-bit BCD equivalents of the ten denary digits:

The BCD code requires 4 bits to represent the 10 decimal digits. Since 4 bits may have up to 16 different binary combinations, a total of 6 combinations will be unused. The position weights of the BCD code are 8, 4, 2, 1.

Other codes (shown in the table) use position weights of 8, 4, -2, -1 and 2, 4, 2, 1.

What does the BCD stand for ?

#### BCD stands for Binary Coded Decimal

An example of a non-weighted code is the *excess-3 code* where digit codes is obtained from their binary equivalent after adding 3. Thus the code of a decimal 0 is 0011, that of 6 is1001, etc.

| Decimal | BCD          |              |              |          |

|---------|--------------|--------------|--------------|----------|

| Digit   | 8 4 2 1      | 84-2-1       | 2421         | Excess-3 |

|         |              |              |              |          |

| 0       | 0000         | 0000         | 0000         | 0011     |

| 1       | 0001         | 0111         | 0001         | 0100     |

| 2       | 0010         | 0110         | 0010         | 0101     |

| 3       | 0011         | 0101         | 0011         | 0110     |

| 4       | 0100         | 0100         | 0100         | 0111     |

| 5       | 0101         | 1011         | 1011         | 1000     |

| 6       | 0110         | 1010         | 1100         | 1001     |

| 7       | 0111         | 1001         | 1101         | 1010     |

| 8       | $1\ 0\ 0\ 0$ | $1\ 0\ 0\ 0$ | 1110         | 1011     |

| 9       | 1001         | 1111         | 1111         | 1 1 0 0  |

| U       | 1010         | 0001         | 0101         | 0000     |

| Ν       | 1011         | 0010         | 0110         | 0001     |

| U       | 1100         | 0011         | 0111         | 0010     |

| S       | 1101         | 1100         | $1\ 0\ 0\ 0$ | 1 1 0 1  |

| E       | 1110         | 1101         | 1001         | 1 1 1 0  |

| D       | 1111         | 1110         | 1010         | 1111     |

#### Table 3.1 decimal codes

#### Number Conversion VersusCoding

Converting a decimal number into binary is done by repeated division (multiplication) by 2for integers (fractions) (see lesson 2).Coding a decimal number into its BCD code is done by replacing each decimal digit of thenumber by its equivalent 4 bit BCD code.

Example Converting (13)10 into binary, we get 1101, coding the same number into BCD, weobtain 00010011.

Example: convert 011010000011 from BCD to decimal

Soln

Group in four bits 0110 1000 0011= 683

Convert (95)10 into its binary equivalent value and give its BCD code as well.

#### {(1011111)2, and 10010101}

#### 3.2 Compliment Representation

Positive numbers (+N) are represented in *exactly* the same way as in signed magnitude system

Negative numbers (-N) are represented by the *complement* of N (N')

One's and Two's Compliment Notation:

Two's compliment is a method of representing negative numbers in binary, whereby the most significant bit maintains its magnitude, but is made negative. In order to subtract one number from another, we need some means of representing negative numbers in binary notation. The "two's complement" convention is almost universally used for this purpose.

The '1's complement' of a binary number 0110 is just 1001 (obtained by inverting or negating each bit in the number). i.e. by bitwise complementing of each bit, i.e. each 1 is replaced by a 0 and each 0 is replaced by a 1.

The '2's complement' is formed by taking the '1's complement' and adding 1. Thus, the '2's complement' of 0110 is 1001 + 0001 = 1010. To show that this is the negative of the initial number (0110) simply add them 0110 + 1010 = 0000 plus a carry bit, which is ignored with an 8 bit number

Negative numbers will always start with a '1' and positives will start will a '0'; the range of integers that can be represented using one byte is from -128 up to +127.

e.g. decimal 18 is represented in a byte as 00010010 while -18 is 10010010

Likewise  $1\ 0\ 0\ 0\ 0\ 0\ 0 = -128$

$0\ 1\ 1\ 1\ 1\ 1\ 1\ 1\ =+\ 127$

0 0 0 0 0 1 1 0 the number

1 1 1 1 1 0 0 1 its 1's complement

1 1 1 1 1 0 1 0 its 2's complement

$0\ 0\ 0\ 0\ 0\ 1\ 1\ 0$  number to be added

$1\ 0\ 0\ 0\ 0\ 0\ 0\ 0$  the sum (difference)

as before, we neglect the carry bit. Notice that the most significant bit of the negative number is a 1 while that of the positive number is a 0. This is a necessary feature of two's complement arithmetic. This makes it easy to test whether a number is positive or negative, you simply check its most significant bit.

Find the 1's and the 2's complement of 110101010

001010101- 1's Complement

001010110- 2's Complement

Converting A Negative Denary Integer Into Two's Complement

Taking the denary integer -52 as an example

First convert to unsigned binary

$+52 = 0\ 0\ 1\ 1\ 0\ 1\ 0\ 0$

Convert to 1's complement

$1 \ 1 \ 0 \ 0 \ 1 \ 0 \ 1 \ 1$

Then finally to 2's complement

$1 \ 1 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0$

Converting a Two's Complement Number Into Denary

This is the same as converting any binary number into denary, as long as you remember that the most significant bit is negative. For example the 'signed' binary number 1 1 0 1 0 1 0 1 is converted as follows:

$-128 \ 64 \ 32 \ 16 \ 8 \ 4 \ 2 \ 1$  $1 \ 1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 1$ = -128 + 64 + 16 + 4 + 1= -43

#### Sign and Magnitude

The alternative to using two's complement to represent negative numbers is to use the 'sign and magnitude' method - here, the most significant bit is used as a sign bit without a numerical value.

Convert 1 1 0 0 1 1 0 0 in 2's complement to decimal

64

32

16

8

4

2

1

1

1

0

0

1

1

0

0

=-(64+8+4)

= -76

Notes:s

The range of integers that can be represented using one byte is from -127 up to +127. although the sign and magnitude method is easier for humans it is much harder to use for computers performing arithmetic.

a). Assuming a single byte is used, convert the following numbers into two's compliment binary:(a) -5 (b) -10 (c) -20 (b). What is the denary value of 1010 1011 if the binary codes represent: (a) a two's compliment number (b) a sign and magnitude number

Addition And Subtraction of Numbers Using1's And 2's Compliment

Addition:Computers will only ever add two numbers at a time – if three numbers need to be added, a computer will add the first two and then add the third number will be added to the result.

**Subtraction:** To perform subtraction, the number to be subtracted is converted into its two's compliment negative and then added

Perform 12 + 25, 25 - 12, 12 - 25  $12 = 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0$   $25 = 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0 \ 1$   $+ = 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 1$  = 37  $-12 = 1 \ 1 \ 1 \ 1 \ 0 \ 1 \ 0 \ 0 \ (2's compliment of 12)$  $25 = 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0 \ 1$

$+ = 10 \ 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 1$

= 13

Discard the carry 1

$12=0\ 0\ 0\ 0\ 1\ 1\ 0\ 0$  $-25=1\ 1\ 1\ 0\ 0\ 1\ 1\ 1$  $+=1\ 1\ 1\ 0\ 0\ 1\ 1$

The answer is in two's compliment which is equal to -13

Try these questions

Computer the following using 2's compliments arithmetic

34-78 34+78 100-34 34-100

#### 3.3 Error-Detection Codes

Binary information may be transmitted through some communication medium, e.g. usingwires or wireless media. A corrupted bit will have its value changed from 0 to 1 or vice versa. To be able to detect errors at the receiver end, the sender sends an extra bit (*parity bit*) with the original binary message.

A *parity bit* is an extra bit included with the *n*-bit binary message to make the total number 1's in this message (*including the parity bit*) either odd or even. If the *parity bit* makes the total number of 1's an odd (even) number, it is called odd (even) parity.

The table shows the *required* odd (*even*) *parity* for a 3-bit message. At the receiver end, an error is detected if the message does not match have the proper parity (odd/even). Parity bits can detect the occurrence 1, 3, 5 or any odd number of errors in the transmitted message.

| Three-Bit Message | Odd Parity Bit | Even Parity Bit |  |

|-------------------|----------------|-----------------|--|

| XYZ               | P              | Р               |  |

|                   |                |                 |  |

| 000               | 1              | 0               |  |

| 0 0 1             | 0              | 1               |  |

| 010               | 0              | 1               |  |

| 011               | 1              | 0               |  |

| 100               | 0              | 1               |  |

| 101               | 1              | 0               |  |

| 110               | 1              | 0               |  |

| 111               | 0              | 1               |  |

Table 2

No error is detectable if the transmitted message has 2 bits in error since the total number of 1's will remain even (or odd) as in the original message.

In general, a transmitted message with even number of errors cannot be detected by the parity bit.

#### Self assessment Question

What do you understand by parity bit

#### Self Assessment Answers

A *parity bit* is an extra bit included with the *n*-bit binary message to make the total number of 1's in this message either odd or even.

#### Gray Code

The Gray code is unweighted and is not an arithmetic code; that is, there are no specific weights assigned to the bit positions. The important feature of the Gray code is that it exhibits only a single bit change from one code word to the next in sequence. The Gray code consist of 16 4-bit code words to represent the decimal Numbers 0 to 15. It is useful in applications like analog to digital conversion. This property is important in many applications, such as shaft position encoders, where error susceptibility increases with the number of bit changes between adjacent numbers in a sequence For Gray code, successive code words differ by only one bit from one to the next as shownin the table and further illustrated in the table below.

|      | Gray Code | Decimal Equivalent |        |

|------|-----------|--------------------|--------|

|      | 0000      | 0                  |        |

| What | 0001      | 1                  | is the |

|      | 0011      | 2                  |        |

|      | 0010      | 3                  |        |

|      | 0110      | 4                  |        |

|      | 0111      | 5                  |        |

|      | 0101      | 6                  |        |

|      | 0100      | 7                  |        |

|      | 1100      | 8                  |        |

|      | 1101      | 9                  |        |

|      | 1111      | 10                 |        |

|      | 1110      | 11                 |        |

|      | 1010      | 12                 |        |

|      | 1011      | 13                 |        |

|      | 1001      | 14                 |        |

|      | 1000      | 15                 |        |

characteristic feature of the Gray Code

The important feature of the Gray code is that it exhibits only a single bit change from one code word to the next in sequence

Binary-to-Gray Code Conversion

Conversion between binary code and Gray code is sometimes useful. The following rules explain how to convert from a binary number to a Gray code word:

1. The most significant bit (left-most) in the Gray code is the same as the corresponding MSB in the binary number.

2. Going from left to right, add each adjacent pair of binary code bits to get the next Gray code bit. Discard carries.

For example, the conversion of the binary number 10110 to Gray code is as follows:

1+0+l+l+0 binary

1 1 1 0 1 gray

the gray code is 11101

Gray-to-Binary Conversion

To convert from Gray code to binary, use a similar method; however, there are some differences. The following rules apply:

1. The most significant bit (left-most) in the binary code is the same as the corresponding bit in the Gray code.

2. Add each binary code bit generated to the Gray code bit in the next adjacent position. Discard carries.

For example, the conversion of the Gray code word 11011 to binary is as follows:

1 then 1+1=0 then 0+0=0 then 0+1=1 then 1+0=0

=10010

#### Self Assessment Question

(a) Convert the binary number 11000110 to Gray code.(b) Convert the Gray code 10101111 to binary.

#### **Character Codes**

ASCII Character Code

ASCII code is a 7-bit code.*American Standard Code for Information Interchange (ASCII)* is used for character encoding by most Windows<sup>TM</sup> PCs. ASCII can be used to translate alphanumeric characters into a 7-bit binary code that represents all the characters available from the keyboard including punctuation and some special symbols such as '@', # and \$:

It is used in communicating information between a computer and its peripherals or other computers.

|    |    | 0/1 |    | - 01 |   | E ASC |   | 17 U U |   |    | •• |    |   |    |   |    |   |     |   |     |   |     |   |

|----|----|-----|----|------|---|-------|---|--------|---|----|----|----|---|----|---|----|---|-----|---|-----|---|-----|---|

|    |    | 33  | !  | 41   | ) | 49    | 1 | 57     | 9 | 65 | Α  | 73 | I | 81 | Q | 89 | Y | 97  | а | 105 | i | 113 | q |

|    |    | 34  |    | 42   | * | 50    | 2 | 58     | : | 66 | в  | 74 | J | 82 | R | 90 | z | 98  | b | 106 | j | 114 | r |

|    |    | 35  | #  | 43   | + | 51    | 3 | 59     | ; | 67 | С  | 75 | к | 83 | S | 91 | [ | 99  | с | 107 | k | 115 | s |

|    |    | 36  | \$ | 44   | , | 52    | 4 | 60     | < | 68 | D  | 76 | L | 84 | т | 92 | ١ | 100 | d | 108 | Т | 116 | t |

|    |    | 37  | %  | 45   | - | 53    | 5 | 61     | = | 69 | Е  | 77 | м | 85 | U | 93 | ] | 101 | е | 109 | m | 117 | u |

|    |    | 38  | &  | 46   |   | 54    | 6 | 62     | > | 70 | F  | 78 | Ν | 86 | v | 94 | ^ | 102 | f | 110 | n | 118 | v |

|    |    | 39  | •  | 47   | 1 | 55    | 7 | 63     | ? | 71 | G  | 79 | 0 | 87 | w | 95 | _ | 103 | g | 111 | 0 | 119 | w |

| 32 | SP | 40  | (  | 48   | 0 | 56    | 8 | 64     | @ | 72 | н  | 80 | Р | 88 | х | 96 | • | 104 | h | 112 | р | 120 | x |

A development of ASCII, known as *Extended ASCII*, uses an 8-bit code that also defines codes for additional characters, including some graphical ones. Note that using an 8-bit code means the maximum number of characters that can be represented is 256.

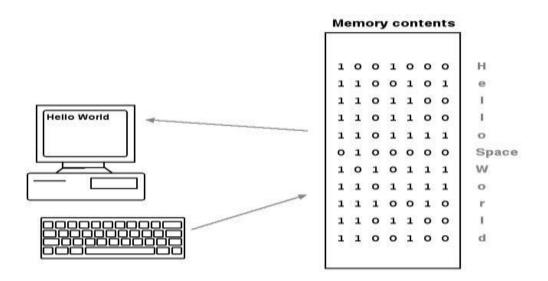

#### How Character Encoding Works

The diagram below shows how the message "Hello World" is stored in the memory of a computer using the ASCII codes:

The message is typed at the keyboard. Electronics in the keyboard convert the typed characters intoASCII binary codes that are sent from the keyboard along a cable to the computer. The computerstores these codes in its internal memory. The computer also provides a visual display of thecharacters as they are typed. To be able to do this, electronics inside the computer convert thestored binary codes back into their character equivalents.

#### Extended Binary Coded Decimal Interchange Code (EBCDIC)

*Extended Binary Coded Decimal Interchange Code (EBCDIC)* was developed by IBM for use in their mainframe systems. It has the same limitation as ASCII in that its 8-bit code can only define 256 different characters. Notice how the EBCDIC codes are completely different to ASCII – if a message was sent that had been encoded using ASCII, but received by a system that used EBCDIC, then the resulting message would not make sense.

|    |   | SAN | ٨P | LE | OF  | THE | EBO | DIC | CHA | RAC | TER | SET |     |   |       |     |   |     |   |     |   |     |    |

|----|---|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|-------|-----|---|-----|---|-----|---|-----|----|

| 65 |   | 81  |    |    | 97  | 1   | 113 |     | 129 | a   | 145 | 1   | 161 | - | 177   | 193 | A | 209 | J | 225 |   | 241 | 1  |

| 66 |   | 82  |    |    | 98  |     | 114 |     | 130 | b   | 146 | ĸ   | 162 | 5 | 178   | 194 | в | 210 | к | 226 | s | 242 | 2  |

| 67 |   | 83  |    |    | 99  |     | 115 |     | 131 | c   | 147 | 1   | 163 | t | 179   | 195 | C | 211 | L | 227 | T | 243 | 3  |

| 68 |   | 84  |    |    | 100 |     | 116 |     | 132 | đ   | 148 | m   | 164 | u | 180   | 196 | D | 212 | м | 228 | U | 244 | 4  |

| 69 |   | 85  |    |    | 101 |     | 117 |     | 133 | 0   | 149 | n   | 165 | v | 181   | 197 | E | 213 | N | 229 | v | 245 | 5  |

| 70 |   | 86  |    |    | 102 |     | 118 |     | 134 | t   | 150 | 0   | 166 | w | 182   | 198 | F | 214 | 0 | 230 | w | 246 | 6  |

| 71 |   | 87  |    |    | 103 |     | 119 |     | 135 | 9   | 151 | p   | 167 | x | 183   | 199 | G | 215 | P | 231 | x | 247 | 7  |

| 72 |   | 88  |    |    | 104 |     | 120 |     | 136 | h   | 152 | q   | 168 | y | 184   | 200 | н | 216 | Q | 232 | Y | 248 | 8  |

| 73 |   | 89  |    |    | 105 |     | 121 | •   | 137 | 1   | 153 | r   | 169 | z | 185   | 201 | 1 | 217 | R | 233 | z | 249 | 9  |

| 74 | ¢ | 90  | t  |    | 106 | 1   | 122 | 1   | 138 |     | 154 |     | 170 |   | 186   | 202 |   | 218 |   | 234 |   | 250 | 1  |

| 75 | 4 | 91  | \$ |    | 107 |     | 123 | #   | 139 |     | 155 |     | 171 |   | 187   | 203 |   | 219 |   | 235 |   | 251 |    |

| 76 | > | 92  | ٠  |    | 108 | %   | 124 | @   | 140 |     | 156 |     | 172 |   | 188   | 204 |   | 220 |   | 236 |   | 252 |    |

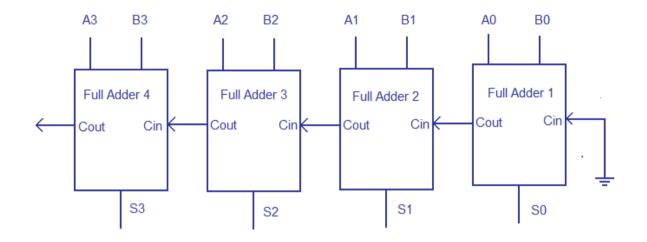

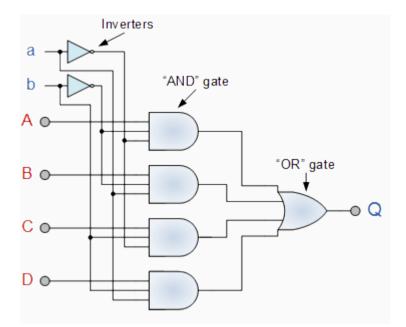

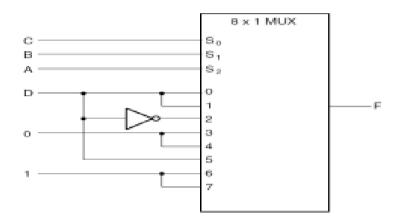

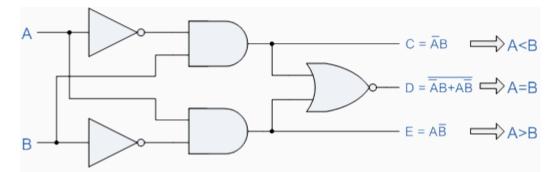

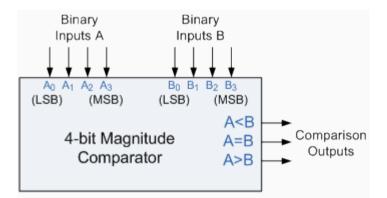

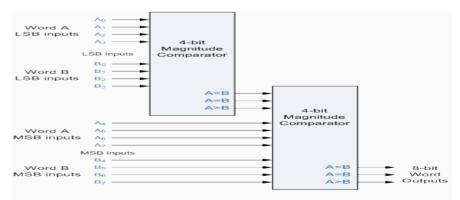

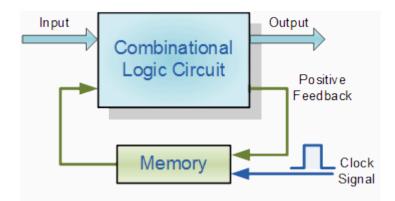

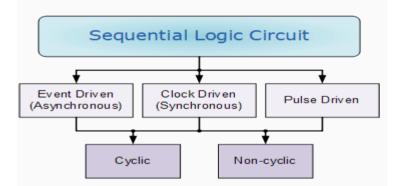

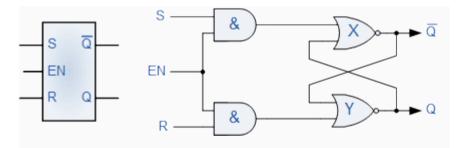

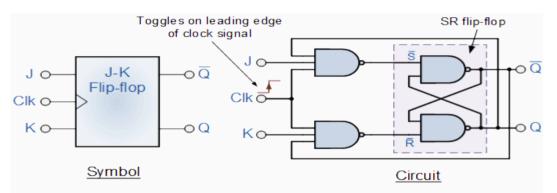

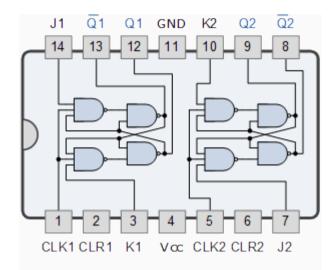

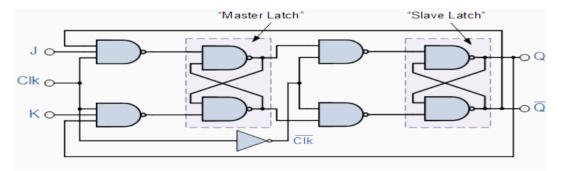

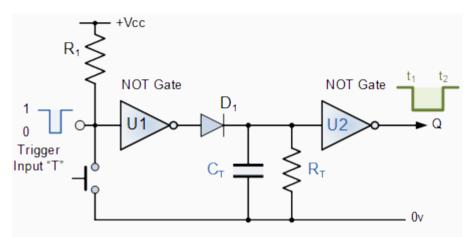

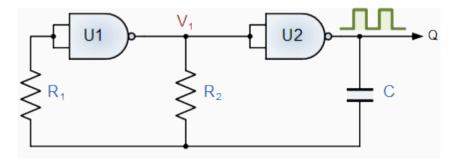

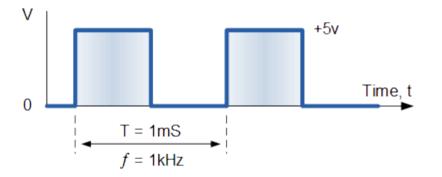

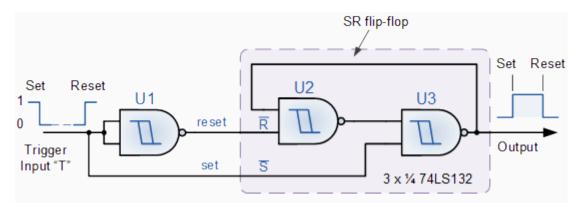

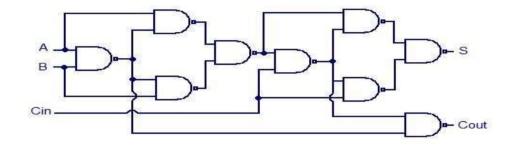

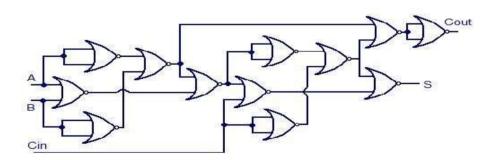

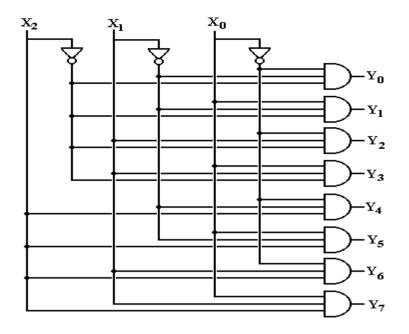

| 77 | ( | 93  | )  |    | 109 |     | 125 | *   | 141 |     | 157 |     | 173 |   | 189   | 205 |   | 221 |   | 237 |   | 253 |    |