# **CPT 214**

# Computer Architecture

# FEDERAL UNIVERSITY OF TECHNOLOGY, MINNA NIGER STATE, NIGERIA

# CENTRE FOR OPEN DISTANCE AND e-LEARNING (CODeL)

# **B.TECH. COMPUTER SCIENCE PROGRAMME**

COURSE TITLE COMPUTER ARCHITECTURE

> COURSE CODE CPT 214

# COURSE CODE CPT 214

# COURSE UNIT

# 3

### **Course Coordinator**

Bashir MOHAMMED (Ph.D.) Department of Computer Science Federal University of Technology (FUT) Minna Minna, Niger State, Nigeria.

# Course Development Team

# CPT 214: Computer Architecture

| Subject Matter Experts         | John K. Alhassan (Ph.D.)<br>Department of Cyber Security<br>FUT Minna, Nigeria.             |

|--------------------------------|---------------------------------------------------------------------------------------------|

| Course Coordinator             | Bashir MOHAMMED (Ph.D.)<br>Department of Computer Science<br>FUT Minna, Nigeria.            |

| ODL Experts                    | Amosa Isiaka GAMBARI (Ph.D.)<br>Nicholas E. ESEZOBOR                                        |

| Instructional System Designers | Oluwole Caleb FALODE (Ph.D.)<br>Bushrah Temitope OJOYE (Mrs.)                               |

| Language Editors               | Chinenye Priscilla UZOCHUKWU (Mrs.)<br>Mubarak Jamiu ALABEDE                                |

| Centre Director                | Abiodun Musa AIBINU (Ph.D.)<br>Centre for Open Distance & e-Learning<br>FUT Minna, Nigeria. |

# CPT 214 Study Guide

# Introduction

**CPT 214 Computer Architecture** is a 3- credit unit course for students studying towards acquiring a Bachelor of Science in any field. The course is divided into 5 modules and 16 study units. It will first introduce to digital logics. Then, memory system. Thereafter, interfacing and communication is discussed. This is followed by an extensive discussion on the introduction of networks, raid architectures, Data Path and control. And finally, instruction pipelining, riscs and multiprocessors.

The course guide therefore gives you an overview of what CPT 214 is all about, the textbooks and other materials to be referenced, what you expect to know in each unit, and how to work through the course material.

# Recommended Study Time

This course is a 3-credit unit course having 16 study units. You are therefore enjoined to spend at least 2 hours in studying the content of each study unit.

# What You Are About to Learn in This Course

The overall aim of this course, CPT 214 is to introduce you to computer architecture. At the end of this course you would have learnt the:

- i. basic computing programmes

- ii. various components of digital logic

- iii. memory system and how to effectively use storage system

- iv. the usage of network for raid architectures and Data Path control

- v. multiprocessors, riscs and instruction pipelining

# Course Aims

This course aims to introduce students to the concept of computer architecture. It is expected that the knowledge will enable the reader to effectively use computers in his/her profession.

# Course Objectives

It is important to note that each unit has specific objectives. Students should study them carefully before proceeding to subsequent units. Therefore, it may be useful to refer to these objectives in the course of your study of the unit to assess your progress. You should always look at the unit objectives after completing a unit. In this way, you can be sure that you have done what is required of you by the end of the unit.

However, below are overall objectives of this course. On completing this course, you should be able to:

i. Define computer architecture

- ii. Explain digital logic

- iii. Explain related technologies to memory system

- iv. Describe the categories of computer hardware

- v. Discuss interfacing and communication

- vi. Explain the functions of networks and how it's being used

- vii. Describe how RISCs works

- viii. Differentiate between cache memory and virtual memory

# Working Through This Course

In order to have a thorough understanding of the course units, you will need to read and understand the contents, practice the steps and implement the knowledge you've gained for your department.

This course is designed to cover approximately sixteen weeks, and it will require your devoted attention. You should do the exercises in the Tutor-Marked Assignments and submit to your tutors.

# Course Materials

The major components of the course are:

- 1. Course Guide

- 2. Study Units

- 3. Text Books

- 4. Assignment File

- 5. Presentation Schedule

# Study Units

There are 16 study units and 5 Modules in this course. They are:

|              | Digital lo | Digital logic                                |  |

|--------------|------------|----------------------------------------------|--|

| Module One   | Unit 1     | Fundamental Building Blocks of Digital Logic |  |

|              | Unit 2     | Programmable Logic Array (PLA)               |  |

|              | Memory     | System                                       |  |

|              | Unit 1     | Storage System and their Technologies        |  |

| Module Two   | Unit 2     | Data Compression and Data Integrity          |  |

|              | Unit 3     | Memory Hierarchy, Organisation and Operation |  |

|              | Unit 4     | Cache memory and Virtual Memory              |  |

|              | Interfaci  | Interfacing and Communication                |  |

|              | Unit 1     | Input/output Fundamentals                    |  |

| Module Three | Unit 2     | Handshaking                                  |  |

|              | Unit 3     | Data Buffer                                  |  |

|              | Unit 4     | External Storage                             |  |

|             | Introduction to Network, Raid Architectures, Data Path & Control |                                                           |

|-------------|------------------------------------------------------------------|-----------------------------------------------------------|

| Module Four | Unit 1                                                           | Introduction to Network                                   |

|             | Unit 2                                                           | Multimedia Support raid architecture                      |

|             | Unit 3                                                           | Data Path and Control Unit                                |

|             | Instruction Pipelining, RISCS and Multiprocessors                |                                                           |

|             | Unit 1                                                           | Instruction pipelining                                    |

| Module Five | Unit 2                                                           | Introduction to reduced instruction set computers (RISCS) |

|             | Unit 3                                                           | Introduction to multiprocessors                           |

# Recommended Texts

The following texts and Internet resource links will be of enormous benefit to you in learning this course:

- 1. Baron, Robert J. and Higbie Lee. *Computer Architecture*. Addison-Wesley Publishing Company.

- 2. Daniel P, and David G, (2009). A Practical Introduction to Computer Architecture. Text in Computer Science, Springer Dordrecht Heidelberg London New York.

- 3. Flautner, K. Kim, N.S. Martin, S. Blaauw D. and Mudge, T.N. Drowsy Caches: Simple Techniques for Reducing Leakage Power. In *International Symposium on Computer Architecture. (ISCA)*, 148–157, 2002

- 4. Hayes, John P. (1998). *Computer Architecture and Organisation* (2nd ed). McGraw-Hill International editions.

- 5. Hennessy J.L and Patterson, D.A. *Computer Architecture: A Quantitative Approach*, Morgan Kaufmann, 2006. ISBN: 0-123-70490-1.

- 6. Mano, M. Morris, (1993). Computer System Architecture (3rd ed). Prentice Hall of India.

- 7. Miles J, and Vincent P. H. (1999). Principle of Computer Architecture Class Test Edition, August 1999. http://www.cs.rutgers.edu/~murdocca/

- 8. Mostafa A. E.B and Hesham E. R, (2005). Fundamentals of Computer Organization and Architecture. Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

- 9. http://ece-www.colorado.edu/faculty/heuring.html

- NOUN, (2008). INTRODUCTION TO COMPUTER ORGANISATION. CIT 246 Course Material, National Open University of Nigeria, Headquarters 14/16 Ahmadu Bello Way, Victoria Island, Lagos. First Printed 2008

- 11. Stallings William. *Computer Organisation and Architecture* (3rd ed). Maxwell Macmillan International Editions.

- 12. Tanenbaum, Andrew S. (1993). *Structural Computer Organisation* (3<sup>rd</sup> Ed.) Prentice Hall of India.

- 13. http://websrv.cs.fsu.edu/~tyson/CDA5155/refs.html

- 14. http://www.cs.ucsd.edu/classes/wi99/cse141\_B/lectures.html

- 15. http://www.cs.caltech.edu/courses/cs184/ winter2001/slides/day5\_2up.pdf

- 16. http://www.cs.iastate.edu/~prabhu/Tutorial/PIPELINE/compSched.html

- 17. http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/

# Assignment File

The assignment file will be given to you in due course. In this file, you will find all the details of the work you must submit to your tutor for marking. The marks you obtain for these assignments will count towards the final mark for the course. Altogether, there are tutor marked assignments for this course.

# Presentation Schedule

The presentation schedule included in this course guide provides you with important dates for completion of each tutor marked assignment. You should therefore endeavour to meet the deadlines.

### Assessment

There are two aspects to the assessment of this course. First, there are tutor marked assignments; and second, the written examination. Therefore, you are expected to take note of the facts, information and problem solving gathered during the course. The tutor marked assignments must be submitted to your tutor for formal assessment, in accordance to the deadline given. The work submitted will count for 40% of your total course mark.

At the end of the course, you will need to sit for a final written examination. This examination will account for 60% of your total score. You will be required to submit some assignments by uploading them to CPT 214 page on the u-learn portal.

# Tutor-Marked Assignment (TMA)

There are TMAs in this course. You need to submit all the TMAs. The best 10 will therefore be counted. When you have completed each assignment, send them to your tutor as soon as possible and make certain that it gets to your tutor on or before the stipulated deadline. If for any reason you cannot complete your assignment on time, contact your tutor before the assignment is due to discuss the possibility of extension. Extension will not be granted after the deadline, unless on extraordinary cases.

# Final Examination and Grading

The final examination for CPT 214 will last for a period of 3 hours and has a value of 60% of the total course grade. The examination will consist of questions which reflect the self-assessment questions and tutor marked assignments that you have previously encountered. Furthermore, all areas of the course will be examined. It would be better to use the time between finishing the last unit and sitting for the examination, to revise the entire course. You

might find it useful to review your TMAs and comment on them before the examination. The final examination covers information from all parts of the course.

# Practical Strategies for Working Through This Course

- 1. Read the course guide thoroughly

- 2. Organize a study schedule. Refer to the course overview for more details. Note the time you are expected to spend on each unit and how the assignment relates to the units. Important details, e.g. details of your tutorials and the date of the first day of the semester are available. You need to gather together all this information in one place such as a diary, a wall chart calendar or an organizer. Whatever method you choose, you should decide on and write in your own dates for working on each unit.

- Once you have created your own study schedule, do everything you can to stick to it. The major reason that students fail is that they get behind with their course works. If you get into difficulties with your schedule, please let your tutor know before it is too late for help.

- 4. Turn to Unit 1 and read the introduction and the learning outcomes for the unit.

- 5. Assemble the study materials. Information about what you need for a unit is given in the table of content at the beginning of each unit. You will almost always need both the study unit you are working on and one of the materials recommended for further readings, on your desk at the same time.

- 6. Work through the unit, the content of the unit itself has been arranged to provide a sequence for you to follow. As you work through the unit, you will be encouraged to read from your set books

- 7. Keep in mind that you will learn a lot by doing all your assignments carefully. They have been designed to help you meet the objectives of the course and will help you pass the examination.

- 8. Review the objectives of each study unit to confirm that you have achieved them. If you are not certain about any of the objectives, review the study material and consult your tutor.

- 9. When you are confident that you have achieved a unit's objectives, you can start on the next unit. Proceed unit by unit through the course and try to pace your study so that you can keep yourself on schedule.

- 10. When you have submitted an assignment to your tutor for marking, do not wait for its return before starting on the next unit. Keep to your schedule. When the assignment is returned, pay particular attention to your tutor's comments, both on the tutor marked assignment form and also written on the assignment. Consult you tutor as soon as possible if you have any questions or problems.

- 11. After completing the last unit, review the course and prepare yourself for the final examination. Check that you have achieved the unit objectives (listed at the beginning of each unit) and the course objectives (listed in this course guide).

# Tutors and Tutorials

There are few hours of tutorial provided in support of this course. You will be notified of the dates, time and location together with the name and phone number of your tutor as soon as you are allocated a tutorial group. Your tutor will mark and comment on your assignments, keep a close watch on your progress and on any difficulties you might encounter and provide assistance to you during the course. You must mail your tutor marked assignment to your tutor well before the due date. At least two working days are required for this purpose. They will be marked by your tutor and returned to you as soon as possible.

Do not hesitate to contact your tutor by telephone, e-mail or discussion board if you need help. The following might be circumstances in which you would find help necessary: contact your tutor if:

- You do not understand any part of the study units or the assigned readings.

- You have difficulty with the self-test or exercise.

- You have questions or problems with an assignment, with your tutor's comments on an assignment or with the grading of an assignment.

You should endeavour to attend the tutorials. This is the only opportunity to have face to face contact with your tutor and ask questions which are answered instantly. You can raise any problem encountered in the course of your study. To gain the maximum benefit from the course tutorials, have some questions handy before attending them. You will learn a lot from participating actively in discussions.

GOODLUCK!

# Table of Contents

| Course Development Team                                                       | iii   |

|-------------------------------------------------------------------------------|-------|

| Study Guide                                                                   | iv    |

| Table of Content                                                              | x     |

| Module One: Digital Logic                                                     | 1     |

| Unit 1: Fundamental Building Blocks of Digital Logic                          | 2     |

| Unit 2: Programmable Logic Array (PLA)                                        | 17    |

| Module Two: Memory Systems                                                    | 26    |

| Unit 1: Storage Systems and their Technologies                                | 27    |

| Unit 2: Data Compression and Data Integrity                                   | 34    |

| Unit 3: Memory Hierarchy, Organisation and Operations                         | 42    |

| Unit 4: Cache Memory and Virtual Memory                                       | 49    |

| Module Three: Interfacing and Communication                                   | 71    |

| Unit 1: Input/ Output Fundamentals                                            | 72    |

| Unit 2: Handshaking                                                           | 90    |

| Unit 3: Data Buffer                                                           | 98    |

| Unit 4: External Storage                                                      | 108   |

| Module Four: Introduction to Networks, RAID Architectures, Data Path & Contro | ol114 |

| Unit 1: Introduction to Networks                                              | 115   |

| Unit 2: Multimedia Support RAID Architectures                                 | 128   |

| Unit 3: Data Path and Control Unit                                            | 139   |

| Module Five: Instruction Pipelining, RISCs & Multiprocessors                  | 155   |

| Unit 1: Instruction Pipelining                                                | 156   |

| Unit 2: Introduction to Reduced Instruction Set Computers (RISCs)             | 165   |

| Unit 3: Introduction to Multiprocessors                                       | 183   |

# Module 1

# Digital Logic

### Unit 1: Fundamental Building Blocks of Digital Logic

Unit 2: Programmable Logic Array (PLA)

# Unit 1

# Fundamental Building Blocks of Digital Logic

# Contents

- 1.0 Introduction

- 2.0 Learning Outcomes

- 3.0 Learning Content

- 3.1 Boolean Algebra

- 3.2 Logic Gates

- 3.3 Combination Circuits

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

# 1.0 Introduction

In this unit, you will learn digital logic. More so, you will briefly learn about the Boolean algebra, which will be useful in the discussions on logic circuits. This unit also discuss on logic gates and combination circuits.

# 2.0 Learning Outcome

By the end of this unit, you should be able to:

- 1. Define Boolean algebra

- 2. Explain logic gates

- 3. Describe combination circuits

# 3.0 Learning Content

### 3.1 Boolean Algebra

**Boolean Algebra** (or **Boolean Logic**) is a logical calculus of truth values, developed by George Boole in the 1840s. It resembles the algebra of real numbers, but with the numeric operations of multiplication xy, addition x + y, and negation -x replaced by the respective logical operations of conjunction  $x \wedge y$ , disjunction  $x \vee y$ , and negation  $\neg x$ .

The Boolean operations are these and all other operations that can be built from these, such as  $x \land (y \lor z)$ . They turned out to coincide with the set of all operations on the set {0,1} that take only finitely many arguments; there are  $2^{2^n}$  such operations when there are *n* arguments. Is that clear.

Do you know that the laws of Boolean algebra can be defined axiomatically? As certain equations called axioms together with their logical consequences called theorems, or semantically as those equations that are true for every possible assignment of 0 or 1 to their variables. Also, the axiomatic approach is sound and complete in the sense that it proves respectively neither more nor fewer laws than the semantic approach.

You should also note that Boolean algebra is used for designing and analyzing digital circuits. First, we will discuss the rules of Boolean algebra and thereafter we will be discussing how it can be used in analyzing or designing digital circuits. Now answer the below question.

## Self-Assessment Question

1. Boolean algebra was developed by \_\_\_\_\_.

### Self-Assessment Answer

### 1. George Boole

### Point 1:

Have at the back of your mind that a variable in Boolean algebra can take only two values

1 (TRUE) or 0 (FALSE)

### Point 2:

There are three basic operations in Boolean algebra, viz:

AND, OR and NOT

(These operators will be given in capitals in this module for differentiating them from normal and, or, not, etc.) is that clear?

A AND B or A.B or AB

A OR B or A + B

NOT A or  $\neg$ A or A' or  $\overline{A}$

But how do the value of A AND B which changes with the values of A and B can be represented in tabular form, which is referred to as the "truth table". See the table below.

| Α | B | A AND B | A OR B | NOT A |

|---|---|---------|--------|-------|

| 0 | 0 | 0       | 0      | 1     |

| 0 | 1 | 0       | 1      | 1     |

| 1 | 0 | 0       | 1      | 0     |

| 1 | 1 | 1       | 1      | 0     |

In addition, three more operators have been defined for Boolean algebra: Say the below aloud.

XOR (Exclusive OR), NOR (Not OR) and NAND (Not AND)

However, if you will be designing and analyzing a logical circuit, it is convenient to use AND, NOT and OR operators. Because AND and OR obey many laws as of multiplicationion and addition in the ordinary algebra of real numbers.

**Example:** Complete the truth table below:

| А | В | A + B |

|---|---|-------|

| 0 | 0 |       |

| 0 | 1 |       |

| 1 | 0 |       |

| 1 | 1 |       |

### Solution

Remember that A + B is the same as A OR B. Therefore, your answer should be;

| А | В | A + B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

### Point 3:

The basic logical identities used in Boolean algebra are:

### **BASIC IDENTITIES**

| A.B = B.A                      | A+B = B+A                                                                              | Commutative law             |

|--------------------------------|----------------------------------------------------------------------------------------|-----------------------------|

| A.(B+C) = (A.B)+(A.C)          | $\mathbf{A}+(\mathbf{B}.\mathbf{C}) = (\mathbf{A}+\mathbf{B}).(\mathbf{A}+\mathbf{C})$ | Distributive law            |

| $1.A = A$ $A.\overline{A} = 0$ | $\begin{array}{l} 0+A=A\\ A+\bar{\textbf{A}}=1 \end{array}$                            | Identity law<br>Inverse law |

### **OTHER IDENTITIES**

| 0.A = 0                         | 1 + A = 1                       |                   |

|---------------------------------|---------------------------------|-------------------|

| A.A = A                         | A+A = A                         |                   |

| $\underline{A.(B.C)} = (A.B).C$ | $\underline{A+(B+C)} = (A+B)+C$ | Associative law   |

| $A.B = \bar{A} + B$             | $A+B = \bar{A}.B$               | Demorgan'sTheorem |

DeMorgan's law is very useful in simplifying logical expressions. Having explained the Boolean algebra, it is important you review it first before proceeding.

### **Boolean Function**:

A Boolean function is defined as an algebraic expression formed with the binary variables, the logic operation symbols, parenthesis, and equal to sign. For example,

F = A. B+C is a Boolean function.

So the value of Boolean Function F can be either 0 or 1.

A Boolean function can be broken into logic diagram and vice versa (we will discuss this in the next section). Therefore, if we code the logic operations in Boolean algebraic form and simplify this expression, we will design the simplified form of the logic circuits. Is that understood? Now answer the questions below.

### Self-Assessment Question

1. The three basic operations of Boolean algebra are \_\_\_\_\_.

### Self-Assessment Answer

1. AND, OR, NOT

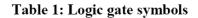

### 3.2 Logic Gates

### What is a Logic Gate?

It is an idealized or physical device implementing a Boolean function. That is, it performs a logical operation on one or more logic inputs and produces a single logic output. Depending

on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and unlimited fan-out. Or it may refer to a non-ideal physical device. Digital systems are said to be constructed by using logic gates.

You should be aware that logic gate is an electronic circuit which produces a typical output signal depending on its input signal. The output signal of a gate is a simple Boolean operation of its input signal(s). Gates are the basic logic elements. These gates are the AND, OR, NOT, NAND, NOR, EXOR and EXNOR gates. Remember your point 2? Any Boolean function can be represented in the form of gates.

Now the basic operations are described below with the aid of truth tables.

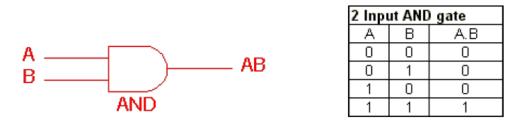

### AND gate

The AND gate is an electronic circuit that gives a **high** output (1) only if **all** its inputs are high. A dot (.) is used to show the AND operation i.e. A.B. Bear in mind that this dot is sometimes omitted i.e. AB

| 2 Input OR gate |   |     |

|-----------------|---|-----|

| А               | В | A+B |

| 0               | 0 | 0   |

| 0               | 1 | 1   |

| 1               | 0 | 1   |

| 1               | 1 | 1   |

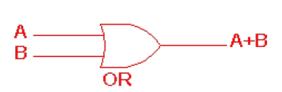

The OR gate is an electronic circuit that gives a high output (1) if **one or more** of its inputs are high. A plus (+) is used to show the OR operation.

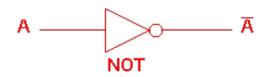

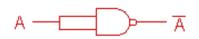

### NOT gate

| NOT gate |   |

|----------|---|

| А        | Ā |

| 0        | 1 |

| 1        | 0 |

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an inverter. Now pay attention! If your input variable is A, the inverted output is known as NOT A. This is also shown as A', or A with a bar over the top, as

shown at the outputs. The diagrams below show two ways in which the NAND logic gate can be configured to produce a NOT gate. It can also be done using NOR logic gates in the same way.

NAND gate

| 2 Input NAND gate |   |     |

|-------------------|---|-----|

| А                 | В | A.B |

| 0                 | 0 | 1   |

| 0                 | 1 | 1   |

| 1                 | 0 | 1   |

| 1                 | 1 | 0   |

This is a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if **any** of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents an inversion.

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if **any** of the inputs are high. The symbol is an OR gate with a small circle on the output. The small circle represents an inversion.

### NOR gate

| 2 Input NOR gate |   |     |  |  |  |

|------------------|---|-----|--|--|--|

| Α                | В | A+B |  |  |  |

| 0                | 0 | 1   |  |  |  |

| 0                | 1 | 0   |  |  |  |

| 1                | 0 | 0   |  |  |  |

| 1                | 1 | 0   |  |  |  |

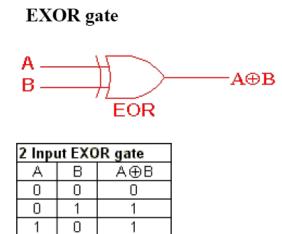

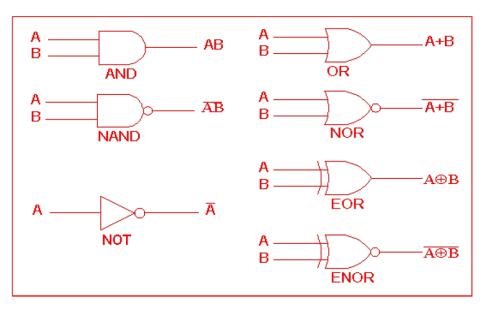

The '**Exclusive-OR**' gate is a circuit which will give a high output if **either, but not both**, of its two inputs are high. An encircled plus sign () is used to show the EOR operation.

The 'Exclusive-NOR' gate circuit does the opposite of the EOR gate. It will give a low output if either, but not both of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents an inversion. The NAND and NOR gates are called **universal functions** since with either one the AND and OR functions and NOT can be generated.

0

### **EXNOR** gate

1

1

### Note:

A function in **sum of products** form can be implemented using NAND gates by replacing all AND and OR gates by NAND gates. A function in **product of sums** form can be implemented using NOR gates by replacing all AND and OR gates by NOR gates.

Table 2 is a summary truth table of the input/output combinations for the NOT gate together with all possible input/output combinations for the

Other gate functions. Also note that a truth table with 'n' inputs has 2<sup>n</sup> rows. You can compare the outputs of different gates.

Table 2: Logic gates representation using the Truth table

|       |      | [ | INPUTS |   | OUTPUTS |      |    |     |      |       |

|-------|------|---|--------|---|---------|------|----|-----|------|-------|

|       |      | [ | А      | В | AND     | NAND | OR | NOR | EXOR | EXNOR |

| NOT g | gate | [ | 0      | 0 | 0       | 1    | 0  | 1   | 0    | 1     |

| Α     | Ā    | [ | 0      | 1 | 0       | 1    | 1  | 0   | 1    | 0     |

| 0     | 1    |   | 1      | 0 | 0       | 1    | 1  | 0   | 1    | 0     |

| 1     | 0    |   | 1      | 1 | 1       | 0    | 1  | 0   | 0    | 1     |

The truth table of NAND and NOR can be made from NOT (A AND B) and NOT (A OR B) respectively. Exclusive OR (XOR) is a special gate whose output is one only if the inputs are not equal. The inverse of exclusive OR can be a comparator which will produce a one output if two inputs are equal. Be aware that digital circuit use only one or two types of gates for simplicity in fabrication purposes. Therefore, one must think in terms of functionally complete sets of gates.

What does a functionally complete set imply? A set of gates by which any Boolean function can be implemented is called a functionally complete set. The functionally compete sets are: (AND, NOT), (NOR), (NAND), (OR< NOT) etc. Now do the exercise below.

Self-Assessment Questions(S)

- 1. What are logical gates?

- 2. List five logical gates you know.

### Self-Assessment Answer(S)

- 1. A logic gate is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logic inputs and produces a single logic output.

- 2. AND, OR, NOR, EXOR, EXNOR

### 3.3 Combination Circuits

Do you know that combinational circuits are interconnected circuits of gates according to a certain rule to produce an output depending on its input value? A well-formed combinational circuit should not have feedback loops. A combinational circuit can be represented as a network of gates and, can be expressed by a truth table or a Boolean expression.

The output of a combinational circuit is related to its input by a combinational function, which is independent of time. Therefore, for an ideal combinational circuit, the output should change according to changes in input. But in actual cases there is a slight delay. This delay is normally proportional to the depth or number of levels, i.e the maximum number of gates lying on any path from input to output.

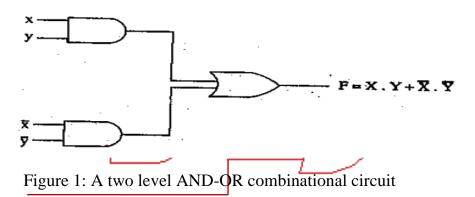

For example, the depth of the combinational circuit in figure 1 is two

**Example**: Draw the logic gates for the function F = A.B + C

### Solution:

The basic design issue related to combinational circuits is: the reduction/minimization of the number of gates. The normal circuit constraints for combinational circuit design are:

The depth of the circuit should not exceed a specific level.

i. Number of input lines to a gate (fan in) and how many gates its output can be fed (fan out) are constrained by the circuit power constraints.

### **Minimization of Gates**

The simplification of the Boolean expression is very useful for combinational circuit designs. The following three methods are used for this.

1. Algebraic simplification

- 2. Karnaugh maps

- 3. The Quine McCluskey method

But before defining any of the above stated methods let us discuss the forms of algebraic expressions. An algebraic expression can exist in two forms:

- 1. Sum of products (SOP) e.g.  $(A.\neg B) + (\neg A. \neg B)$

- 2. Product of sums (POS) e.g. (¬A +¬B).(A+B)

If a product of SOP expression contains every variable of that function either in true or complement form, then it is defined as a minterm. This minterm will be true only for one combination of input values of the variables. For example, in the SOP expression-

$$F(A, B, C) = (A.B.C) + (\neg A. \neg B.C) + (A.B)$$

We have three product terms namely A.B.C,  $\neg A$ .  $\neg B.C$  and A.B. But only the first two of them qualify to be a minterm, as the third one does not contain variable C or its complement. In addition, the term A.B.C will be one only if A=1, B=1 and C=1 for any other combination of values of A, B, C the minterm will have zero value. Similarly, the minterm  $\neg A$ .  $\neg B.C$  will have value 1 only if  $\neg A = 1$  i.e. A=0,  $\neg B=1$  i.e. B=0 and C=1.For any other combination of values the minterm will have a zero value. Ask your tutor for more explanation.

Also on the second note, a similar type of term used in POS form is called maxterm. And maxterm is a term of POS expression, which contains all the variables of the function in true or complemented form. For example,

$F(A, B, C)=(A=B=C).(\neg A+\neg B+C)$  have two maxterms. A maxterm have a value 0 for only one combination of input values. You'll agree that maxterm A+B+C will be 0 value only for A=0, B=0 and C=0. For all other combination of values of A, B, C it will have a value one.

Now let us come back to the problem of minimizing the number of gates.

### **Algebraic Simplification**

We have already discussed the algebraic simplification of a logical circuit. An algebraic expression can exist in POS or SOP forms. Okay? The algebraic functions can appear in many different forms. Although the process of simplification exists yet it is cumbersome because of the absence of routes, which tell what rule to apply next. The Karnaugh map is a simple direct approach of simplification of logical expressions.

### Karnaugh Maps

The Karnaugh map is a convenient way of representing and simplifying Boolean functions of 4 to 6 variables. Karnaugh maps can also be used for designing the circuits in situations where you can construct the truth table for an operation or a function. In other words, Karnaugh maps can be used to construct a circuit when the input and output to that proposed circuit are defined. For each output one Karnaugh map needs to be constructed. The stepwise procedure for Karnaugh map is as follows:

### Step 1

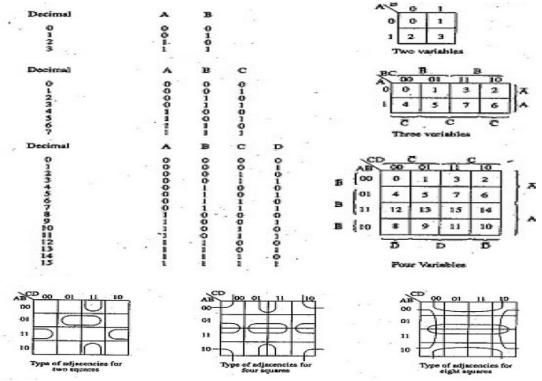

Create a simple map depending on the number of variables in the function. Figure 2 shows the map of two, three and four variables. A map of 2 variables contains 4 value positions or elements, while for 3 variables it has  $2^3$ =8 elements; similarly, for 4 variables it is  $2^4$ =16

elements and so on. Special care is taken to represent variables in the map. Value of only one variable changes in two adjacent columns or rows.

The advantage of having a change in one variable is that two adjacent columns or rows represent a true form or complement form of a single variable. For example, in Figure 2 the columns which have positive A are adjacent to  $\neg A$ . Please note the adjacency of the corners. The rightmost column can be considered to be adjacent to the first column; since they differ only by one variable, therefore, they are adjacent. Similarly, the topmost and bottommost rows are adjacent.

Figure 2: Maps of two, three and four variables and their adjacencies

### Note the following:

- 1. Decimal equivalents of the cells are given for help in understanding where the position of the respective decimal equivalent is. It is not the value filled in a square. A square can contain one or nothing.

- 2. The 00, 01, 11 etc. written on the top implies the value of respective variables.

- 3. Wherever the value of a variable is zero it is said to represent its complement form.

- 4. The value of only one variable changes when we move from one row to the next row or from one column to the next column.

### Step 2:

The next step in the Karnaugh map is to map the truth table into the map. The mapping is done by putting a 1 in the respective squares belonging to the 1 value in the truth table. This mapped map is used to arrive at simplified Boolean expressions, which then can be used for drawing up the optimal logical circuits. Step 2 will be clearer in the example.

### Step 3:

Now create simple algebraic expressions from the Karnaugh map. These expressions are created by using adjacency if we have two adjacent 1's then the expressions for those can be simplified together since they differ in only one variable. Similarly, we search for adjacent pairs of four, eight, and so on. A 1 can appear in more than one adjacent pairs. You must find adjacencies till all 1's in the Karnaugh map are covered. The following example will clarify step 3.

**Example 2:** Now let us see how to use Karnaugh map simplification for finding the Boolean function for the cases whose truth table is given as:

| Α |   | В |   | С |   | D | Decimal<br>Equivalent | Output F |

|---|---|---|---|---|---|---|-----------------------|----------|

| 0 |   | 0 |   | 0 |   | 0 | 0                     | 1        |

| 0 |   | 0 |   | 0 |   | 1 | 1                     | 1        |

| 0 |   | 0 |   | 1 |   | 0 | 2                     | 1        |

| 0 |   | 0 |   | 1 |   | 1 | 3                     | 0        |

| 0 |   | 1 |   | 0 |   | 0 | 4                     | 0        |

| 0 | 1 |   | 0 |   | 1 |   | 5                     | 0        |

| 0 | 1 |   | 1 |   | 0 |   | 6                     | 1        |

| 0 | 1 |   | 1 |   | 1 |   | 7                     | 0        |

| 1 | 0 |   | 0 |   | 0 |   | 8                     | 1        |

| 1 | 0 |   | 0 |   | 1 |   | 9                     | 1        |

| 1 | 0 |   | 1 |   | 0 |   | 10                    | 1        |

| 1 | 0 |   | 1 |   | 1 |   | 11                    | 0        |

| 1 | 1 |   | 0 |   | 0 |   | 12                    | 0        |

| 1 | 1 |   | 0 |   | 1 |   | 13                    | 0        |

| 1 | 1 |   | 1 |   | 0 |   | 14                    | 0        |

| 1 | 1 |   | 1 |   | 1 |   | 15                    | 0        |

Another short representation of the truth table is  $\Sigma(0,1,2,6,8,9,10)$  which indicate the decimal equivalent for A, B, C, D values for which the output is one.

Let us construct the Karnaugh map for this.

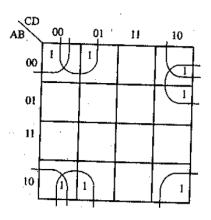

Figure 3: Karnaugh's map of the truth table of example 2

Let us see the pairs which can be considered adjacent in the Karnaugh map here.

The pairs are

- 1. The four corners

- 2. The four 1's as in top and bottom in columns 1 and 2

- 3. The two 1's in the top two rows of the last column.

The corners can be represented by the expressions:

1.

$$(\neg A \neg B \neg C \neg D + \neg A \neg BC \neg D) + (A \neg B \neg C \neg D + A \neg BC \neg D)$$

$= \neg A . \neg B . \neg D(\neg C + C) + A . \neg B . \neg D(\neg C + C)$

$= \neg A \neg B \neg D + A \neg B \neg D$  as  $(\neg C + C) = 1$

$= \neg B \neg D$   $(\neg A + A)$

$= \neg B \neg D$  as  $(\neg A + A) = 1$

2. The four 1's give the following term:

$$(\neg A \neg B \neg C \neg D + \neg A \neg B \neg C.D) + (A \neg B \neg C \neg D + A \neg B \neg CD) = \neg A \neg B \neg C (\neg D + D) + A \neg B \neg C (\neg D + D) = \neg A \neg B \neg C + A \neg B \neg C (\neg D + D) = \neg B \neg C (\neg A + A) = \neg B \neg C$$

as  $(\neg A + A) = 1$

3. The two 1's in the last column

$$\neg A \neg B C \neg D + \neg A B C \neg D$$

=  $\neg A C \neg D (\neg B + B)$

=  $\neg A C \neg D$  as  $(\neg B + B) = 1$

Thus, the Boolean expression derived from this Karnaugh map is

$$F = \neg B \neg D + \neg B \neg C + \neg A C \neg D$$

The expressions so obtained through the Karnaugh map are in the form of the sum of the product form, i.e. it is expressed as a sum of the products of the variables. The expression is one of the minimal solutions. This expression can be expressed in product of the sum form, but for this, special methods need to be used.

Let us see how we can modify the Karnaugh map simplification to obtain the product of the sum form. Suppose in the previous example instead of using 1's we combine the adjacent zero square then we will obtain the inverse function and on taking NOT of this function we will get the product of sum form (the use of DeMorgan's theorem will be required).

Another important aspect of this simple method of digital circuit design is DONOT care conditions. These conditions further simplify the algebraic function. These conditions imply that it does not matter whether the output produced is zero or 1 for a specific input. These conditions can occur when the combination of the number of inputs are more than needed; e.g., calculation through BCD where 4 bits are used to represent a decimal digit, which implies we can represent  $2^4 = 16$  digits but since we have only 10 decimal digits, therefore, 6 of those input combinations do not matter and thus, are a candidate for DONOT care condition.

What will happen if we have more than 4-6 variables? As the number of the variables increases the Karnaugh map becomes more and more cumbersome (as the number of possible combination of inputs keeps on increasing). A method was suggested to deal with the increasing number of variables. This is a tabular approach and is known as the Quine-Mckluskey method.

Know that this method is suitable for programming and hence provides a tool for automating designs in the form of minimized Boolean expressions. The basic principle behind the Quine-Mckluskey method is to remove the terms which are redundant and can be obtained by other terms.

### Self-Assessment Question

1. List three methods that have been used to minimize the use of Gates.

### Self-Assessment Answer

The following three methods are used for this.

- 1. Algebraic simplification

- 2. Karnaugh maps

- 3. The Quine McCluskey method

# 4.0 Conclusion

In this unit, I want to believe you have learnt about the digital logic. You have also learnt about the Boolean algebra, which is the basis for discussions on logic circuits. You also learnt in this unit the logic gates and combination circuits.

## 5.0 Summary

We have discussed that Boolean algebra is an attempt to represent the true-false logic of humans in mathematical form. George Boole proposed the principles of the Boolean algebra in 1854, hence the name Boolean algebra. Do not forget that Boolean algebra is used for designing and analyzing digital circuits. And its function is defined as an algebraic expression formed with the binary variables, the logic operation symbols, parenthesis, and equal to sign.

More so, digital systems are said to be constructed by using logic gates. A logic gate is an electronic circuit which produces a typical output signal depending on its input signal. Also, combinational circuits are interconnected circuits of gates according to a certain rule to produce an output depending on its input value.

And lastly, remember that well-formed combinational circuit should not have feedback loops. A combinational circuit can be represented as a network of gates and, can be expressed by a truth table or a Boolean expression.

# 6.0 Tutor-Marked Assignment

- 1. Explain logic gates with AND gate and OR gate as examples?

- 2. Explain sum of products and product of sums?

# 7.0 References/Further Reading

- 1. Baron, Robert J. and Higbie Lee. *Computer Architecture*. Addison-Wesley Publishing Company.

- 2. Daniel P, and David G, (2009). A Practical Introduction to Computer Architecture. Text in Computer Science, Springer Dordrecht Heidelberg London New York.

- Flautner, K. Kim, N.S. Martin, S. Blaauw D. and Mudge, T.N. Drowsy Caches: Simple Techniques for Reducing Leakage Power. In *International Symposium on Computer Architecture. (ISCA)*, 148–157, 2002

- 4. Hayes, John P. (1998). *Computer Architecture and Organisation* (2nd ed). McGraw-Hill International editions.

- 5. Hennessy J.L and Patterson, D.A. *Computer Architecture: A Quantitative Approach*, Morgan Kaufmann, 2006. ISBN: 0-123-70490-1.

- 6. Mano, M. Morris, (1993). Computer System Architecture (3rd ed). Prentice Hall of India.

- 7. Miles J, and Vincent P. H. (1999). Principle of Computer Architecture Class Test Edition, August 1999. http://www.cs.rutgers.edu/~murdocca/

- 8. http://ece-www.colorado.edu/faculty/heuring.html

- 9. Mostafa A. E.B and Hesham E. R, (2005). Fundamentals of Computer Organization and Architecture. Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

- NOUN, (2008). INTRODUCTION TO COMPUTER ORGANISATION. CIT 246 Course Material, National Open University of Nigeria, Headquarters 14/16 Ahmadu Bello Way, Victoria Island, Lagos. First Printed 2008

- 11. Stallings William. *Computer Organisation and Architecture* (3rd ed). Maxwell Macmillan International Editions.

- 12. Tanenbaum, Andrew S. (1993). *Structural Computer Organisation* (3<sup>rd</sup> ed) Prentice Hall of India.

- 13. http://websrv.cs.fsu.edu/~tyson/CDA5155/refs.html

- 14. http://www.cs.ucsd.edu/classes/wi99/cse141\_B/lectures.html

- 15. http://www.cs.caltech.edu/courses/cs184/ winter2001/slides/day5\_2up.pdf

- 16. http://www.cs.iastate.edu/~prabhu/Tutorial/PIPELINE/compSched.html

- 17. http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/

# Unit 2

# Programmable Logic Array (PLA)

# Contents

- 1.0 Introduction

- 2.0 Learning Outcomes

- 3.0 Learning Content

- 3.1 Programmable Logic Array

- 3.2 What Is a Flip-Flop?

- 3.3 Registers

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

# 1.0 Introduction

In this unit, what you will learn is about programmable logic array (PLA). One way to design a combinational logic circuit is that you get gates and connect them with wires. One disadvantage with this way of designing circuits is its lack of portability. You will also learn about Programmable Logic Array (PLA), definition of a Flip-Flop, and registers.

# 2.0 Learning Outcome

By the end of this unit, you should be able to:

- 1. Explain programmable logic array (PLA)

- 2. Define a flip-flop

- 3. Describe registers

## 3.0 Learning Content

### 3.1 Programmable Logic Array

You should know that the individual gates are treated as basic building blocks from which various logic functions can be derived before now. You have also learnt about the strategies of minimization of number of gates in the previous unit. But with the advancement of technology, the integration provided by integrated circuit technology has increased resulting in the production of one to ten gates on a single chip (in Small Scale Integration (SSI)).

The gate level designs are constructed at the gate level only. But if the design is to be done using these SSI chips, the design consideration needs to be changed as a number of such SSI chips may be used for developing a logic circuit. With MSI & VLSI we can put even more gates on a chip and can also make gate interconnections on a chip. These integration and connection bring the advantages of decreased cost, size, and increased speed.

Note that the basic drawback faced in such VLSI & MSI chips is that for each logic function the layout of gates and interconnection need to be designed. The cost involved in making such a custom chip design is quite high. This brings us to the concept of Programamble Logic Array (PLA), a general-purpose chip that can be readily adopted for any specific purpose. The PLA are designed for SOP form of Boolean function and consist of a regular arrangement of NOT, AND & OR gates on a chip.

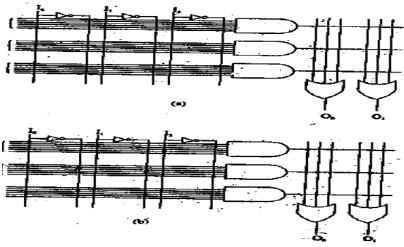

Each input to the chip is passed through a NOT gate, thus, the input and their complement are available to each AND gate. The output of each AND gate is made available for each OR gate. And the output of each OR gate is treated as chip output. By making appropriate connections, any logic function can be implemented in these Programmable Logic Arrays. Now take a close look at the below diagram.

Figure 1: Programmable Logic Array

The figure 1(a) shows a PLA of three inputs and two outputs. Please note the connectivity points, as all these points can be connected if desired. Figure 1(b) shows an implementation of logic function:

# $O_0 = I_0, I_1, I_2 + \neg I_0 \neg I_1 \neg I_2 \text{ and } O_1 = \neg I_0 \neg I_1 \neg I_2 + \neg I_0. \neg I_1$

Please note the second function is a non-optimal function and can be simplified using Boolean algebra.

### Self-Assessment Question

1. What is a Programmable Logical Array?

### Self-Assessment Answer

1. Programmable Logic Array (PLA) is a general-purpose chip that can be readily adopted for any specific purpose.

### 3.2 What is a Flip-Flop?

A flip-flop is a binary cell, which can store a bit of information and which in itself is a step-tostep circuit. But, how does it happen? A flip-flop maintains any one of the two stable states that can be treated as zero or one depending on the presence and absence of output signals. This state of a flip-flop can only change when a clock pulse has arrived. First see the basic flip-flop or a latch that was a revolutionary step in computers. The basic latch presented here is not in order. Let us see its logic diagram (Figure 2).

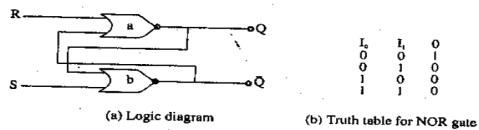

Figure 2: A Basic latch (S-R latch using NOR gates)

You can construct a flip-flop using two NAND or NOR gates; which contains a feedback loop. The flip-flop you saw in the above figure has two inputs R (Reset) and S (set) and two outputs Q and  $\neg Q$ . In a normal mode of operation both the flip-flop inputs are at zero i.e. S = 0 & R = 0. This means that the flip-flop can show two states: either the value Q is 1 (therefore  $\neg Q = 0$ ). we say the flip-flop is in set state or the value of Q is 0 (therefore  $\neg Q = 1$ ) we call it a clear state. Do you understand?

Now let's take this example: Draw the truth table for A flip-flop NAND gate

Solution:

The first thing is to find the AND then the NOT as shown in the table below

| I <sub>0</sub> | l <sub>1</sub> | NAND |

|----------------|----------------|------|

| 0              | 0              | 1    |

| 0              | 1              | 1    |

| 1              | 0              | 1    |

| 1              | 1              | 0    |

Let us see how the S and R input can be used to set and clear the state of the flip-flop.

The first question you should ask yourself is, why in normal cases S and R are zero? The reason is that this state does not cause any change in state. Suppose the flip-flop was in set state i.e. Q = 1 and  $\neg Q = 0$  and as S = 0 and R = 0, the output of 'a' NOR gate will be 1 since both its input  $\neg Q$  and R are zero (refer to the truth table of 1 NOR gate in Figure 2) and 'b' NOR gate will show output as 0 as one of its input Q is 1. Similarly, if flip-flop was in clear state then  $\neg Q = 1$  and R = 0, therefore, output of 'a' gate will be 0 and 'b' gate 1. Thus, flip-flop maintains a stable state at S = 0 and R = 0.

Now the flip-flop is taken to set state if the S input quickly goes to 1 and then goes back to 0. R remains at zero during this time. What happens if, say initially, the flip-flop was in state 0 i.e. the value of Q was 0. As soon as S becomes 1 the output of NOR gate 'b' goes to 0 i.e.  $\neg$ Q becomes 0 and almost immediately Q becomes 1 as both the input ( $\neg$ Q and R) to NOR gate 'a' become 0.

You see, change in the value of S back to 0 does not change the value of Q again as the input to NOR gate 'b' now are Q = 1 and S = 0. As a result, the flip-flop stays in the set state even after S returns to zero. If the flip-flop was in state 1 then, when S goes to 1 there is no change in value of  $\neg$ Q as both the inputs to NOR gate 'b' are 1 at this time. Thus,  $\neg$ Q remains in state 0 or in other words flip-flop stays in the set state.

But R input goes to value 1 then flip-flop acquires the clear state. On changing for a short time, the value of R to 1 the Q output changes to 0 irrespective of the state of flip-flop and as Q is 0 and S is 0 the  $\neg$ Q becomes 1. Even after R comes back to value 0, Q remains 0 i.e., flip flop comes to the clear state.

Now, anybody can ask you that what will happen when both S and R go to 1 at the same time. Well, you should be able to say that this is the situation which may create a set or clear state depending on which of the S and R stays longer in zero state. But meanwhile both of them are 1 and the value of Q and  $\neg$ Q becomes 1 which implies that both Q and its complement are one, an impossible situation. Therefore, the transition of both S and R to 1 at the same time is an undesirable condition for this basic latch. Let us try to construct a synchronous R-S flip-flop form the basic latch. The clock pulse will be used to synchronize the flip-flop. (What is a clock pulse?).

Self-Assessment Question

1. What is a Flip Flop?

### Self-Assessment Answer

1. A flip-flop is a binary cell, which can store a bit of information and which in itself is a sequential circuit.

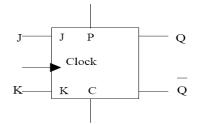

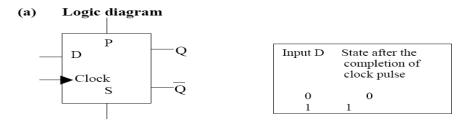

### 3.2.1 D Flip-Flop

D flip-flop is a special type of flip-flop in the sense that it represents the currently applied input as the state of the flip-flop. Thus, in effect it can store 1 bit of data information and is sometimes referred to as Data flip-flop. Please note that the state of the flip-flop changes for the applied input. It does not have a condition where the state does not change as the case in RS flip-flop, the state of R-S flip-flop does not change when S = 0 and R = 0.

If we do not want a particular input state to change, then either the clock is to be disabled during that period or a feedback of the output can be embedded with the input D. Do not forget that D flip-flop is also referred to as Delay flip-flop because it delays the 0 or 1 applied to its input by a single clock pulse.

| Input State at the completi | State at the completion |  |  |  |  |

|-----------------------------|-------------------------|--|--|--|--|

| J K of clock cycle          |                         |  |  |  |  |

|                             |                         |  |  |  |  |

| 0 0 No change in State      |                         |  |  |  |  |

| 0 1 Clear the flip-flop (s  | state 0)                |  |  |  |  |

1 0 Set the flip-flop (state 1)

1 Complement the state of flip-flop

(b) Symbolic representation

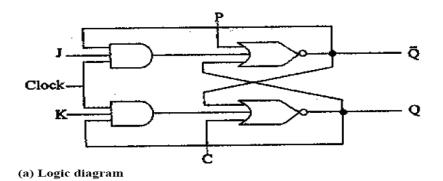

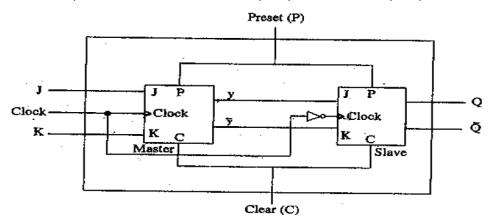

### J-K flip-flop

(c) Characteristic table

1

(b) Symbolic representation (c) Characteristic table D flip-flop

Figure 3: Other flip-flops

### 3.2.2 J K flip-flop

The basic drawback with the R S flip-flop is that one set of input conditions are not utilized and this can be used with a little change in the circuit. In this flip-flop, the last combination is used to complement the state of the flip-flop. After discussing some of the simple sequential circuits, that is flip-flop, let us discuss some of the complex sequential circuits, which can be developed using simple gates, and flip-flops.

### Self-Assessment Question

1. List two (2) types of Flip-Flops you know.

### Self-Assessment Answer

### 1. D-Flip-Flop and JK Flip-Flop

### 3.3 Registers

A register is a binary function which holds the binary information in digital form. Thus, a register consists of a group of binary storage cells. A register consists of one and more flip-flops depending on the number of bits to be stored in a word. A separate flip-flop is used for storing a bit of a word. In addition to storage, registers are normally coupled with combinational gates enabling certain data processing tasks.

Thus, a register in a broad sense consists of the flip-flop that stores binary information and gates, which controls when and how information is transferred to the register. Normally in a register you will notice that independent data lines are provided for each flip-flop, enabling the transfer of data to and from all flip-flops to the register simultaneously.

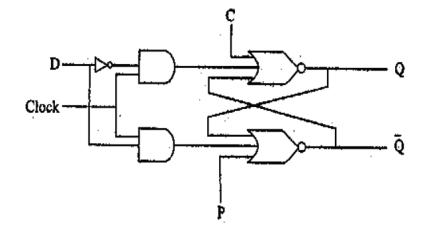

I want you to know that this mode of operation is called Parallel Input-Output. Since the stored information in a set of flip-flops is treated as a single entity, common control signals such as clock, preset and clear can be used for all the flip-flops of the register. Registers can be constructed from any type of flip-flop. These flip-flops in integrated circuit registers are usually constructed internally using two separate flip-flop circuits. The normally used special kind of arrangement is termed the master slave flip-flop. This type of flip-flop helps in having a stable state at the output. It consists of a master flip-flop and a slave flip-flop.

Figure 4: Masters-slave flip-flop using J-K flip-flop

**Note:** You can construct master-slave flip-flop with D flip-flop (Figure 4) or R-S flip-flop in the same manner.

Now, let us analyze this flip-flop.

When the clock pulse is 0 the master is disabled but the slave becomes active and its output Q and ¬Q becomes equal to Y and ¬Y respectively. Why? Well, the possible combination of the value of Y and ¬Y are either Y = 1 which means ¬Y = 0; or Y = 0 which implies ¬Y = 1. Let us see the characteristic table for these two inputs for the J-K flip-flop. The SLAVE flip-flop,

Thus, it can have value either J=1 and K=0 which will set the flip-flop that is Q=1 and  $\neg$ Q=0; or J=0, K=1 which will clear the flip-flop. Therefore, Q is same as Y.

2. When inputs are applied at J and K and the clock pulse becomes 1, only the master gets activated, resulting in intermediate output Y go to state 0 or 1 depending on the input and previous state. Please note that during this time the slave is still maintaining its previous state. As the clock pulse become 0, the master becomes inactive and the slave acquires the same state as the master.

But why do we acquire this master-slave combination? There is a major reason for this master-slave form. Consider a situation where the output of a flip-flop is going to input of other flip-flops. Here, the assumption is that the clock pulse inputs of all flip-flops are synchronized and occur at the same time.

The change of state of the master occurs when the clock pulse goes to 1, but during that time the output of the slave still has not changed, thus the state of the flip-flops in the system can be changed simultaneously during the same clock pulse even though outputs of flipflops are connected to the inputs of flip-flops. In other words, there are no restrictions on feedback from the register's outputs to its inputs.

### Self-Assessment Questions

1. What is the mode of operation of a register?

### Self-Assessment Answer(s)

1. Parallel Input-Output.

### 4.0 Conclusion

In this unit, you have learned about the programmable logic array (PLA). You have also learnt about definition of a Flip-Flop and registers.

## 5.0 Summary

The individual gates are treated as basic building blocks from which various logic functions can be derived before now. You have also learnt about the strategies of minimization of number of gates. But with the advancement of technology the integration provided by integrated circuit technology has increased resulting in the production of one to ten gates on a single chip (in Small Scale Integration (SSI)).

A flip-flop is a binary cell, which can store a bit of information and which in itself is a sequential circuit. But, how does it do it? A flip-flop maintains any one of the two stable states that can be treated as zero or one depending on the presence and absence of output signals. The state of a flip-flop can only change when a clock pulse has arrived. D flip-flop is a special type of flip-flop in the sense that it represents the currently applied input as the state of the flip-flop.

Thus, in effect it can store 1 bit of data information and is sometimes referred to as Data flipflop. A register is a binary function which holds the binary information in digital form. Thus, a register consists of a group of binary storage cells. A register consists of one and more flipflops depending on the number of bits to be stored in a word.

### 6.0 Tutor-Marked Assignment

- 1. With the aid of a diagram describe a flip-flop?

- 2. Define a register?

# 7.0 References/Further Reading

- Baron, Robert J. and Higbie Lee. Computer Architecture. Addison-Wesley Publishing Company.

- Daniel P, and David G, (2009). A Practical Introduction to Computer Architecture. Text in Computer Science, Springer Dordrecht Heidelberg London New York.

- Flautner, K. Kim, N.S. Martin, S. Blaauw D. and Mudge, T.N. Drowsy Caches: Simple Techniques for Reducing Leakage Power. In *International Symposium on Computer Architecture. (ISCA)*, 148–157, 2002

- Hayes, John P. (1998). Computer Architecture and Organisation (2nd ed). McGraw-Hill International editions.

- Hennessy J.L and Patterson, D.A. *Computer Architecture: A Quantitative Approach*, Morgan Kaufmann, 2006. ISBN: 0-123-70490-1.

- Mano, M. Morris, (1993). Computer System Architecture (3rd ed). Prentice Hall of India.

- Miles J, and Vincent P. H. (1999). Principle of Computer Architecture Class Test Edition, August 1999. http://www.cs.rutgers.edu/~murdocca/

- http://ece-www.colorado.edu/faculty/heuring.html

- Mostafa A. E.B and Hesham E. R, (2005). Fundamentals of Computer Organization and Architecture. Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

- NOUN, (2008). Introduction To Computer Organisation. CIT 246 Course Material, National Open University of Nigeria, Headquarters 14/16 Ahmadu Bello Way, Victoria Island,Lagos. First Printed 2008

- Stallings William. Computer Organisation and Architecture (3rd ed). Maxwell Macmillan International Editions.

- Tanenbaum, Andrew S. (1993). *Structural Computer Organisation* (3<sup>rd</sup> ed) Prentice Hall of India.

- http://websrv.cs.fsu.edu/~tyson/CDA5155/refs.html

http://www.cs.ucsd.edu/classes/wi99/cse141\_B/lectures.html

- http://www.cs.caltech.edu/courses/cs184/ winter2001/slides/day5\_2up.pdf

- http://www.cs.iastate.edu/~prabhu/Tutorial/PIPELINE/compSched.html

- http://www.mmdb.ece.ucsb.edu/~ece154/lecture5.pdf

- http://ocw.mit.edu/courses/electrical-engineering-and-computer-science/

## Module 2

## Memory Systems

- Unit 1: Storage Systems and Their Technology

- Unit 2: Data Compression and Data Integrity

- Unit 3: Memory Hierarchy, Organization and Operations

- Unit 4: Cache Memories and Virtual Memory

## Unit 1

### Storage Systems and Their Technologies

#### Contents

- 1.0 Introduction

- 2.0 Learning Outcomes

- 3.0 Learning Content

- 3.1 Computer Data Storage

- 3.2 Fundamental Storage Technologies

- 3.3 Related Technologies

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

#### 1.0 Introduction

In this unit, what you will learn borders on storage systems and their technologies. Computer data storage, often called storage or memory. It is a technology consisting of computer components and recording media used to retain digital data. It is also a core function and fundamental component of computers. Yes, you will also learn in this unit about fundamental storage technologies and related technologies.

#### 2.0 Learning Outcome

By the end of this unit, you should be able to:

- i. Define computer data storage

- ii. Explain semiconductor

- iii. Describe magnetic storage

- iv. Explain optical storage

- v. Explain related technologies

#### 3.0 Learning Content

#### 3.1 Computer Data Storage

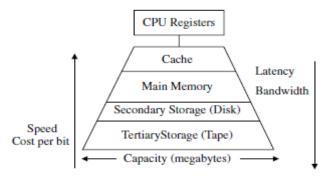

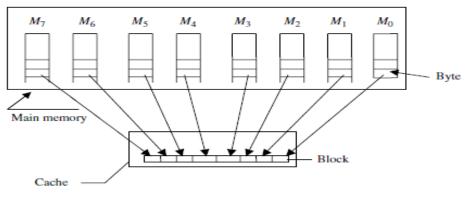

Put at the back of your mind that computer data storage often called storage or memory is a technology consisting of computer components and recording media used to retain digital data. As said earlier, it is a core function and fundamental component of computers. In present-day usage, memory is usually semiconductor storage read-write random-access memory, typically DRAM (Dynamic-RAM) or other forms of fast but temporary storage.

Storage consists of storage devices and their media not directly accessible by the CPU, (secondary or tertiary storage), typically hard disk drives, optical disc drives, and other devices slower than RAM but are non-volatile (retaining contents when powered down). Historically, *memory* has been called *core*, *main memory*, *real storage* or *internal memory* while storage devices have been referred to as secondary storage, external memory or auxiliary/peripheral storage.

The distinctions are fundamental to the architecture of computers. The distinctions also reflect an important and significant technical difference between memory and mass storage devices, which has been blurred by the historical usage of the term *storage*. Nevertheless, this article uses the traditional nomenclature. Many different forms of storage, based on various natural occurrences, have been invented.

So far, no practical universal storage medium exists, and all forms of storage have some drawbacks. Therefore, a computer system usually contains several kinds of storage, each with an individual purpose. You may have heard that the modern digital computer represents data using the binary numeral system. Text, numbers, pictures, audio, and nearly any other form of information can be converted into a string of bits, or binary digits, each of which has a value of 1 or 0.

However, the most common unit of storage is the byte, equal to 8 bits. A piece of information can be handled by any computer or device whose storage space is large enough to accommodate *the binary representation of the piece of information*, or simply data. For example, the complete works of Shakespeare, about 1250 pages in print, can be stored in about five megabytes (forty million bits) with one byte per character.

#### Self-Assessment Question

#### 1. What is Computer Data Storage?

#### Self-Assessment Answer

1. Computer data storage often called storage or memory is a technology consisting of computer components and recording media used to retain digital data

#### 3.2 Fundamental Storage Technologies

Let me say that as of 2011[update], the most commonly used data storage technologies are semiconductor, magnetic, and optical, while paper still sees some limited usage. *Media* is a common name for what actually holds the data in the storage device. Some other fundamental storage technologies have also been used in the past or are proposed for development.

#### Semiconductor

Do you know that a semiconductor memory uses semiconductor-based integrated circuits to store information? A semiconductor memory chip may contain millions of tiny transistors or capacitors. Both *volatile* and *non-volatile* forms of semiconductor memory exist. In modern computers, primary storage almost exclusively consists of dynamic volatile semiconductor memory or dynamic random access memory.

Since the turn of the century, a type of non-volatile semiconductor memory known as flash memory has steadily gained share as off-line storage for home computers. Non-volatile semiconductor memory is also used for secondary storage in various advanced electronic devices and specialized computers.

I want you to know that as early as 2006, notebook and desktop computer manufacturers started using flash-based solid-state drives (SSDs) as default configuration options for the secondary storage either in addition to or instead of the more traditional HDD.

#### **Magnetic Storage**

Magnetic storage uses different patterns of magnetization on a magnetically coated surface to store information. Its storage is *non-volatile*. The information is accessed using one or more read/write heads which may contain one or more recording transducers. A read/write head only covers a part of the surface so that the head or medium or both must be moved relative to another in order to access data. In modern computers, magnetic storage will take these forms:

#### 1. Magnetic disk

Floppy disk, used for off-line storage

Hard disk drive, used for secondary storage

2 Magnetic tape, used for tertiary and off-line storage

Know that in early computers, magnetic storage was also used as:

- 1. Primary storage in a form of magnetic memory, or core memory, core rope memory, thin-film memory and/or twist or memory.

- 2. Tertiary (e.g. NCR CRAM) or off line storage in the form of magnetic cards.

- 3. Magnetic tape was then often used for secondary storage.

#### **Optical Storage**

Optical storage, the typical optical disc, stores information in deformities on the surface of a circular disc and reads this information by illuminating the surface with a laser diode and observing the reflection. Optical disc storage is *non-volatile*. The deformities may be permanent (read only media), formed once (write once media) or reversible (recordable or read/write media). The following forms are currently in common use:

- 1. CD, CD-ROM, DVD, BD-ROM: Read only storage, used for mass distribution of digital information (music, video, computer programs)

- 2. CD-R, DVD-R, DVD+R, BD-R: Write once storage, used for tertiary and off-line storage

- 3. CD-RW, DVD-RW, DVD+RW, DVD-RAM, BD-RE: Slow write, fast read storage, used for tertiary and off-line storage

- 4. Ultra-Density Optical or UDO is similar in capacity to BD-R or BD-RE and is slow write, fast read storage used for tertiary and off-line storage.

#### Example:

If I ask you what forms is the magnetic storage in modern computers?

#### Answer:

All I want to see is in modern computers, magnetic storage will take these forms:

- 1. Magnetic disk

- Floppy disk, used for off-line storage

- Hard disk drive, used for secondary storage

- 2. Magnetic tape, used for tertiary and off-line storage

Magneto-optical disc storage is optical disc storage where the magnetic state on a ferromagnetic surface stores information. The information is read optically and written by combining magnetic and optical methods. Magneto-optical disc storage is *non-volatile*, *sequential access*, slow write, fast read storage used for tertiary and off-line storage. 3D optical data storage has also been proposed.

#### Self-Assessment Question(s)

1. List three computer storage technologies you know.

#### Self-Assessment Answer

1. Semiconductor, Magnetic Storage, Optical Storage

#### 3.3 Related Technologies

#### **Network Connectivity**

You will also learn that a secondary or tertiary storage may connect to a computer utilizing computer networks. This concept does not pertain to the primary storage, which is shared between multiple processors in a much lesser degree.

- 1. Direct-attached storage (DAS) is a traditional mass storage that does not use any network. This is still a most popular approach. This retronym was coined recently, together with NAS and SAN.

- Network-attached storage (NAS) is mass storage attached to a computer which another computer can access at file level over a local area network, a private wide area network, or in the case of online file storage, over the Internet. NAS is commonly associated with the NFS and CIFS/SMB protocols.

- 3. Storage area network (SAN) is a specialized network that provides other computers with storage capacity. The crucial difference between NAS and SAN is the former presents and manages file systems to client computers, whilst the latter provides access at blockaddressing (raw) level, leaving it to attaching systems to manage data or file systems within the provided capacity. SAN is commonly associated with Fibre Channel networks.

#### **Robotic Storage**

Large quantities of individual magnetic tapes, and optical or magneto-optical discs may be stored in robotic tertiary storage devices. In tape storage field they are known as tape libraries, and in optical storage field optical jukeboxes, or optical disk libraries per analogy. Smallest forms of either technology containing just one drive device are referred to as autoloaders or auto-changers.

Robotic-access storage devices may have a number of slots, each holding individual media, and usually one or more picking robots that traverse the slots and load media to built-in drives. The arrangement of the slots and picking devices affects performance. Important characteristics of such storage are possible expansion options: adding slots, modules, drives, robots. Tape libraries may have from 10 to more than 100,000 slots, and provide terabytes or petabytes of near-line information. Optical jukeboxes are somewhat smaller solutions, up to 1,000 slots.

Robotic storage is used for backups, and for high-capacity archives in imaging, medical, and video industries. Hierarchical storage management is a most known archiving strategy of automatically *migrating* long-unused files from fast hard disk storage to libraries or jukeboxes. If the files are needed, they are *retrieved* back to disk.

#### 4.0 Conclusion

In this unit, you have learned about the storage systems and their technologies. You have also learnt about computer data storage, often called storage or memory, fundamental storage technologies and related technologies.

#### 5.0 Summary

Computer data storage often called storage or memory is a technology consisting of computer components and recording media used to retain digital data. It is a core function and fundamental component of computers. As of 2011, the most commonly used data storage technologies are semiconductor, magnetic, and optical, while paper still sees some limited usage.

*Media* is a common Semiconductor memory uses semiconductor-based integrated circuits to store information. A semiconductor memory chip may contain millions of tiny transistors or capacitors. Both *volatile* and *non-volatile* forms of semiconductor memory exist. Magnetic storage uses different patterns of magnetization on a magnetically coated surface to store information. Magnetic storage is *non-volatile*.

The information is accessed using one or more read/write heads which may contain one or more recording transducers. Optical storage, the typical optical disc, stores information in deformities on the surface of a circular disc and reads this information by illuminating the surface with a laser diode and observing the reflection. Optical disc storage is *non-volatile*. A secondary or tertiary storage may connect to a computer utilizing computer networks.

This concept does not pertain to the primary storage, which is shared between multiple processors in a much lesser degree. Large quantities of individual magnetic tapes, and optical or magneto-optical discs may be stored in robotic tertiary storage devices.

#### 6.0 Tutor-Marked Assignment

- i. Explain how a modern digital computer presents data?

- ii. Describe magnetic storage with their forms?

#### 7.0 References/Further Reading

- Baron, Robert J. and Higbie Lee. *Computer Architecture*. Addison-Wesley Publishing Company.

- Daniel P, and David G, (2009). A Practical Introduction to Computer Architecture. Text in Computer Science, Springer Dordrecht Heidelberg London New York.

- Flautner, K. Kim, N.S. Martin, S. Blaauw D. and Mudge, T.N. Drowsy Caches: Simple Techniques for Reducing Leakage Power. In *International Symposium on Computer Architecture. (ISCA)*, 148–157, 2002

- Hayes, John P. (1998). Computer Architecture and Organisation (2nd ed). McGraw-Hill International editions.

- Hennessy J.L and Patterson, D.A. *Computer Architecture: A Quantitative Approach*, Morgan Kaufmann, 2006. ISBN: 0-123-70490-1.

Mano, M. Morris, (1993). Computer System Architecture (3rd ed). Prentice Hall of India.

- Miles J, and Vincent P. H. (1999). Principle of Computer Architecture Class Test Edition, August 1999. http://www.cs.rutgers.edu/~murdocca/

- http://ece-www.colorado.edu/faculty/heuring.html

- Mostafa A. E.B and Hesham E. R, (2005). Fundamentals of Computer Organization and Architecture. Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

- NOUN, (2008). Introduction to Computer Organisation. CIT 246 Course Material, National Open University of Nigeria, Headquarters 14/16 Ahmadu Bello Way, Victoria Island,Lagos. First Printed 2008

- Stallings William. *Computer Organisation and Architecture* (3rd ed). Maxwell Macmillan International Editions.

- Tanenbaum, Andrew S. (1993). *Structural Computer Organisation* (3<sup>rd</sup> ed) Prentice Hall of India.

http://websrv.cs.fsu.edu/~tyson/CDA5155/refs.html

http://www.cs.ucsd.edu/classes/wi99/cse141\_B/lectures.html

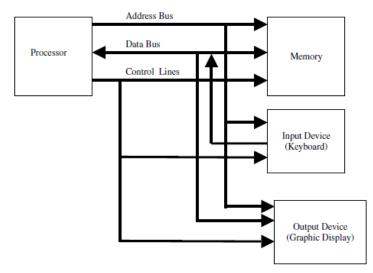

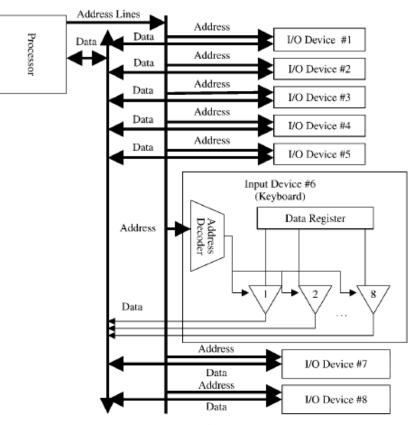

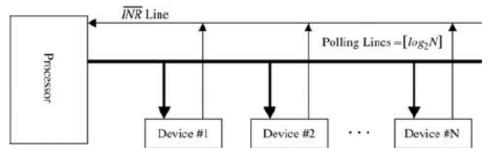

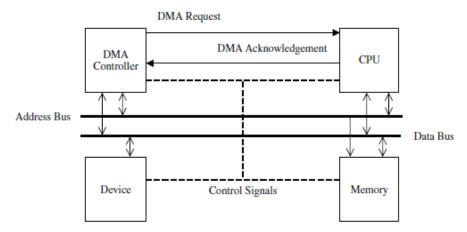

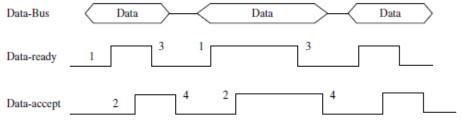

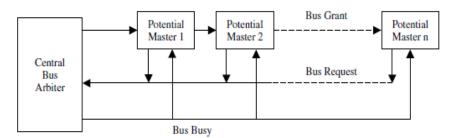

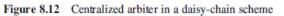

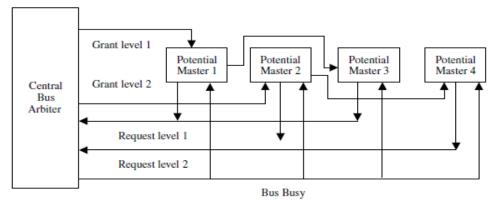

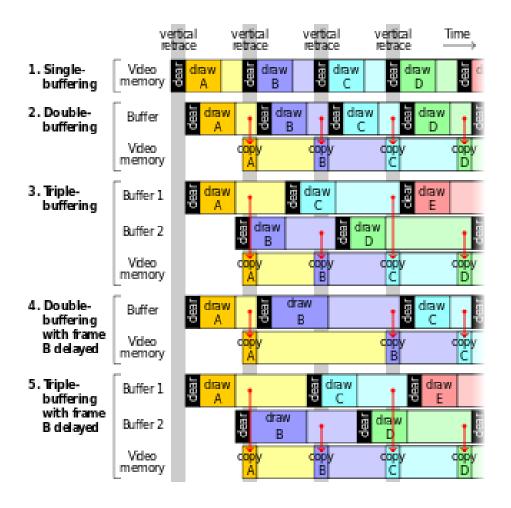

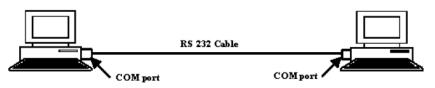

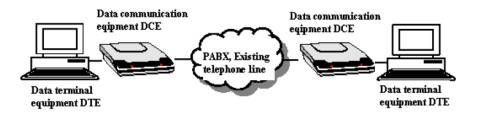

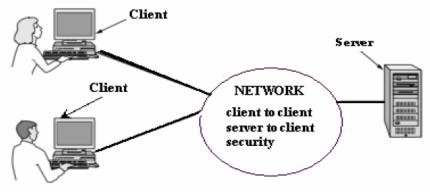

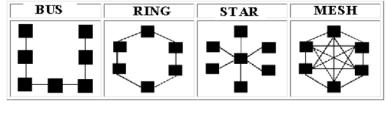

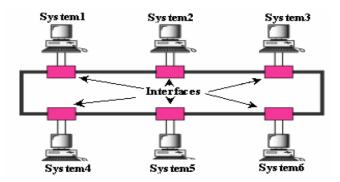

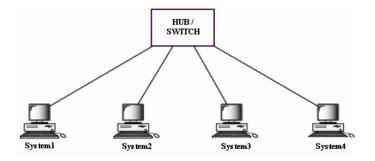

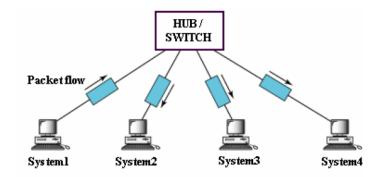

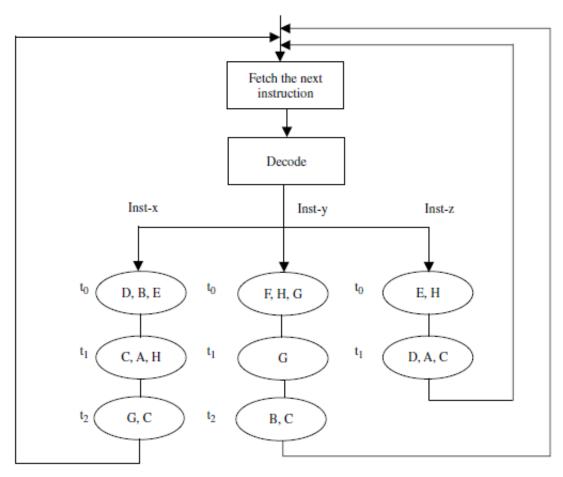

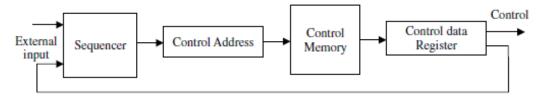

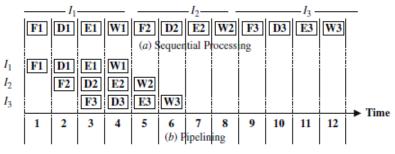

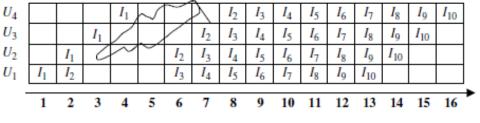

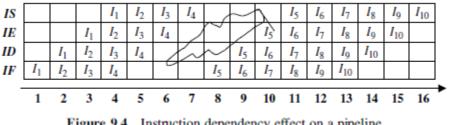

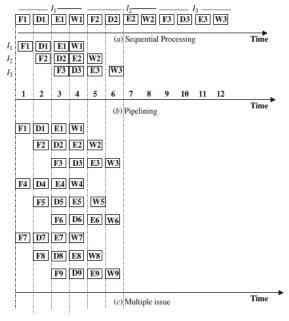

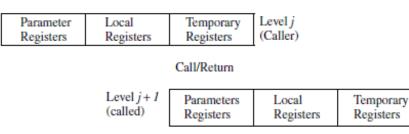

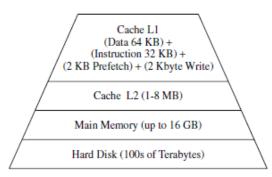

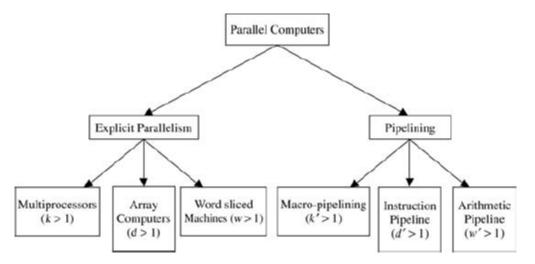

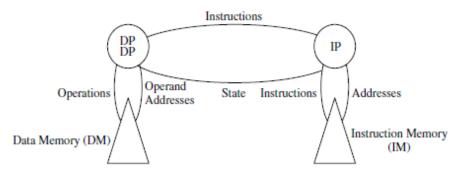

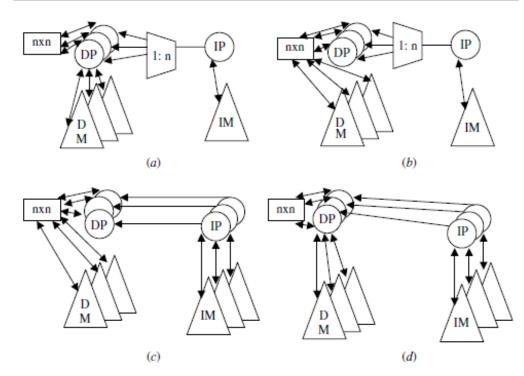

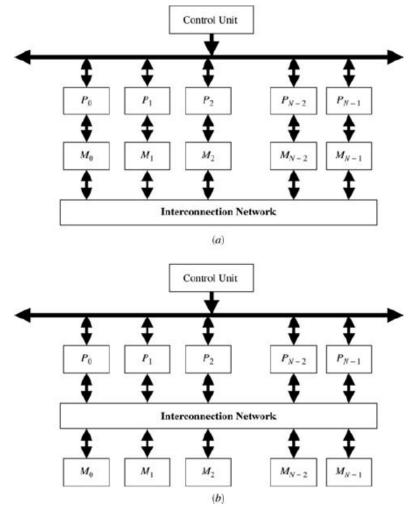

http://www.cs.caltech.edu/courses/cs184/ winter2001/slides/day5\_2up.pdf